- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种基于开关逻辑结构的低功耗SAR ADC的设计

摘要:设计并实现了一款10 位逐次逼近型模数转换器,该电路采用了改进型开关逻辑结构降低了开关的动作频率,提高了数模转换器的线性度,同时降低了模数转换器的功耗。仿真结果表明,该模数转换器在Chartered 0.35 μm2P4M工艺下实现了10 位精度,转换速率为250 kHz,信噪比大于60 dB,功耗小于2 mW.流片后测试结果显示芯片达到设计指标要求,平均功耗为1.97 mW。

逐次逼近型模数转换器(successive approximatiONregiSTer analog-to-digital converter,SAR ADC)是应用于采样速率低于5,MHz 的中高分辨率的常见结构,其分辨率一般为8~16 位,因制造工艺与现代数字CMOS 工艺的兼容性好,且易于在较低的工艺成本下实现,所以广泛应用于现代超大规模集成电路与片上系统(system-on-chip,SOC),如便携式/电池供电仪表、笔输入量化器、工业控制和数据/信号采集器等。

笔者设计了一款10位低功耗SAR ADC,采用温度计码控制的开关逻辑结构代替传统的开关阵列控制数模(digital-to-analog,D/A)转换器的动作,从而提高了D/A 转换器的线性度并降低了ADC 的功耗。ADC 在 250,kHz 的采样速度下实现了10 位的模数转换功能,功耗小于2,mW。

1 SAR ADC的结构和工作原理传统SAR ADC 的结构主要包括5 个部分,分别是:采样保持电路、模拟比较器、D/A 转换器、逐次逼近寄存器和逻辑控制单元。在很多实际电路中,采样保持与D/A 转换器合二为一。

SAR ADC 通过比较器对D/A 转换器产生的参考电压和采样所得的模拟输入电压进行比较,由逐次逼近寄存器逐次地决定每一位数字码,直到完成最低有效位(least significant bit,LSB)的转换。SAR ADC采用二进制搜索算法来决定模数转化过程中的数字码值,N 位的SAR ADC需要进行N 步的转化。

在SAR ADC 中,数字模块消耗的功耗较小,整个SAR ADC的功耗主要集中在3 个方面。

(1)对采样保持电容的充放电。

(2)对D/A转换器中二进制加权电容的充放电。

(3)模数转换过程中比较器所消耗的功耗。

有关降低SAR ADC 功耗的文献通常针对以上3个方面来提出电路结构的改进方案,如在数模转换器中采用特殊结构的电容阵列以及采用功耗较低的动态比较器等。

为了降低ADC 的整体功耗,笔者设计的D/A 转换器采用了电荷分配型的结构。与其他同类型ADC的最大区别在于用温度计码的开关逻辑结构代替了常用的二进制码开关来控制D/A 转换器,从而合理优化了电容阵列的开关逻辑结构,减小了开关的动作频率,既提高了D/A 转换器的分辨率和线性度,同时又降低了整个系统的功耗。

2 基于开关逻辑结构的D/A转换器2.1 D/A转换器的基本原理

传统型电荷分配型D/A 转换器通常由一个二进制加权电容阵列、一个与LSB 等值的电容和开关阵列组成,其转换过程可以分为3 个阶段。

(1)采样阶段:此时,所有电容的上极板接地,下极板接输入电压,这样,上极板存储了与输入电压成正比的电荷,这些电荷在D/A 转换器的转换过程中保持不变。

(2)保持阶段:此阶段,二进制加权电容的上极板接地开关断开,下极板接地,引起电容阵列上极板的参考电压的变化。

(3)再分配阶段:此时,逐次逼近寄存器的最高位被置为1,即最大的电容2N-1C 的下极板连接到基准电压Vref,在下一个时钟周期来临时,最大的电容的下极板的连接状态是由比较器的比较结果决定的。同时次大的电容的下极板连接到基准电压Vref.这个过程将会进行N 次,在每一个时钟周期内比较器的比较结果决定了原先被试探的电容的下极板接地或是接基准电压Vref,同时将比试探电容小一半的那个电容设为试探电容,直到整个转换过程完成,即最小电容的下极板状态被决定。

2.2 D/A转换器的低功耗设计

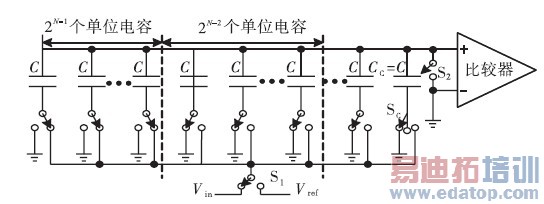

所设计的开关逻辑结构的D/A 转换器如图1 所示,其与传统型D/A 的区别是将二进制加权电容阵列进行了分拆并加入了码制转换电路。码制转换电路将逻辑控制单元控制的寄存器的输出二进制码转化成为温度计码,以温度计码来控制整个二进制加权电容阵列,以降低开关动作频率。

图1 D/A转换器

以3 位D/A 转换器为例来简要说明。图2(a)为三位的二进制码到温度计码的编码转换图;图2(b)为二进制码对应单位开关输入码图。由图2 可知,一旦比较器的输出为0,即在模数转换过程中出现输入信号比D/A 转换器所产生的参考电压小的情况,采用温度计码的开关逻辑结构对减小开关动作频率是有利的。将二进制码转换为温度计码只需通过一个简单的编码转换电路就可以实现。

图2 码制转换示意

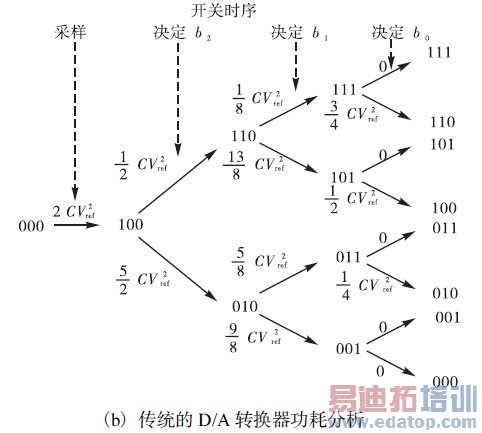

2.3 D/A转换器的功耗分析

对于电容阵列中的电容,只有当其下极板连接到Vref 时,因充电产生功耗。设电容阵列的建立时间为T,则电容从Vref获得的能量为:

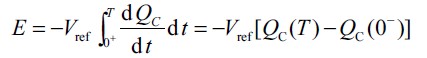

由于电容两端的电压不能突变,故QC(0+)= QC(0-),且 iref(t) = -dQC/ dt ,故:

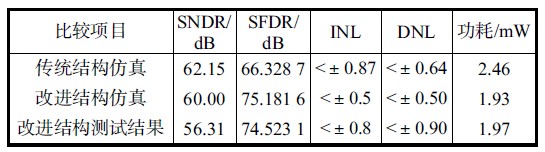

所以,可以计算每一次开关动作时D/A 的功耗。为了减少计算量,仍以3 位D/A 转换器为例,对两种D/A 转换器的功耗进行比较,如图3 所示,箭头旁边的数字为每一次开关动作时消耗的能量。图3显示当比较器比较的结果为0 时,采用的结构所消耗的功耗小于传统的结构。显然,所设计的D/A 转换器的平均功耗远小于传统的D/A 转换器。随着ADC 位数的增加,这种平均功耗的降低效应将会更加显着。10 位SAR ADC和传统结构的SAR ADC功耗对比如表1 所示,数据表明改进的SAR ADC 相对于传统结构下降了21.5%。

图3 改进的和传统的D/A功耗分析

表1 SAR ADC测试结果

3 电路仿真与芯片测试

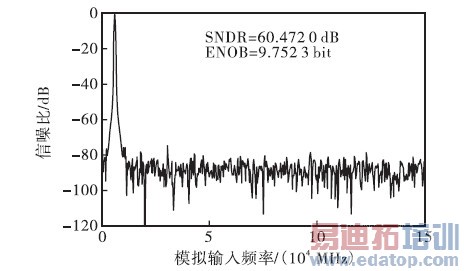

利用Cadence AMS作为仿真工具,对SAR ADC进行了功能仿真,采用FFT 法分析ADC 的动态性能,得到的频谱图如图4 所示。仿真所得信噪失真比(SNDR)为60.472,dB.

图4 电路仿真的FFT频谱

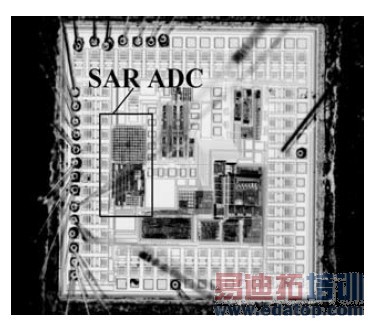

基于Chartered 0.35,μm,2P4M 工艺,完成了电路的版图设计,其中单位电容均采用工艺偏差相对较小的poly-poly 电容。图5 给出了经MPW 流片SARADC 芯片图。由于电路的非线性与电路的元件匹配有关,其匹配性越好,其线性度越高,因此版图设计中采用了一系列手段以提高电容阵列的匹配性,包括采用"共质心"结构布置版图,降低因芯片面积加大带来的氧化层梯度的影响;电容阵列周边采用"虚拟"结构;单位电容采用固定的周长/面积比等。对比表1中的无失真动态范围参数,可以看出线性度提高了11.78%.

图5 SAR ADC芯片

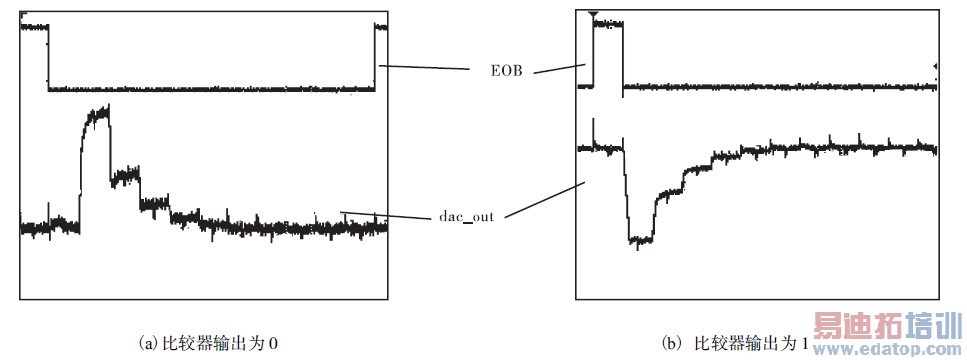

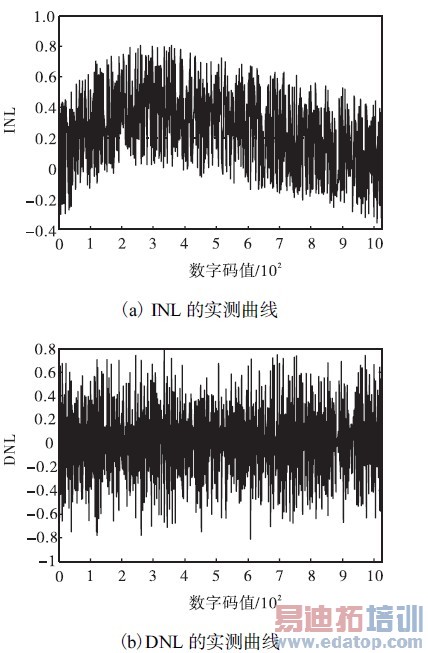

使用TeKtronix TLA5204B 逻辑分析仪和TDS3052B 示波器等工具对MPW 流片回来的芯片进行了测试。图6 给出了D/A 的测试结果,其中EOB 为转换结束信号,dac_out 为D/A 输出信号;SAR ADC在250,kHz 的转换速率下的实测积分非线性(Integralnonlinearity,INL)误差和微分非线性(differnetialnonlinearity,DNL)误差特性曲线[14]如图7 所示。

图6 D/A的测试结果

图7 SAR ADC的INL和DNL的实测曲线

表1 显示了10 位SAR ADC 的整体性能。比较流片后测试结果和仿真结果可见所设计的SAR ADC较好地达到了低功耗的设计要求,性能良好。

4 结 语

完成了一款基于开关逻辑结构的SAR ADC 设计。其中的D/A 转换器由温度计码的开关逻辑结构来控制,从而减小了开关的动作频率,降低了整个系统的功耗。测试结果显示,设计的SAR ADC 实现了10 位模数转换功能,转换速率为250 kHz,INL 和DNL 均小于1 个LSB,功耗小于2 mW,表明该电路较好地达到了设计要求。

作者:赵毅强 耿俊峰 郑淑凤 高静 来源:《天津大学学报》