- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于SoPC的实时视频处理与显示设计

摘要:介绍了一种采用SoPC技术,适用于光照度不够均匀造成图像灰度过于集中环境下的视频处理与显示设计。该系统基于FPGA技术,通过将NiosⅡ软核处理器、用户自定义逻辑模块、存储器、I/O等集成到单块低成本的FPGA上,实现对解码芯片SAA7113H的初始化及配置、视频图像灰度信号直方图统计以及灰度均衡化的实时处理与显示。其设计灵活、可靠性高,并且降低了成本和功耗。

当前基于软核处理器的图像系统已成为研究的热点,使用FPGA来构建基于片上可编程系统(SoPC)的图像处理系统,已成为一种趋势[1]。因此,本文采用SoPC技术,在Altera公司单片Cyclone系列FPGA上使用IP资源复用技术集成了NiosII软核处理器及各种输入输出接口,完成了对视频图像的采集、预处理、存储和显示几大功能。本系统对图像进行了灰度均衡化处理,使系统应用更广。由于直方图均衡能直接从已知的图像中提取信息,不需要额外的参数说明,所以在军用、航空、商业等领域,特别是红外图像增强领域[2]有实际的意义。SoPC是Altera公司提出来的一种灵活、高效的柔性设计,不需要修改硬件[3],就可方便地扩展和修改嵌入式视频采集功能。同时,由于融入众多的IP核,保证了设计的高效、快速。

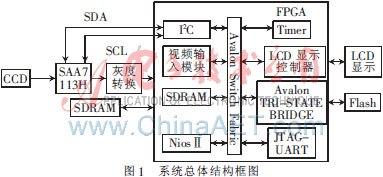

1 系统总体结构及工作原理

系统框图如图1所示。系统上电后,Nios II软核中的I2C控制总线对视频采集模块SAA7113H进行配置,FPGA依靠像素时钟和行、场信号同步采集SAA7113H芯片输出的视频信号中的灰度视频数据,把采集到的灰度数据进行灰度直方图统计和灰度分布均衡化处理。Nios II软核外部加一个延迟模块,与灰度转换模块输出的信号同步之后,视频输入模块开始工作,通过存储控制、DMA控制器传输视频信号,LCD显示控制等模块显示所采集的信号。所有处理都采用流水线操作,大大节省了系统的处理时间。

2 系统硬件设计

2.1 视频解码芯片SAA7113H初始化

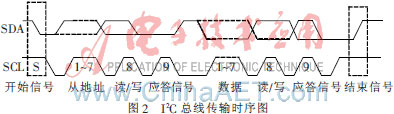

本系统中视频解码器的初始化配置由Nios II软核处理器通过I2C总线完成,主要包括对视频解码器的工作模式,输出行、场同步参考信号的时序关系以及输出数字信号的格式等进行设置。I2C总线是由Philips公司开发的一种两线制总线,由一条串行数据线SDA和一条串行时钟线SCL组成,可以实现数据通信,完成芯片配置。首先,I2C总线控制器发出一个数据传输的起始条件:SCL信号保持高电平、而SDA信号由高电平变为低电平时,开始传输地址数据流。起始条件满足后,发出一个8bit的设备从地址,所有的外围设备开始响应起始条件并转换下一个8bit寄存器地址(7bit地址+1bit读写位),由高位到低位依次传输。外围设备识别出传输地址后,在第9个时钟脉冲(确认位)把数据线变为低电平,然后开始将8bit数据写入或者读出寄存器(读写位决定了数据的传输方向)。当时钟线SCLK为高电平、而数据线SDA由低电平变为高电平时,表示一次数据传输完成,停止I2C总线,等待下一次的传输开始。图2为I2C总线的数据传输时序图。

从SAA7113H的4个模拟输入端AI11、AI12、AI21、AI22输入的视频图像信号,经A/D转换后产生数字色度信号和亮度信号,分别进行亮度信号处理和色度信号处理。亮度信号处理的结果送到色度信号处理器,进行综合处理,产生YUV信号,经格式转化后从VPO(8位)输出。所有这些功能均是在I2C总线控制下完成。SAA7113的寄存器配置通过I2C总线来进行,遵从I2C总线协议。表1是SAA7113H寄存器的"写"操作格式。

![]()

其中,S为起始位,条件是SCL为高电平、SDA有下降沿、ACK-s为从动设备应答位,P为终止位。在初始化过程中要注意:SAA7113H的节点地址(Slave Address)上电、RTS0为高电平时,其I2C写地址为48H,读地址为49H;RTS0为低电平时,其I2C写地址为4AH,读地址为4BH。

2.2 灰度直方图统计及其均衡化

通过输入系统获取的图像信息中含有各种各样的噪声与畸变,例如,光照度不够均匀会造成图像灰度过于集中,由CCD获得的图像经过A/D转换、线路传送都会产生噪声污染等,不可避免地会影响系统图像的清晰程度,降低图像质量。但通过图像增强可以改善图像质量。直方图均衡化算法是空域图像增强技术的重要算法,是图像压缩、图像分割和图像识别等后续图像处理的基础[2,4],在图像预处理技术中有广泛的应用。

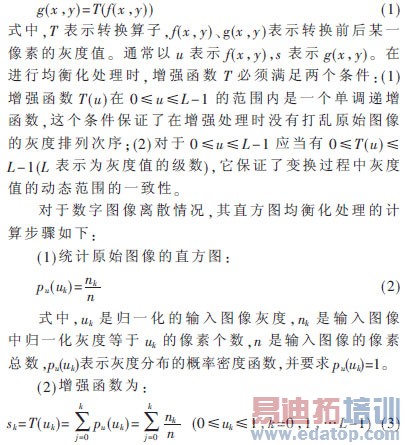

2.2.1 直方图均衡化原理

直方图均衡是以概率论为基础,运用灰度点运算来实现直方图变换。原始图像的直方图包含了丰富的图像信息,描述了图像的灰度级内容,反映了图像的灰度分布情况。直方图统计及均衡化的基本思想是对在图像中像素个数多的灰度级进行展宽,而对像素个数少的灰度级进行缩减,从而达到清晰图像的目的[5]。通过点运算使输入图像转换为在每一灰度级上都有相同的像素点的数目。在图像增强处理中运用如下公式:

(3)用累积分布函数作变换函数进行图像灰度变换。

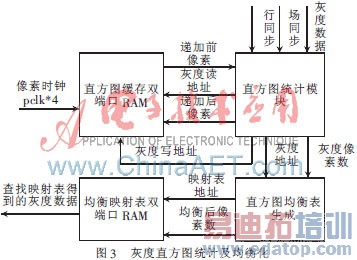

2.2.2 基于FPGA的算法优化及实现

算法的关键是在FPGA中实现直方图统计和均衡后的映射关系表,本设计采用FPGA器件提供的Block RAM来存放直方图和均衡后映射关系表。以双端口RAM的数组结构为核心,把整个算法分为两个部分执行:(1)统计原始图像的各级灰度值,并存入灰度计数表RAM中;(2)对得到的灰度值做灰度映射,把映射后的结果存入到映射表RAM中,即生成均衡映射表。根据映射表就可以知道原始图像某一灰度级经过变换后的灰度级。经过这样的处理,就可以把原始图像中密集分布的灰度值映射到经过直方图均衡化后的新的灰度级上。图3为该算法的逻辑框图。

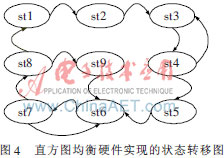

考虑到FPGA的硬件特点,在接收图像数据、计算此场的直方图时,在FPGA内实现浮点型数据运算相对复杂且消耗较多逻辑资源,因此在对图像进行直方图统计时将各灰度级像素点的个数作为直方图数据:pu(uk)=nk,以避免使用浮点型数据运算。对直方图进行均衡化处理,得到原灰度到均衡化后灰度映射关系表。本设计中的直方图均衡化的算法具体的状态转移图如图4所示。其具体的转移条件:启动信号有效时,由st1转向st2;当计数器1计数到255时,跳转到st3;当计数器1没有计数到图像高度减1或者计数器2没有计数到图像宽度减1时,跳转到st3;当计数器1计数到图像高度减1且计数器2计数到图像宽度减1时,跳转到st5;当计数器1没有计数到255时,跳转到st6;当计数器计数到255时,跳转到st7;当计数器1计数到图像高度减1且计数器2计数到图像宽度减1时,跳转到st1状态;当计数器1没有计数到图像高度减1或者计数器2没有计数到图像宽度减1时,跳转到st6。在进行计数统计时,计数器在检测得到一个像素点的灰度之后,不仅要相应地将计数器加1,而且对应灰度值大于当前灰度值的所有计数器都加1,这样就能同时完成原始图像各像素灰度值的统计和累积,减少了统计时间。

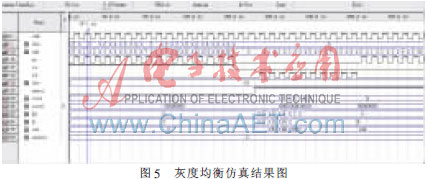

因为在灰度均衡处理过程中是以场为单位进行的,在灰度均衡化处理完之后,要将场合并为帧。其操作是由Nios II软核中的SDRAM控制器来完成奇偶场的合并。灰度均衡化的仿真结果图如图5所示。

3 视频输入模块

视频输入模块的结构示意图如图6所示。经过灰度变换YcrCb4:2:2格式视频信号在像素时钟控制下输入FIFO缓冲器。彩条测试信号模块在系统测试时,给出一个非常简单的测试信号,可以模拟为信号源,以方便系统的调试。色度转换模块将YCrCb格式转换为RGB格式,并把其值写到FIFO缓冲器中。Avalon DMA把图像数据写到系统存储器(SDRAM)中,当完成一帧图像需写操作时,给Nios II处理器一个中断信号。

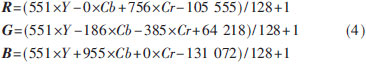

在色度空间的转换模块中,采用FPGA片内的资源,利用MegaCore构造一个乘加器件完成运算。根据转换矩阵中YUV的比例关系,将信号放大一定的倍数,使其接近一个整数值。YUV信号的最大值为255,但是10bit DATA可以接收1 023亮度等级的调节,所以这个比例可以放大4倍左右(如果超出1023就按1023的等级计算)。根据反复实验最后得出,按照如下的运算规则最接近转换矩阵:

4 Nios II系统的生成

用SoPC Builder可以进行系统模块硬件设计和底层软件生成。进行硬件模块设计时,SoPC Builder提供了图形化配置界面,备有一些常用外设的IP模块,如SDRAM、Flash RAM、UART、Interval timer、Parallel I/O等。Nios II软核所含的组件如图7所示。

在SoPC Builder自带的IP核库中并没有I2C配置模块、视频输入模块和LCD controller模块的IP核,这些模块是根据寄存器特点以及功能要求自行设计的,并以IP核的形式通过Avalon总线连接到SoPC系统上。在建立了基于Nios II处理器的SoPC系统后,需要进行一些系统设置才能生成最终的Nios II系统。因此,系统配置除了对外设设置外,还包括启动程序、中断向量表、系统启动地址等的设置。

本文介绍了基于SoPC技术的视频采集方案以及对视频信号进行灰度直方图统计及灰度均衡化的实现。该方案结合SoPC技术在软硬件可裁剪、可升级、可扩充等优点,大大缩短了系统整体设计周期,有很好的应用前景和科研价值。

参考文献

[1] 王刚,张潋.基于FPGA的SoPC嵌入式系统设计与典型实例[M].北京:电子工业出版社,2009.

[2] 刘延,任永杰,李群伟,等.基于FPGA的直方图均衡实时并行算法及新架构实现[J].红外技术,2010(3).

[3] 李兰英.NiosII嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[4] 唐崇武,李会方,何俊婷,等.改进的直方图均衡图像增强算法及实现[J].信息安全与通信保密,2009(12).

[5] 鲁恒.基于FPGA的实时图像直方图均衡增强设计[J].电子应用技术,2006,32(11).