- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于Altera ASI IP核的ASI发送卡实现

1.ASI 接口的应用意义

随着数字电视技术的迅速发展,在电视节目的制作设计方面己经有很大一部分实现了数 字处理。在节目的传输方面,我们从卫星上己可以接收到多套数字压缩编码的节目。这种传 输方式,不但保证了节目的高清晰质量,也大大降低了电视节目传输、发送、接收的成本。 而大量的收发设备,采用的是ASI 的接口标准,设计实现基于PC 机和ASI 接口标准的电视 节目传输流的收发设备,在节目的制作、保存和重播等方面有大量的应用。

随着广播电视数字化的开展,有线电视的数字化进程越来越快。数字化技术提高了广播 电视节目的技术质量、节目质量,提供了广播电视和综合数据业务的多媒体服务手段,拓宽 了广播电视业务。数字化以后的电视信号传输,采用MPEG-2 视频编码标准,可以以4~ 5Mbit/s 的带宽传送高清晰度的电视节目,噪声没有积累,大大提高了传输质量,有很广阔 的应用前景。在目前的数字通信系统中,有两种MPEG-2 接口标准:ASI 异步串行接口和SPI 同步并行接口。其中SPI 接口一共有11 位有用信号,每位信号差分成两路用来提高传输抗 干扰性,在物理链接上用DB25 传输。由于其处理简单且扩展性强,MPEG-2 编解码器及视频测试设备的输入、输出一般都采用SPI 接口。但是由于其连线多且复杂,所以SPI 接口只能 用于短距离传输。ASI(异步串行接口)只需要一根电缆就可实现270Mbit/s 的透明传输,所以 应用十分普遍。ASI 接口具有高速、可靠、固定波特率和传输距离远等优点,而且连接简单 成本低,可以广泛应用于各种高速点到点的传输,尤其是视频传输设备。

2.ASI 协议结构

ASI 可以有不同的数据接收速率,但是传输速率是恒定的,为270Mbit/s。因此ASI 可以发送和接收不同速率的MPEG-2 数据。ASI 采用分层结构,分为三层:物理层、数据编码层和传送规则层。

第零层是物理层。物理层定义了传输介质、驱动器和接收器以及传输速率。物理接口提 供了LED 驱动的多模光纤和同轴电缆。基本速率被定义为270Mbps。在同轴电缆的应用中, 以随机及与数据有关的抖动和占空系数失真的传统方式,规定了允许抖动的最大值。

第一层是数据编码层。采用 DC 平衡的8B/10B 传输码。这种码把每一个 8bit 数据字节 变换成具有下列特性的l0bit 码字:游程长度等于或小于4bit; DC 编制最小。这种码通过无效 传输码点和"运行"的不等性来提供差错校验。作为超出对数据字节进行编码需要的额外 码点,规定了专用字符。特别是逗号这个字符(在8B/10B 传输码规则中定义为K28.5 专用字 符),用来在DVB-ASI传输链路中建立字节对齐。在发送端对字节进行8B/10B 编码,对出 现的每一个8bit 字节产生一个10bit 的码字,使这些10bit 码字通过以固定输出比特率270 Mbps 工作的并/串转换。如果并/串转换器请求输入一个新码字,但是数据源还没有准备好 新码字,就应该插入同步字 (或者称为逗号字符K28.5)。在传输数据的空余字段插入同步 字符,可以使传输码子具有较强的抗扰,错误检测和在同步能力。

第二层是传送规则层。ASI 传输的第2 层标准使用MPEG-2 传输流包(TS)作为基本的信 息单元。传输包可以通过 3 种方式传输:一种是以块状的连续字节传输,也就是说,在一个 单独数据包的传输流中不用插入同步字节;第二种方式是以单独的字节方式传输,在这种方 式中要插入同步字节;第三种方式是连续字节和同步字节相结合。此外,ASI 的第二层协议 规定,在每个传输包之前至少要有两个同步字 (K28.5 )。尽管数据包同步过程不是 ASI 传 输协议定义的内容,MPEG-2 传输包同步字节 (47H)被包括到第 2 层的包定义中,这样接收 设备就可以实现包同步。ASI 接口的第2 层定义使用MPEG-2 传输流的语法,只是增加了在 每个传输包前需要有至少两个K28.5 同步字符这个额外要求。只要最初是同步的,8B/10B 接收装置一般能够维持同步,不需要增加同步字符。但是当线路干扰等外界因素使同步丢失 时,增加的同步字节可以使一个传输包重新同步。传输包结构应该遵循EN/ISO/IEC 13818-1 和ETS 300 429 对传输流包的规定。包长度可以是 188 个字节或者204 个字节。传输包可 以通过两种方式出现在第 2 层。第一种每个TS 包中的188 字节是连续的,分为分组头部、 调整字段和有效负载三个部分。其中调整字段是可选的,并不是所有的传送流分组中都出现 调整字段。同步字符插在两个包中间,称为突发模式。用突发模式实现TS 流的传输,具有 动态分配的灵活性、可分级性、可扩展性、较强的抗千扰性等有点;第二种是同步字随机均 匀的插在TS 数据之间,称为非突发模式。

3.设计实现

3.1 ASI 发送卡硬件设计

大部分ASI 编码的实现,都是采用Cypress 公司的CY7B923 实现并行数据到串行数据的 转换。CY7B923 主要实现码字的8/10bit 转换、插入同步字K28.5 和并/串变换。ASI 的传输 速率恒定为270MHz,而输入MPEG-2 TS 码率是不同的,所以要用FIFO 实现速率匹配,需 要对输入的SPI 数据、FIFO 和CY7B923 之间的通信进行逻辑控制。综合性能、价格和程序 复杂度的考虑,本方案采用FPGA,用Verilog 编程来实现它们之间的逻辑控制;采用Altera 公司的ASI IP 核,代替Cypress 公司的CY7B923 来实现ASI 数据的编码。ASI IP 核具有使 用方便、成本低等优点。

在ASI 的编码过程中,只需将MPEG-2 编码的TS 码流的8 位数据和一位TS 码率传输时 钟输入到FPGA 中,本方案是PCI 33M 的时钟信号。因为在本方案中,TS 格式为188 个字节 的突发模式发送数据,根据数据有效信号DVALID,FPGA 检测这个信号来判断什么时间内是 有效数据,来接收TS 码流数据,而不用关心TS 码流的同步头。FPGA 将接收到的数据以TS 码率时钟写入FIFO。当FIFO 半满时,FPGA 接收到FIFO 的半满信号,然后FPGA 给ASI 核发出FIFO 可读信号,ASI 核以27Mbps 读取FIFO 中的数据;当FPGA 计数到ASI 核读取了一定数量的FIFO 数据,FPGA 则向ASI IP 核发送FIFO 不可读信号,防止FIFO 读空。MPEG-2 传 输码率的并行最大速度为132Mbps,而读FIFO 速率为27Mbps,因此FIFO 会有溢出。因此在发送MPEG-2 传输流时,有驱动程序控制一次发送数据的多少。考虑到延时,本方案在FPGA 内部烧制了一个2K 大小的异步FIFO。ASI IP 核在FIFO 中数据不可读时,向ASI 码流中填 充K28.5 以维持270Mbps 的固定传输速率。最后串行数据经过驱动就可用同轴电缆传送出去。 本方案中,同步字K28.5 的插入采用传输码流的单个字节前后不能都是K28.5 同步字的方式。

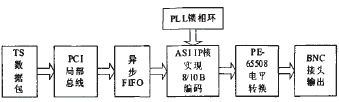

ASI 发送卡的硬件实现框图如下:

该系统是基于 ALTERA 公司的FPGA 芯片,Cyclone Ⅱ EP2C8Q208 设计的。经过编码的并行数据流经过PCI 总线送入异步FIFO。异步FIFO 主要实现数据缓存和时钟匹配的作用。 系统进行DMA 操作,把数据送入板卡。FIFO 将这些数据缓存,以避免数据丢失。又由于时 钟有PCI 33M 的时钟信号和27M 的ASI 输入时钟信号。这就要求把这两个不同频率的时钟同 步。FIFO 在两个不同的时钟下工作,数据的输入和输出分别使用不同的时钟。这就实现了 时钟的隔离和无缝连接。FIFO 采用32 位输入、8 位输出,分别与PCI 的数据宽度和ASI IP 核的输入数据宽度相一致。ASI IP 核实现8 位数据到10 位的编码。其中ASI IP 核的参考 时钟为27M,输出时钟是270M。采用外部锁相环,27MHz 时钟频率有晶振产生,通过锁相环 产生270M 的时钟,用于ASI 接口的数据输出。PE65508 实现耦合和阻抗匹配,最终经BNC 插头发送出去。

3.2 ASI IP 核的生成

ASI 编码的实现采用Quartus 6.1 直接生成,进行仿真验证。

ASI 接口的生成。IP 核首先需要安装,可以从Altera 网站上下载。安装之后,打开 Quartus 6.1 新建工程之后,点击tools 菜单里面的Megawizard plug-in Maneger,选择 创建一个新的宏函数变量,按步骤一步步生成asi 文件。可以选择器件和生成文件语言,分 别选择Cyclone Ⅱ和verilog 语言。需要注意的是生成的文件名要与工程的顶层文件名相 一致。选择Transmitter,这里作为发送接口。在ASI 中根据所选器件速度的快慢,可以选 择是否生成锁相环。这里采用外部锁相环,用于产生270MHz 的输出频率。

生成的ASI 接口verilog 部分代码如下:

module asi ( rst, tx_refclk, tx_data, tx_en, tx_clk270, asi_tx);

input rst,tx_refclk,tx_en,tx_clk270,asi_tx;

input [7:0] tx_data;

asi_megacore_top asi_megacore_top_inst( .rst(rst), .tx_refclk(tx_refclk), .tx_data(tx_data),

.tx_en(tx_en), .tx_clk270(tx_clk270), .asi_tx(asi_tx));

……

endmodule

该接口实现8 位数据到10 位数据的编码。在8 位的MPEG-2 数据从输入端输入,流入内 部FIFO 中。tx_data 8 位并行数据输入接口,实现数据编码,即把每个8 位的数据变为10 位的数据;然后串行器把10 位并行数据转换为串行数据。asi_tx 经编码后的串行数据输入 接口。若MPEG-2 的TS 流的传输率小于270Mbps 时,则需要插入同步字符以保障输出端稳定 的270Mbps。tx_refclk 为输入的27M 参考时钟,tx_clk270 为270M 的数据输出时钟。它们是通过外部锁相环得到的。rst 是复位信号,高电平是有效电平,使整个设计停止工作。tx_en 数据输入使能信号,控制FIFO 中待编码的数据进入ASI IP 核实现数据编码和并串转换。

3.3 ASI 工程及仿真波形

把生成的ASI 核添加的自己的工程中,顶层部分代码如下:

module FIFO_ASI(clk27,data,t_out);

input clk27;

output data,t_out

wire clk13,clk270;

wire[31:0] data32;

wire[7:0] data8;

……

endmodule

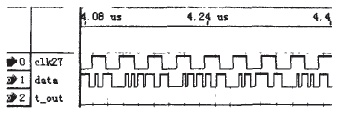

对其进行仿真,波形如下:

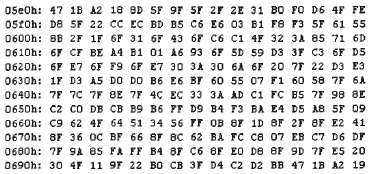

外部接 27M 的时钟,连接到clk27,做为ASI IP 核27M 的输入参考时钟。t_out 为一个 时钟输出信号,对27M 分频,作为指示灯信号,来监测程序是否下载到FPAG 中。在指示灯正常闪烁情况下,表明程序已经下到芯片中,并且能够工作。经过ASI IP 核编码的ASI 数 据由data 输入。在本工程中,通过一电脑不断地发送TS 流给板卡,经过ASI 编码后通过 ASI 接口输出。在接收端,通过一个ASI 接收卡,读出接收的数据,可以看出ASI 工作正常。 在发送TS 流时采突发模式,其读出的数据如下:

在调试阶段,PC 机连续发送相同的MPEG-2 编码的TS 包。在接收到的数据中,可以看到连 续的MPEG-2 编码的TS 包,且与发送的数据相同。其中TS 包的接收采用一块ASI 接收卡作 为接收端,通过USB 接口输入到电脑里,用相应的软件读取数据后显示。

4.应用意义

本文设计的基于Altera 公司的ASI IP 核实现的DVB-ASI 卡,实现了ASI 数据的正确编 码和发送。用FPGA 实现逻辑控制和数据缓存,可以方便的实现系统升级,实现多个ASI 数 据的发送。与用Cypress 公司的CY7B923 实现的ASI 的发送卡相比,本卡更适合批量生产,可以节约成本,提高了市场竟争力,具有很好的市场前景。

本文作者创新观点是用Altera 公司的ASI IP 核代替Cypress 公司的CY7B923 专用ASI 发送芯片,实现ASI 数据的稳定发送。本方案降低了成本,设计灵活,并且方便升级到多路ASI 数据发送。

来源:21IC电子网