- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

无线电台中DS/D-MPSK调制解调器的FPGA实现

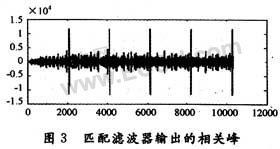

将数字匹配滤波器输出的相关峰延时一个基带数据的码元宽度,即NTc之后,与当前相关值峰相乘得:

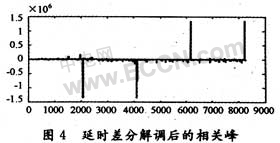

由此可见,延时相乘刚好实现了解调和解差分。图4是Verilog代码仿真得到的延时差分解调后的相关峰,负相关峰表示'1',正相关峰表示'0'。

为了提高抗干扰能力,可以把I,Q两路的相关值累加求和后再进行判决。经过判决,就可以恢复出基带数据和时钟。

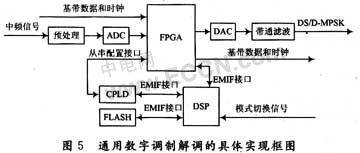

3 DS/D-MPSK通用数宇调制和解扩解调器的具体实现方案

本方案已经应用于某军用数字超短波电台中,其具体的实现框图如图5所示。

其中,FPGA选用的是Xilinx公司的XC2VP20,200万门的高端产品,标称频率为400 MHz。NCO的时钟频率较高,达到160~240 MHz。DSP选用的是TI公司的TMS320VC5510,FLASH选用的是Spansion公司的S29GL128N,16 MB的容量,存放DS/D-BPSK,DS/D-QPSK和DS/D-8PSK等多种模式的FPGA配置文件。CPLD选用的是Xilinx公司的XC9572XL。DSP主要完成对FLASH的读写工作,并且根据模式切换信号,配合CPLD完成对FPGA的动态配置。

4实际测试结果

图6是在中频20.48 MHz上通过Agilent 89600矢量信号分析仪测到的DS/D-QPSK信号的星座图、眼图、频谱图和统计数据,其频差为1.8 Hz,相差为876毫度,I,Q平衡度为-20 dB。图7是中频为21.76 MHz的DS/D-8PSK信号混频到280 MHz经声表面波滤波器后测到的星座图、眼图、频谱图和统计数据,其频差为-0.75 Hz,相差为3°,I,Q平衡度为-21 dB。

5结语

从以上的测试结果可以看出,本文提出的DS/D-MPSK通用数字调制和解扩解调器在实际应用中取得了良好的效果,证明了本方案是正确的、可行的和稳定可靠的。

作者:谭进,陈 勇,查光明(电子科技大学 四川 成都 610054)

来源:《现代电子技术》

上一篇:基于DSP的脱机视频编/解码系统

下一篇:华为FTTx-ODN解决方案