- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于STB7100的高清IPTV机顶盒设计

1 引言

IPTV利用计算机或机顶盒+电视作为接收终端,完成的业务包括电视直播、视频点播、时移电视、网络浏览、信息服务、互动游戏,以及未来可扩充的业务[1]。随着宽带用户的增多,以影视服务为主的宽带流媒体服务成为宽带增值业务中的重要服务。与此同时,人们对高质量高清晰影音服务的需求使得高清发展成为必然趋势。因此,高清与IVI'V的结合必将成为当前宽带网络上最具发展潜力、最具盈利前景的热点宽带增值应用之一。

2 IPTV机顶盒总体设计

根据高清IPTV机顶盒所具备的功能,综合考察ST,Broadcom等几大主流IPTV芯片厂商的方案以及目前的市场状况,笔者选择ST公司的STB7100芯片进行设计[2]。该产品是世界上第一个支持H.264/AVC和MPEG一2高清标准的单芯片解决方案,单片集成了高性能多标准的视频解码电路和机顶盒所需的全部功能。STB7100芯片是sTB710x系列中性价比很高的一款产品,在一个单片上集成了STB的所有功能和多标准解码电路,可同时解码多个高清视频流,并把合成的视频输出到2个电视机,或以画中画的形式显示到屏幕上。STB7100芯片提供了整套解决方案,嵌入式操作系统可采用Linux,OS21,WinCE中任一种,为上层的软件开发提供了更大的选择余地。

3 IPTV机顶盒硬件结构设计

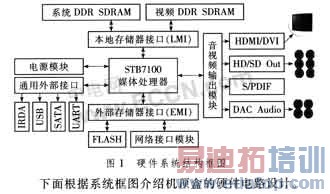

根据系统要求制定了硬件结构总体框架图,如图l所示,选用专用的机顶盒解码芯片作为主控CPU,并设计CPU的外围电路和必要的功能电路[3]。本地存储器接口模块(Local Memory Interface,LMI)的32位DDR存储器用于系统运行和音视频数据存储;外部存储器接口模块(External Memory Interface,EMI)提供了对各种外设的支持,包括Flash,ROM和网卡等。其中,网口模块用于完成接收及处理IP数据和音视频流功能;音视频输出模块完成音视频信号的输出功能;电源模块负责芯片及整个系统的供电;外部接口完成CPU对各功能模块的信号传输的控制功能。

3.1机顶盒核心处理芯片STB7100

sTB7100是一款高性能、单芯片集成的音视频解码的媒体处理器,其主要模块有:

1)处理器核心器件

主频为266 MHz的高性能ST40是器件的CPU核心,属于ST的32 bit RISC系列,采用SuperH体系结构,负责控制芯片的其他部分,包括与2个ST231CPU之间的通信。此外,还有2个主频都是400 MHz的ST231CPU用于处理音频和视频。

2)视频解码模块及接口

sTB7100支持多种视频解码标准,包括H.264/AVC,MPEG一2双向解码标准。分辨力最高支持1 920×1 080i或l 920×720p。同时,STB7100拥有D1标清输入、RGB/YPbPr/YC/CBS模拟的高清和标清输出等多种视频接口,还集成了高带宽数字媒体接口(HDMI)和高清晰内容复制保护接口(HDCP)。

3)音频解码模块及接口

采用1个400 MHz的ST231 CPU作为解码器,兼容所有通用的音频标准。音频流输入可以是I2S格式的PCM数字输入或经过内存的传输子系统内部源输入。输出接口包括S/PDIF串行数字音频输出和24 bit立体声模拟输出。

4)其他外设接口

STB7100提供了丰富的外设接口供选择,包括UART接口、红外接口、SmartCard接口以及1个串行ATA(SATA)硬盘接口和1个USB2.0主控制器端口。

3.2本地存储器接口模块(LMI)

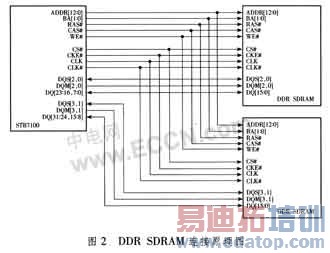

为满足不同类型视频的要求,必须有足够的内存空间用于存储和解码视音频流。LMI选择64 Mbyte大小的内存用于H.264解码或MEPG一2双向解码,其连接方式如图2所示。

其中,DDR的内部块寻址由BAO和BAl决定,可寻址4个内存块,即一个内存芯片存在4个Bank。A0一A12用于对块内行地址进行寻址,AO~A8用于对块内列地址进行寻址,所以每个芯片的容量为32 Mbyte。由于每个内存芯片的位宽是16位,CPU的数据位宽是32位,为了和CPU保持协同工作,必须传输和CPI.I总线位宽一致的数据量,所以需要2个内存芯片,以达到32位数据宽度。2个32 Mbyte内存芯片同时工作,用同一个片选信号CS控制,也用相同的BA0和BAl信号来控制Bank的选择。

3.3外部存储器接口模块(EMI)

EMI是sT芯片用来支持一般用途的外部存储器接口,被分成5个Bank,允许系统支持各种类型的存储器、外部处理器接口和其他设备,通过5个不同的片选信号访问5种不同的设备。系统中提供了FLASh{和网卡两种类型的设备。下面分别介绍这两种设备:

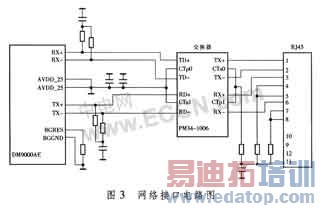

1)FLASH是用于存储U-boot引导代码、内核以及文件系统的设备,其首地址默认为系统上电时的起始地址。FLASH采用了ST公司的M58LW064D,它是一个64Mbyte FLASH存储器,采用0.15μm NOR工艺,使用2.7~3.6 V单电源。存储器被分成可单独擦除的64块,每块1 Mbyte。编程和擦除命令通过接口写进存储器,在实际应用中,通过U-boot下的cp,erase和protect命令对FLASH进行写入、擦除和保护操作;状态存储器提供了各种操作的状态信息;存储器写缓冲区允许处理器以并行方式编程l~16 byte。为了能对其他块进行编程、擦除,正在编程的块可先挂起,然后恢复;块保持功能使被保护的块不能编程和擦除。上电时,所有块均被保护,块保护命令可用于保护或中止保护某些块。当编程、擦除能使Vpen低电平时,则阻止了所有编程和擦除。STS信号可被设置为准备好/忙(RY/BY)两种模式,高电平为准备好,低电平为忙,在这里设置为高电平,始终为准备好状态。 2)在综合考虑功能和价格等各个方面的因素后,采用了DAVICOM公司高性价比的DM9000AE快速以太网控制处理器作为网络接口,其电路原理图如图3所示。其中网络变压器用的是PPT公司的PM34-1006M,本身不支持AUTO MDIX,所以需要将CTp0与CTsl,CTsO与CTpl连起来。

4 IPTV机顶盒软件结构设计

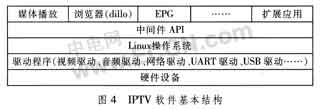

考虑到成本和通用性,机顶盒采用Linux操作系统。嵌入式操作系统负责机顶盒系统的全部软件和硬件资源的分配、调度工作,控制并协调并发活动,能通过装卸某些模块来达到系统所要求的功能。图4表示了系统的软件结构,以Linux操作系统为核心,向下通过各个驱动程序面向硬件系统,调配各种硬件资源,向上可加载与音视频相关的应用程序和完成其他任务的应用程序[4]。

机顶盒可划分为3层结构:操作系统以下主要用于完成对硬件设备的操作,为上层提供支持;API层承上启下,将应用程序翻译成CPU能够识别的指令,去调用硬件设备完成相应的操作;最上层主要实现媒体播放、浏览器以及EPG等应用,由用户直接操作。

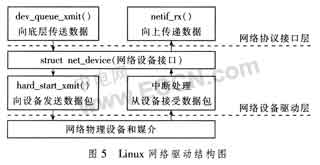

图5为Linux网络驱动基本结构,在发送数据时,应用层数据通过dev_queue_xmit( )向下层发送数据,dev_queue_xmit( )通过网络设备接口hard_star_xmit( )函数指针向设备发送数据,将应用层的数据发送给硬件设备;在接受数据时,当网络数据到达设备后产生中断,进人中断处理子程序,然后调用接受函数接受数据,再通过netif_ix( )函数发送给上层。编写DM9000AE驱动时,除实现探测、发送接受及中断等函数外,还要与开放的板子相对应,需注意网卡的基地址和中断。由于DM9000AE的地址线和数据线是复用的,所以要根据电路原理图来确定用来读取数据的I/O端口地址线和数据线的关系。

在网络功能实现的基础上,本设计采用NFS协议实现网络挂载文件系统,把boot loader和内核镜像写到FLASH上,这样可把应用程序直接放到PC机的文件系统里,节省了机顶盒的内存空间。目前,硬件电路设计已完成,经过测试,可播放H.264和MPEG一2的高清和标清视频码流,同时可播放MPEG一1,AAC,PCM等格式的音频内容。另外,采用了基于GTK的Dillo浏览器,由于不支持.1avaScript,Java等附加功能,使得它具有规模小速度快的优点。可以把视频模块、EPG模块等各种功能模块以插件方式与Dillo浏览器一起使用。当需要进行交互服务时,可通过HTTP协议访问EPG服务器,得到EPG相关信息,并在本地进行解析重构出EPG。如果需要点播视频,就通过:EPG去视频服务器上得到视频源的URL,然后对URL进行解析,再交给视频功能模块进行解码播放。

5 小结

介绍了IPTV机顶盒硬件电路的基本组成模块,确定了以STB7100为核心的系统解决方案。STB7100具有强大的音视频处理能力,并可通过其丰富的外围接口进行功能芯片的扩展,实现各种需要的功能。笔者虽然已实现了部分功能,但机顶盒设计仍需完善,还需要对智能卡、数字版权管理等扩展功能做更深一步的研究。

上一篇:基于数字网络的会议系统技术

下一篇:NGN关键构介绍