- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

应用于锁相环的脉宽调整电路的设计

前言

在锁相环PLL、DLL和时钟数据恢复电路CDR等电路的应用中,人们普遍要求输出时钟信号有50%的占空比,以便在时钟上升及下降沿都能够采样数据,最大限度地提高数据传输的速度。为了达到这一需求,我们经常需要在时钟的输出加入脉宽调整电路来得到一个占空比尽可能达到50%的时钟信号。

近年来诞生了许多种类的脉宽调整电路。这些电路大致可以分为以下三类:第一类最为简单,即采用2分频器产生占空比为50%的时钟,2分频器并不是专为调整占空比而采用的,但的确达到了这一需求;第二类通过负反馈机制,采用数字或模拟控制,调整信号占空比,这类电路最主要考虑的是系统稳定性;最后一种是采用复杂数字算法的占空比调整电路,其实现相对比较复杂。因此本文主要分析设计前两种类型的脉宽调整电路。

2分频器作为脉宽调整电路

绝大多数PLL中使用2分频prescaler电路处理VCO输出的高频信号,既实现了反馈路径上的预分频要求,降低了后续反馈分频电路的工作频率和功耗;又实现了对输出信号脉宽的调整,基本满足了50%占空比的要求。但其最大的缺点在于减少了压控振荡器VCO一半的输出信号范围,对于高频信号的50%占空比需求,这一缺点体现得比较明显。

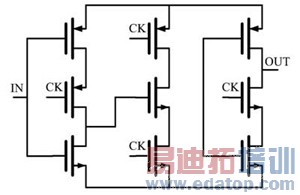

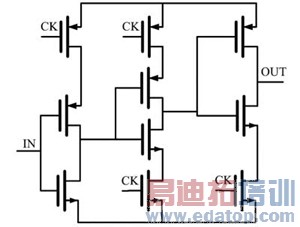

通常我们采用静态D触发器实现2分频,为了实现在高频工作时降低功耗,现在越来越多采用动态逻辑电路实现2分频。图1是一种传统的九管实现的动态2分频器。当时钟¢为低电平时,第一级时钟开关导通,采样输入信号,这时第二级输出的高电平保证了该电路的即时输出是前一次采样保持得到的信号,该信号电荷储存于输出节点的寄生电容。由于现代CMOS工艺已经进入深亚微米阶段,晶体管的漏电流现象越发明显,因此,该电路正常工作的频率不能太低。当¢变为高电平后,第一级刚才所采样的信号正确到达第三级的输入端,¢的高电平使得这一级成为普通反相器,实现了触发器的功能。由于采用了动态机制,利用寄生电容采样保持信号,减少了直流通路,降低了功耗,与静态逻辑实现方法相比,所用晶体管数量大大减少。该电路设计中,主要考虑时钟MOS开关的导通电阻和开关速度的折中以及信号上升下降时间的大致匹配。为提高该电路的速度,可以按照图2所示改进,与图1电路相比,时钟MOS开关更靠近电地,因此速度更快。对图2电路仿真结果表明,该电路最高工作频率可以达到12GHz。

图1 传统的动态触发器

图2 改进的动态触发器

负反馈脉宽调整电路

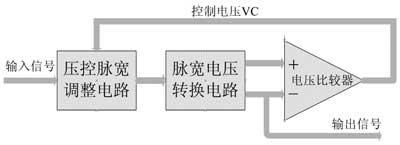

同锁相环电路利用负反馈机制锁定相位的原理类似,我们同样可以利用负反馈机制构建简单系统来调整信号占空比。该系统主要有以下几个模块构成:压控脉宽调整器、脉宽电压转换器和电压比较器等。系统模块图如图3所示。

图3 负反馈脉宽调整电路模块

压控脉宽调整器可由压控延时线VCDL和鉴相器PD组成。简单的VCDL可以由一串反相器构成,其输出信号是输入信号的延时,延时大小由控制电压VC决定;鉴相器PD可由静态RS触发器构成。两个同频存在延时的信号输入鉴相器后,检测的是两信号上升沿之差,即产生了脉宽与延时成线性关系(延时小于一个周期)的同频输出,延时越长(在一个周期范围内),则PD输出信号的占空比越大。因此,要实现宽范围信号占空比的调节,重要的是实现VCDL的宽范围。

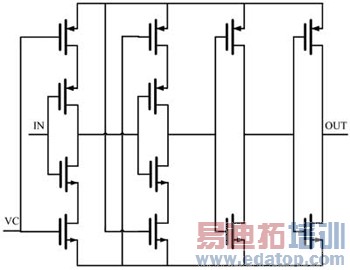

另外一种更为简单的压控脉宽调整器是脉宽伸缩电路,如图4所示。该电路通过调整信号不同的上升/下降延时达到调整占空比的目的。图中靠近电地的MOS管电流源的电流大小由控制电平VC决定。控制电压较大时,NMOS电流镜的电流大于PMOS电流源中的电流,信号上升比下降要慢,反之亦然。因此,改变控制电压的大小,即实现了信号上升下降延时的不同,从而实现了脉宽的调节。

图4 压控脉宽调整器

设计该电路时,传输信号反相器中的MOS管采用最小特征尺寸,并保证较大的宽度,使MOS管开关迅速,提高电路的工作频率;作为电流源使用的MOS管,为减少沟长调制效应,晶体管的长度应该比较大,这样对减少噪声也有帮助。另外要注意的是,当控制电压处于电源电压一半时,调整P、N电流源电流基本一致,这一要求确定了它们的相对宽长比,对扩大电路工作范围有重要的作用。由于电路调整了信号上升/下降的延时,有可能在高频应用时会对信号的完整性有所伤害,因此必须在该电路的输出加上缓冲器,根据负载决定缓冲器的驱动能力。为了适应后续模块比较的要求,需要产生相位互补信号。该电路可由两条反相器链组成。由于正相路径比反相路径少一级,为保证信号的相位互补,我们对正相路径的负载增加MOS电容,通过增大正相路径延时来达到互补的要求。

脉宽调整电路中的另一个模块是脉宽电压转换器,它的功能是产生与脉宽成线性关系的电压信号。本设计中采用两个对称的转换器实现对压控脉宽调整器输出互补信号的脉宽比较。如果输出时钟是50%占空比,其互补信号脉宽基本一致,则两转换器的输出电平也是基本相同的。由于考虑的是电压相对值,因此脉宽电压转换过程中产生的一些非理想因素,比如充放电流不匹配、电荷共享等,可以忽略。该转换器的基本原理是由脉宽控制电流源对电容充放电。在脉宽比较极端的情况时,该电路也能够正常反映当前信号占空比的正确关系。

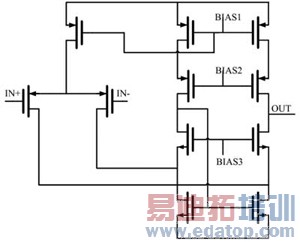

系统中另一个模块是电压比较器,它在整个负反馈系统中起着重要的作用。本设计中采用跨导运算放大器OTA对脉宽电压转换器输出的电压值进行比较,并产生压控脉宽调整器所需的控制电压VC,构成整个系统的负反馈回路。该OTA需要较高的直流增益和较大的带宽。为了更好地保证整个环路的稳定性,放大器采用一级折叠共源共栅结构。图5为该放大器的电路图。

图5 折叠共源共栅跨导运算放大器

当压控脉宽调整器输出信号具有约50%占空比时,转换器的输出电压维持在较小的值(考虑充放电荷大致相同),因此,采用PMOS管作为放大器的差分输入符合输入范围的要求。为了扩大输出范围,放大器采用了宽范围Cascode电流镜作为有源负载。

经过仿真可得,该放大器直流增益达65dB,完全满足系统要求。为了保证反馈环路稳定以及减少控制电压上的纹波(ripple),放大器的负载电容应取得较大一些,以降低主极点频率。考虑面积方面的因素,该电容可以采用NMOS电容,这种电容的单位面积电容值比其他类型的集成电容都要大的多。该电容的缺点是电容值受工艺、电压等因素变化较大,而且漏电随栅氧化层厚度减小而增大,但在此处做相位补偿和滤波之用,可以忽略这些缺点。

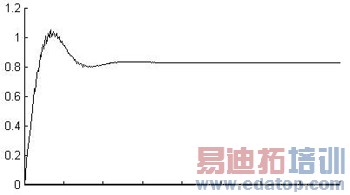

整个系统中最重要的是系统环路稳定性的问题,该闭环系统的环路增益是:Loop gain=1/(1+s/p1)×A0/(1+s/p2)只要放大器的负载电容足够大(大约30pF),就可以使环路有足够的相位裕度保证整个闭环系统的稳定。典型的二阶系统控制电压稳定曲线如图6所示。在脉宽电压转换器中,我们可以采用类似于电贺泵的电容充放电结构,也可以采用本次设计中采用的简单低通滤波器结构。考虑到这两种结构所引入的极点p1的位置不同,因此后者更加容易稳定。

图6 典型的二阶系统控制电压稳定曲线

该系统在SMIC 180nm数字工艺下,采用Cadence公司的Spectre仿真器通过仿真,工作频率范围100MHz~1.5GHz,稳定时间约在1~3μs,有效输入占空比为30%~70%,输出占空比误差在0.5%之内,基本满足了宽范围应用中所需的50%占空比设计要求。

该系统的误差主要来自环路有限的增益以及控制电压上的纹波抖动。另外,保证压控脉宽调整器足够的范围和线性度,都对提高系统的性能有重要的作用。因此在压控脉宽调整器中采用VCDL结构比直接采用脉宽伸缩电路有优势,但脉宽伸缩结构实现更为简单。

作者:同济大学 孙春来 来源:今日电子/21IC

上一篇:大中型呼叫中心的数字化管理

下一篇:SAS存储系统中的电缆

件