- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

LTE上行DFT/IDFT的一种设计实现

摘要:根据3GPP协议规定,提出一种适于FPGA实现的解决方案。采用分而治之和WFTA的算式分解,最大限度地减少DFT的运算量;采用块浮点动态截取多余位宽,减少系统面积;运用4个双端口RAM读写,使系统能运行在流水线结构;采用对称结构存储每一级的旋转因子,最大化共享因子。

为了降低手机终端的功率损耗[1],LTE上行链路采用基于DFT扩频OFDM(DFTS_OFDM)的单载波传输,又称为单载波FDMA(SC_FDMA)。DFTS_OFDM方案的基本结构如图1所示。3GPP协议规定[2]上行PUSCH信道产生SC_FDMA符号要求DFT点数满足式(1)。

由几个参数的变化可以得到最小12点、最大1296点共35种模式的DFT[3]。现在已有的研究方法(如质因子分解结合WFTA算法)解决非2n点DFT,但此法不够灵活,不适合长度可变的DFT。在数字电视DTMB系统中,3780点FFT的处理采用分裂基与质因子分解结合WFTA算法实现,但对于LTE上行可配置长度DFT的实现还没有一个成熟有效的方法。

根据LTE实时系统需求采用pipeline流水线结构实现高速可配置的DFT设计,同时在结构和资源利用上进行优化,最后给出仿真图形以及综合结果,为上行LTE设计提供一种参考。

2 总体结构及技术实现

2.1 整体结构框图

LTE DFT的模块化总体结构如图3所示,根据算法分析可以知道LTE DFT的分而治之需要几个阶段才能完成,每个阶段需要做多次小因子点的DFT,所以图示是一个循环的形式。由状态机控制这些阶段的完成,直到最后一个循环结束输出数据。

其中前处理进入WFTA模块的包括对4个双端口RAM的读取控制以及对旋转因子ROM的读取,还有旋转因子地址的计算。饱和操作根据系统的最大bit数限定,对经过WFTA计算后的数据进行饱和处理,超过的bit数直接截取掉。

2.2 技术实现

2.2.1 4个双端口RAM的数据存储

为保证pipeline地处理每次循环的数据,这里采用4个双端口RAM对数据进行存取。对4、2、5、3四种小因子的WFTA计算来说,选4个RAM最方便,如果需要进行4点的WFTA计算,则从每个RAM中读出一个数据,这仅需要一个时钟就可读出4个数据。对2点的WFTA计算,则可以一个时钟读出两组的2点WFTA进行计算。对3点的用一个时钟,对于5点的用两个时钟读取。

在基于原位计算的基础上进行改进,加入旋转数据模块,是为了将本来是在一个RAM中的数据在填入RAM前进行旋转,使其在不同的RAM中便于下一阶段pipeline读取。图4展示了一个最简单的12点的填写RAM实例,在开始第一阶段前先将12点的输入数通过载入buffer模块用12个clk按图3顺序载入4个RAM中,也就是将数据倒位序放入4个RAM中。将倒位序之后的数据重新标号,即1对应载入buffer的3,2对应6等。这样做的目的是为了方便计算地址。例如,在第一阶段读的过程中,0、1、2、3通过右移2bit,即除以4可以算出地址为0,它们分别对应4个RAM的第0地址;同理4、5、6、7除以4可以得到1,即对应1地址,依此类推。

根据公式4的推导可知在第一阶段DFT的处理中不需要乘以旋转因子,所以旋转因子为0,在第一阶段和第二阶段中需要先乘以旋转因子,旋转因子按照公式推导处理列出在表中。在第一阶段先处理0、1、2、3四点的WFTA,然后按原位顺序填入4个RAM,接着处理4、5、6、7四点的WFTA,本来应该也按原位填入RAM中,但是注意到在第二阶段需要处理0、4、8三点的WFTA,如果还按照原位填入,则0、4、8三个数据在同一个RAM中,要读取这3个数需要3个clk,显然不适应pipeline的处理。所以在做完4、5、6、7四点的WFTA之后将数据旋转再写入4个RAM中,同样将8、9、10、11四点的结果也旋转,如图4所示。这样的读写RAM操作可以保证pipeline的处理。

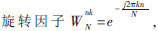

2.2.2 旋转因子的存取

根据式(4)的推导,每一级之间需要先乘以旋转因子,对于旋转因子的地址计算依据式(4)的推导。由于要实现35种可配置模式的DFT设计,所以在实现时要尽可能地考虑旋转因子的共享存储,从而尽可能地减少存储这些旋转因子的ROM大小。

一般做法是将N点的旋转因子全部存储,然后根据算出来的nk乘积来查找对应的旋转因子,这样35中模式需要很多的ROM地址来存储。这里将具有2的幂次方关系的旋转因子共用,如12、24、48…768点DFT的旋转因子共用,12点的旋转因子是24点的一部分,24点的是48点的一部分等,这样就只需要存储具有两的幂次方关系的DFT点数的最大那个点768点,又由于旋转因子自身的对称性,只存储最大点数的1/8就可以了,其他部分通过对称性来查找。具体实现步骤如下:

一般做法是将N点的旋转因子全部存储,然后根据算出来的nk乘积来查找对应的旋转因子,这样35中模式需要很多的ROM地址来存储。这里将具有2的幂次方关系的旋转因子共用,如12、24、48…768点DFT的旋转因子共用,12点的旋转因子是24点的一部分,24点的是48点的一部分等,这样就只需要存储具有两的幂次方关系的DFT点数的最大那个点768点,又由于旋转因子自身的对称性,只存储最大点数的1/8就可以了,其他部分通过对称性来查找。具体实现步骤如下:

(1)根据2的幂次方关系特性,将35种模式的DFT旋转因子分成10组,并存储这10组中最大的点的八分之一构成一个ROM。对于N点(对应组中最大的点),只存储[N/8]个地址数据;

(2)对于计算出的旋转因子地址K,根据它所处的DFT模式,选择它所属的组,10组分别用{R0,R1,R2,…,R9}表示;

(3)如果K在R5,则R0+R1+R2+R3+R4为它的偏移地址offset;

(4)12点的DFT需要用此组中最大的768点ROM表来找数,则地址K有可能是[0,…,11]×768/12中的一个作为有效地址eff_dft_addr;

(5)对于算出的eff_dft_addr,根据对[N×1/8],…,[N×7/8]的比较找出它处于768点中的哪个位置(此处N为768),即哪个1/8象限;

(6)找出所处的象限后,再找出其在第一个1/8对称的位置值dft_8_addr,计算出dft_addr=offset+dft_8_addr,然后在ROM表中找出对应的值,再根据对称性还原其原来的所属象限的值。如图5所示,展示一个点的查找方式。通过查找A″的值来得到A的值。

2.2.3 WFTA的运算单元

WFTA算法对2、3、4、5、7、8、9、16等小N点有较快速处理能力,它将小N点DFT转换为循环卷积,利用多项式理论使卷积计算尽可能减少乘法。

2.2.4 块浮点的数据处理

定点运算的特点是速度快但动态范围小。浮点运算的特点则是动态范围大但占用资源大。块浮点具有两种运算的优点,是两种运算的折中,让一组数具有共同的阶码,这个阶码是同组数中最大的那个数的阶码,简化系统资源提高运算的精度[6]。

如表1所示,因为每次WFTA运算后都有数据位宽的扩展,本结构具有3bit的扩展。为保持输入wfta_top的模块数据始终为18bit,这里用块浮点动态截取的方法对每一级的WFTA结果进行处理,动态截取的位宽决定下一级的数据宽度,同时循环累加每个阶段的阶码,在数据输出时进行还原操作。

3 仿真综合

图7所示为12点DFT的仿真图形,dft模式是第一种,首先data_in_vld为高时开始数据输入,然后用12个clk将数据读入4个RAM,之后计算第一级RAM读取地址将数据读出,处理3次4点的DFT,处理后将数据写入RAM,需要3个clk;再后读出数据做4次3点的DFT,处理后将数据写入RAM,需4个clk;最后将数据读出做压缩还原处理,data_out_vld为高后pipeline出数,需要12个clk。理论上需要31个clk,但是在处理中需要处理与其他模式的共享,还要有打拍延时等操作,实际用掉98个clk。120点的DFT实际用502个clk,理论上是120×2+30+30+24+40=364个clk,说明处理的点数越多冗余clk比例越小。

使用Stratix III EP3SL340F1517I3芯片,运用Quartus II综合后的结果为:7824个组合ALUT,0个内存ALUT,8699个逻辑寄存器,可达到时钟124.64MHz,满足LTE系统时钟122.88MHz的要求。

文章在介绍LTE上行SC_FDMA的基础上,对35种模式的DFT预编码进行算法分析,提出并用FPGA实现了一种高速可配置的方案。文中对数据存储、WFTA运算单元和块浮点处理进行简单表述,根据旋转因子特性,详细介绍了旋转因子的优化,大大降低了35种模式旋转因子的存储大小。最后给出的仿真综合结果表明该方案具有较好的性能。

作者:刘少雄 林平分 来源:《微型机与应用》2011年12期