- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

无线通信电台的通信协议研究

录入:edatop.com 点击:

摘 要:通信协议是通信系统在通信链路上实现复杂任务的软件构架及程序编写规则,任何通信系统之所以能正常工作离不开通信协议的支持。本文以研制一种通信电台为例,提出了一种适合无线通信电台的通信协议,实验结果证明此协议具有很好的性能。

关键词:通信电台;通信协议;DSP;FPGA

一、引言

任何通信系统均有一定的通信协议支持来完成通信的任务,一般通信系统至少包括物理层通信协议和链路层通信协议。物理层通信协议用于在数据链路的实体之间为位传输所需要的物理连接的建立、保持和拆断提供电气的、机械的、功能性的特性。链路层协议是在通信系统的物理层正常工作的基础上进一步管理和控制,主要完成建立链路、拆除链路、流量控制、同步控制和差错控制的功能。本文提出的通信协议主要包括物理层协议和链路层协议,经过通信电台的试验证明它是一种可靠的高效的通信协议,具有较高的理论意义和工程应用价值。

二、通信协议的原理

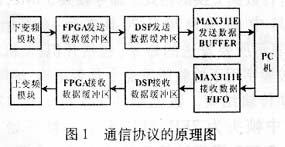

本文提出的一种通信协议用在一种无线通信电台上,此协议能很好地满足此通信电台间歇式工作的要求,其原理如图1所示。

当无线通信电台的天线接收到信息时,上变频模块把射频端的数据送给现场可编程门阵列器件(FPGA)进行解码,FPGA解码后的数据放在FPGA的发送数据缓冲区,此缓冲区大小设置为1024 byte大小,当此缓冲区满时产生一中断信号触发数字信号处理器(DSP),DSP内开辟一个大小为1 024 byte的缓冲区txqueue,txqueue通过数据总线方式接收FPGA发来的数据,当txqueue满时,再通过DSP的定时器中断方式把txqueue内的1 024 byte的数据发往接口器件(MAX3111E)内的发送数据Buffer,此Buffer内的数据最终发往个人计算机(PC),PC机对这些数据进行分析和处理。

当PC机有数据和命令要发送时,首先把PC内的数据或命令以9 600 bps的速度通过MAX3111E的接收数据FIFO发送到DSP中1 024 byte大小的数据缓冲区rxqueue,当rxqueue的数据满时,查询FPGA的接收数据缓冲有没有空,如果FPGA的接收缓冲区空时,则把rxqueue的数据发往FPGA的接收数据缓冲区,FPGA对接收缓冲区的数据进行编码处理后送上变频模块。PC机发送的帧包括命令帧和数据帧,帧结构如表1和表2所示。

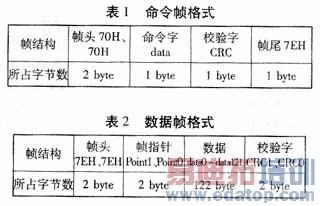

命令帧用于向DSP发送开机、关机、复位等命令用来监控电台的工作,数据帧用于定义PC和DSP进行数据交换的格式。命令帧共5 byte,即5×8 bit,其 中 帧 头为70 H、70 H表示一帧开始传输,data1表示所要发送的命令(包括开机、关机、复位等),校验字用于检验所发命令是否正确,帧尾7EH表示帧传输结束。数据帧共128 byte,即128×8 bit,其中帧头为7EH、7EH表示一帧开始传输,Point1、Point0用于计算已传输出帧的个数,Point1表示计数器的高位数值,Point0表示计数器的低位数值,data0~data121表示所要发送的数据,校验字CRC1、CRC0用于检验所发命令是否正确,此类帧采用循环校验码CRC的16位校验方式,此帧不设结束标志,校验结束即表示数据帧传输结束。

关键词:通信电台;通信协议;DSP;FPGA

一、引言

任何通信系统均有一定的通信协议支持来完成通信的任务,一般通信系统至少包括物理层通信协议和链路层通信协议。物理层通信协议用于在数据链路的实体之间为位传输所需要的物理连接的建立、保持和拆断提供电气的、机械的、功能性的特性。链路层协议是在通信系统的物理层正常工作的基础上进一步管理和控制,主要完成建立链路、拆除链路、流量控制、同步控制和差错控制的功能。本文提出的通信协议主要包括物理层协议和链路层协议,经过通信电台的试验证明它是一种可靠的高效的通信协议,具有较高的理论意义和工程应用价值。

二、通信协议的原理

本文提出的一种通信协议用在一种无线通信电台上,此协议能很好地满足此通信电台间歇式工作的要求,其原理如图1所示。

当无线通信电台的天线接收到信息时,上变频模块把射频端的数据送给现场可编程门阵列器件(FPGA)进行解码,FPGA解码后的数据放在FPGA的发送数据缓冲区,此缓冲区大小设置为1024 byte大小,当此缓冲区满时产生一中断信号触发数字信号处理器(DSP),DSP内开辟一个大小为1 024 byte的缓冲区txqueue,txqueue通过数据总线方式接收FPGA发来的数据,当txqueue满时,再通过DSP的定时器中断方式把txqueue内的1 024 byte的数据发往接口器件(MAX3111E)内的发送数据Buffer,此Buffer内的数据最终发往个人计算机(PC),PC机对这些数据进行分析和处理。

当PC机有数据和命令要发送时,首先把PC内的数据或命令以9 600 bps的速度通过MAX3111E的接收数据FIFO发送到DSP中1 024 byte大小的数据缓冲区rxqueue,当rxqueue的数据满时,查询FPGA的接收数据缓冲有没有空,如果FPGA的接收缓冲区空时,则把rxqueue的数据发往FPGA的接收数据缓冲区,FPGA对接收缓冲区的数据进行编码处理后送上变频模块。PC机发送的帧包括命令帧和数据帧,帧结构如表1和表2所示。

命令帧用于向DSP发送开机、关机、复位等命令用来监控电台的工作,数据帧用于定义PC和DSP进行数据交换的格式。命令帧共5 byte,即5×8 bit,其 中 帧 头为70 H、70 H表示一帧开始传输,data1表示所要发送的命令(包括开机、关机、复位等),校验字用于检验所发命令是否正确,帧尾7EH表示帧传输结束。数据帧共128 byte,即128×8 bit,其中帧头为7EH、7EH表示一帧开始传输,Point1、Point0用于计算已传输出帧的个数,Point1表示计数器的高位数值,Point0表示计数器的低位数值,data0~data121表示所要发送的数据,校验字CRC1、CRC0用于检验所发命令是否正确,此类帧采用循环校验码CRC的16位校验方式,此帧不设结束标志,校验结束即表示数据帧传输结束。

上一篇:部署无线IPS

下一篇:我国数字集群通信发展的几点考虑