- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于姿态测量的微型存储系统的设计

中北大学 张学彦 张彦军甄国涌

微型姿态测试系统在航天科技领域起着越来越重要的作用,对确定飞行体各种飞行姿 态有着重要的参考意义。在测试领域中,低功耗,小体积,噪声小,大容量已是竞争的主要目标。微型姿态测试系统主要用于飞行体抛撒后到落地前的三向角速度及线加速度参数的测 量、采集、编码和记录,并在飞行体硬回收后完成遥测数据的事后读取和处理。

在本文的设 计中,飞行体姿态微型存储器测试系统达到并满足了传统上难以胜任的高性能指标和许多技 术上的苛刻要求,其中体积小,低功耗,抗过载性能高是本文设计的主要方面。从系统结构设计、电源设计以及状态设计等环节保证了小体积、低功耗的设计要求,也提高了整个系统 的抗高过载性能。

1 微型姿态存储测量系统的模块组成及工作原理[1]

如图1 所示,为微型姿态存储测量系统框图。整个系统由过载开关、惯性组合、电源控制及变换电路、信号调理电路、A/D 转换系统、中心控制逻辑单元、FLASH 存储器和读数接口电路等组成。

飞行体在空中飞行中当达到额定的过载量时,系统将由过载开关来触发启动信号,飞行 体的三维角速度及线加速度参数由惯性组合转化为供记录器采集的模拟信号,记录器将在 FPGA 中心控制单元的时序控制下对模拟信号进行采集、编帧和存储,当记录器被收回时, 将由地面检测系统对存储器的数据进行读取和事后处理。

电源控制及变换模块接收到“启动”命令后,就将飞行体上装载的电源经转化输出给惯 性组合供电,同时将系统电池经过变换输出系统3.3V 给整个记录装置供电。信号调理模块就是把惯性组合信号调理成可以被记录装置接收的0~3.3V 信号,同时保证记录装置足够的 输入阻抗,即不影响被测信号的电气特性。

6 通道12 位A/D 转换系统的功能是在中心控制 逻辑模块的控制下,按照12KHz 的采样率对惯性组合送来的6 路信号进行采集,并将采集到 的数据送到中心控制逻辑模块中。

中心控制逻辑模块是整个记录装置的核心部分,它的功能是对6 通道12 位A/D 转换系 统送来的数据按顺序采集后送入128M 容量的8 位 FLASH 存储器中,其路采样率为2KHz。

在 中心控制逻辑模块开始工作的同时,就随之发出“自保”命令给电源控制及变换模块,以保 证电源控制及变换模块即使在过载开关再断开后仍能正常工作,即保证过载开关的触发有效性。128M 容量的8 位FLASH 存储模块主要用于数据的存储,其容量为128M,数据位为8 位。 由于FLASH 存储器具有掉电保持数据的功能,所以不需要设计后备电池进行掉电,な据。根据前面的技术指标可知,128M 的容量远满足所要求的存储容量。

读数接口模块主要用于 记录装置检测时和回收后数据的读取。 2 微型存储器系统的硬件设计微型姿态存储器测试系统对电源有苛刻的要求,因为此测试系统由电池供电,根据低功 耗的设计原则,本设计采用了MAX8882 的低压差电源控制芯片,对输入3.5V~5V 电压能同 时转换出3.3V 和2.5 电压,通过逻辑程序控制电源芯片可有效控制整个系统的耗电量。当 启动电源控制系统时,逻辑控制中心产生自保信号来控制MAX8882 的shutdown 使能端,使 整个系统正常供电。当采集存储过程完成时,逻辑控制中心产生触发信号来控制MAX8882 停止工作,从而整个系统处于节能状态。

微型姿态存储器的电路设计思路主要依据对飞行体的姿态参数进行实时采集,编帧和存储这一思路进行设计,信号调理电路是将姿态模拟信号进行分压、滤波和跟随运放后传送发给模数转换芯片, 模数转换电路采用了美信公司的MAX1295 芯片,它是6 通道12 位精度逐 次逼近式的数模转换器,采样率为265Ksps,片内集成了高性能的采样保持电路和参考电压源。同时还具有较低的功耗和较高的信噪比,可以进行内部和外部的采样模式设置,在本设 计中采用了外部采样模式。

存储系统采用了三星公司的K9F1G08 FLASH 存储器,该芯片性能良好,封装较小,为 微型化测试系统设计提供了便利,在逻辑中心的时序控制下,对存储器进行读、写、擦除操 作,每种操作都采用了由FLASH 的状态信号r/b 进行中断的方式。在写操作过程中,以8 位数据进行存取,在存储一页数据时要进行页编程,大约要300us~700us ,等待r/b 状态 信号的改变后进入下一页的存储,为了使采集和存储的速度相匹配,在FPGA 内部采用了8K Bits 的双口RAM,在FLASH 存储器进行页编程的时候进行数据的缓存。在擦除操作过程中,对 FLASH 存储器要进行块擦除,擦除一块时间要2ms~3ms,等待r/b 状态信号的改变后进入下一块的擦除。同样在读取数据操作中,每读取一个字节都要等待r/b 的中断,数据通过 检测台和USB 电缆传给上位机。

本次设计的微型姿态存储器测试系统的另一个主要突出点在于它的微型化 ,整个的记 录器的各个芯片都采用了小型化的贴片封装,电路板采用了四层板工艺制作,中间分别为电源层和地层,不仅大大较小了记录器的体积,同时对信号的隔离和抗干扰性也起到了一定的 积极作用。

2 逻辑流程图设计

流程图见图2 所示,整个过程由过载开关启动电源控制芯片以启动整个FPGA 的控制 时序,复位模块由上位机复位,上电自动复位和软复位组合而成,当启动整个系统时,首先 要对系统初始化复位,同时定义一个触发信号“esok”使初始化为“0”,以便触发控制单元, 使系统进入自检状态,在自检模块中,FPGA 首先要从FLASH 存储器第六页连续读取16 页的 数据,并判断数据是否为“FF”,如果不是,则存储器内有数据存在,系统将停止在这个状态,如果是则触发信号“esok”为“1” 以启动A/D 采集数据模块和FLASH 存储数据模块, 此时,中心控制模块在响应采集模块的中断使A/D 模块以16K 的采样率往FPGA 内部的双口RAM 写数据,同时FLASH 存储模块在中心控制模块下,判断并推进RAM 的地址以读取RAM 的 数据,在数据不断写入FLASH 存储器的同时判断数据容量是否达到指定的数据量,如果没有, 则返回到FLASH 写状态继续存储数据,一旦达到,系统则触发一个信号来控制电源模块关闭 电源,使整个系统停止工作,以减小耗电量。当插上读数口时启动USB 在线,在上位机的控 制下,对FLASH 存储器进行读取操作,以便对数据进行事后分析和处理。

结束语

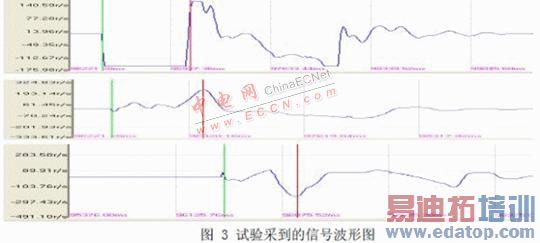

该微型姿态存储测试系统工作性能良好,在抛撒试验中得到如图3 所示的信号,达到了理论要求,成功的完成了飞行体姿态参数的采集和存储,通过多次试验证明,该微型测试系 统具有一定的工程应用性并对其他测试设计有着重要参考意义。