- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种高速数据采集卡的设计与实现

O 引言

测试设备是武器系统中最主要的子系统之一,它的工作正常与否将直接影响到整个武器系统的作战性能。在对武器系统进行测试的过程中,需要对一系列的电压、电流等模拟量信号进行快速、实时的数据采集和分析,检查这些模拟量的指标是否符合要求,可以对武器系统是否发生故障做出诊断,保证武器系统的正常工作。根据现代战争对武器系统的作战需求,提高快速机动保障能力,研制出体积小、结构紧凑、便携式的测试设备就成为主要的目标。

本文设计了一种基于PC/104总线的高速数据采集系统,其目的在于替代示波器在武器系统测试中的作用。常规采集方案主要有两种:

(1)由单片机直接控制的采集方案,这是最简单最常用的控制方案。由于每次采样都要有单片机的参与,需占用单片机的时间,影响其数据处理,而且对于多通道、多个A/D转换器的控制,因所需处理的信息更多,则更加不方便。

(2)由DMA控制的采集方案。此方案硬件电路复杂,若与单片机配合使用,需要单片机具有总线挂起功能,否则还需要进行总线切换,影响数据的及时处理。

综合以上两种方案的优缺点,本数据采集卡自动采样硬件电路主要采用可编程逻辑器件CPLD和先进先出FIFO(First In First Out)技术设计而成,可以很好地实现高速数据采集。

1 数据采集卡总体方案设计

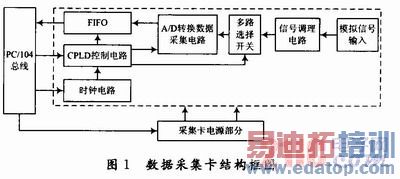

数据采集卡是由信号调理电路、带采样保持器的A/D模数转换器、多路模拟开关、FIFO数据缓存、CPLD芯片及时钟电路等部分组成,具有高精度、高可靠性、高抗干扰能力等特点。总体结构设计原理如图1所示。

2 芯片介绍

该数据采集卡采用的芯片主要有:AD9283模/数转换器、AD508A多路选择开关、EPM7128SCL84-6CPLD和CY7C4261 FIFO缓存器。下面对以上所用芯片做一简要介绍。

2.1 AD9283模/数转换器简介

本数据采集卡选用了ANALOG DEVICE公司生产的高速8位模/数转换器AD9283。它采用先进CMOS制作工艺,提供20脚表面贴装封装形式。片内集成高性能采样和保持放大器,输入信号可采用单输入或差分输入,处理输入电压峰峰值在0~1 V之间的模拟信号,采用单+3 V模拟电源和单+3 V数字电源,片内提供+1.2~+1.3 V的参考电压,最高抽样速率可达100 MSPS,具有高速并行输出接口。

2.2 EPM7128SCL84-6 CPLD芯片简介

本数据采集卡选用一片Altera公司生产的EPM7128SLC84-6CPLD作为核心处理芯片,它具有高阻抗、电可擦除等特点,可用门单元为2 500个,有64个用户可用I/O引脚,工作电压为+5 V,管脚间最大延迟为5 ns,采用PLCC-84封装,通过JTAG接口可实现在线编程。

2.3 CY7C4261 FIFO缓存器简介

本数据采集卡选用的FIFO器件是CYPRESS公司生产的高速、低功耗、先入先出存储器芯片CY7CA261。它的容量为16K×9位,读写周期为10 ns,支持异步和同步读写操作,写数据和读数据分别具有时钟和使能信号,具有“空、满、可编程几乎空、可编程几乎满”四个状态标志位,没有绝对地址的概念,只有读指针和写指针的相对位置,只要标志不为0,就可以进行写操作,只要标志不为0,就可以进行读操作,读写操作可以同时进行。

3 数据采集卡电路设计

3.1 信号调理电路

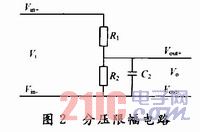

被测信号在进入A/D转换器之前,都必须进行适当的处理,使之符合A/D转换器的量程要求。对大信号需经过适当的衰减,而小信号则需要放大。本数据采集卡采用的A/D转换器的输入电压峰峰值在0~1 V之间,而被测信号幅度都大于此值,所以信号在进入A/D转换器之前需对其进行衰减处理。具体的分压限幅电路如图2所示。

3.2 A/D转换与FIFO缓存电路

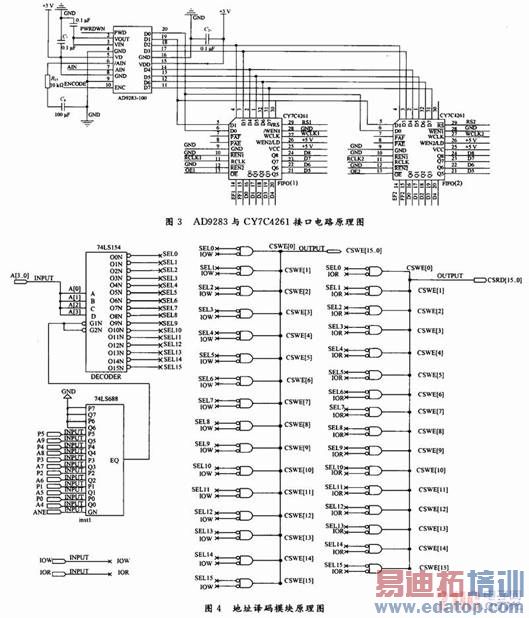

由于AD9283数据最大采集频率为100 MHz,所以其最大数据存储频率至少应为100 MHz,而CY7C4261的最大存储速率为100 MHz,能实现系统要求,系统中CY7C4261的写时钟与A/D转换采用同一个时钟进行控制。在测试过程中,有些待测信号周期较大,而本数据采集板的采样频率为100 MHz,为了在数据采集过程中不丢数据,需要连续采集大量数据。一片CY7C4261的存储容量不够,需要两片轮流存储。AD9283与CY7C4261的接口电路连接如图3所示。

4 CPLD在数据采集卡中的应用

CPLD作为整个数据采集过程的控制核心,负责地址译码、多路开关选通、A/D转换启动、将转换结果写入FIFO以及两片FIFO之间的切换等一系列操作。它的三个功能模块分别为:地址译码模块、多路开关控制模块、A/D采样及FIFO控制模块。

4.1 地址译码模块

该模块实现了CPLD内部与PC/104总线的接口单元。本数据采集卡是作为PC/104的标准外设进行工作的。PC/104规定,外设的操作地址为A[9:0],在系统软件设计中要防止地址冲突。PC/104中使用A0~A9地址位来表示I/O端口地址,即可有1 024个口地址,前512个供系统板使用,后512个供扩充插槽使用,当A9=O时表示系统板上的口地址,当A9=1时表示扩充插槽接口卡上的口地址。因此本数据采集板的基地址由A[9:4]来确定,偏移地址由地址线的A[3:O]确定,选择该地址就意味着相应的操作,CPLD对地址进行译码后就产生相应的控制。在Qu-artusⅡ上设计的地址译码模块原理图程序如图4所示。

地址译码的工作过程为:在拨码开关上手工设基地址,在CPLD内部划出一片74LS688地址比较器,比较CPU发出的基地址与手工设定的基地址是否一致,若不一致,则地址译码电路不工作,进而整个数据采集板都不工作,若一致,则74LS688输出低电平,使得偏移地址译码电路中的4-16译码器74LS154正常工作,在IOR,IOW信号的作用下产生各种控制信号,使数据采集板正常工作。

4.2 多路开关控制模块

该模块实现了对八选一多路选择开关ADG508A的选通控制。通过控制使能引脚EN以及CH0~CH2引脚,可对多路开关的输入通道进行可编程选择。PC/104CPU通过地址译码选中CSWE[2],并写入数据D0~D7,就可以选择不同的通道导通。在QuartusⅡ上设计的多路开关控制模块原理图程序如图5所示。

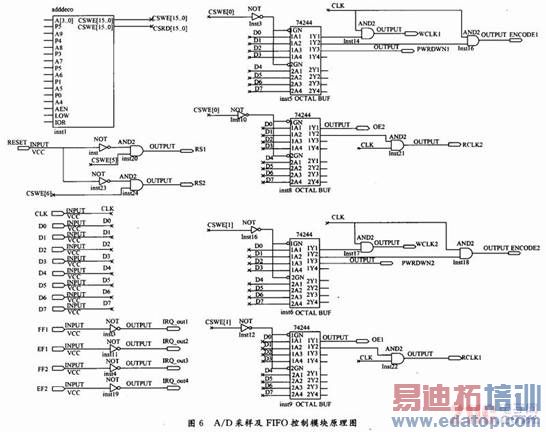

4.3 A/D采样及FIFO控制模块

该模块主要负责A/D芯片的转换时序,实现对A/D采样的合理控制,同时将转换数据存入FIFO中,并且控制着两片FIFO的轮流存储,实现大量数据的采集。PC/104CPU通过地址译码选中CSWE[O],写入数据D0~D7,将与门inst15打开,输出端ENCODE1输出100 MHz的时钟信号,PWRDWN1端输出为低电平,启动A/D转换,同时,与门inst14被打开,WCLK1端输出100 MHz时钟,将转换后的数据存入FIFO(1)中。选中CSRD[0],写人数据D0~D7,将与门inst21打开,OE2端输出低电平,使CY7C4261(2)输出使能,RCLK2端输出100 MHz的时钟信号,将数据读出。当FIFO(1)存储满时,CPLD控制由FIFO(2)来进行存储,同时将FIFO(1)中的数据读出,当FIFO(2)存储满时,转由FIFO(1)进行存储,同时将FIFO(2)中数据读出。如此反复,直至预定的延时时间止,实现了两片FIFO的轮流存储和读取,进而达到了采集大量数据的目的。另外,在每次采样及向FIFO中存储数据之前,都要求选通CSWE[5]或CSWE[6]将FIFO芯片复位,使其读指针和写指针都指向第一个物理存储地址。在QuartusⅡ上设计的A/D采样及FIFO控制模块原理图程序如图6所示。

CPLD硬件控制逻辑设计的关键是分析各个器件的工作时序和采样保持时间,A/D转换时间以及数据存入FIFO的时间等。在设计的时序处理进程中,要根据CPLD的工作频率计算各个等待周期,等器件准备好以后才能进行下一个处理。

5 结语

采用CPLD和FIFO器件设计了一种基于PC/104总线的高速数据采集卡,它可以作为PC/104总线标准模件使用。该采集板上的大部分控制逻辑被集成到CPLD芯片中,大大减少了扩展卡上的器件数量,同时降低了系统成本,提高了系统的可靠性。该数据采集板非常适合搭建高密度、小体积的便携式测试设备,可广泛应用于武器控制系统的测试等多种场合,对控制系统的模拟量信号进行快速、实时的数据采集和分析。

上一篇:电子负载及其在检测设备测试中应用

下一篇:基于虚拟仪器的电梯上行超速,ぷ爸眉觳庀低