- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于多路移相时钟的测频模块方案设计

本文根据雷达发射机频率快速变化的特点,采用目前新型的逻辑控制器件研究新型频率测量模块,结合等精度内插测频原理,对整形放大后的脉冲直接计数,实现对下变频后单脉冲包络的载波快速测频。具有测量精度高,测量用时短的特点,能作为脉冲雷达单脉冲瞬时测频模块。

1 移相时钟计数法测频原理

移相时钟计数法以等精度测频法为基础,是一种新的内插技术,其多路同频但不同相位的时钟由FPGA内部的PLL产生,然后分别传送到相应的计数器计数,在实际闸门开启时段各计数器同时计数;实际闸门关闭后,再将总计数值用于测频运算。具体方法为:实际闸门作为关键逻辑信号,通过全局时钟布线和4个同步计数器的计数使能端(cnt_ena)相连,作为计数器的计数使能信号;四路时钟信号作为计数器的计数时钟,分别和4 个计数器的时钟端(clk)相连,实现4个计数器对实际闸门脉宽计数,计数器设置为在时钟上升沿加1计数。设4个计数器的计数值分别为ns1、ns2、 ns3、ns4,假设总计数值为N′s,由于每个计数器计数值的变动都会使N′s的值发生变动,而n21、ns2、ns3、ns4对应的计数时钟相互有 90°的相位差(Tdk/4计数时间),则计数值N′s会在每Tdk/4时间增加1。等效于将一路标准计数时钟进行4倍频。在一次测量结束后(即实际闸门关闭),再利用公式计算得到实际闸门脉宽测量值,则等精度测频公式:

对比式(1)和(2)可知,将4个计数器计数值ns1、ns2、ns3、ns4求和运算的结果作为新的计数值进行测频运算,其测频结果等效为将标准频率4倍频。该结论也可从相对误差的角度进行说明,由于等精度测频法的实际闸门和被测信号同步,故式(2)中的Nx不存在量化误差。而实际闸门和标准时钟不同步,则N′s存在±1量化误差。则测频的相对误差为:

由于计数值N′s几乎为Ns的4倍,故式(2)所对应的误差是式(1)对应的1/4。即通过四路移相时钟测频的方法,在测量时间和基准时钟频率不变的情况下,使测量的相对误差变为原误差的1/4,测量精度提高了4倍。若增加移相时钟的路数,则测量精度会进一步提高。

2 新型测频模块总体方案设计

利用移相时钟计数法构建中频瞬时测量模块来实现频率的测量,该测频模块的测量对象是脉冲雷达接收机下变频后的中频信号。总体设计目标是构建一个数字化、综合化、自动化的测试平台,能满足脉内测频的要求,能进行远程通信,并有一定的移植型和升级性,建立系统的基本框架如图1。

整个系统的工作机理是:操作人员通过上位机人机界面对该模块进行参数设置和功能选择,人机界面的设定值通过串口传输到单片机,单片机作为测量模块的控制部件,控制FPGA完成相应的测量任务,FPGA负责具体测频算法实现。测试完成后,测试结果通过单片机传送给上位机人机界面显示,两者通过 RS232串口连接。整个设计中FPGA内部的测频算法电路为核心电路。

3 FPGA测频算法电路设计

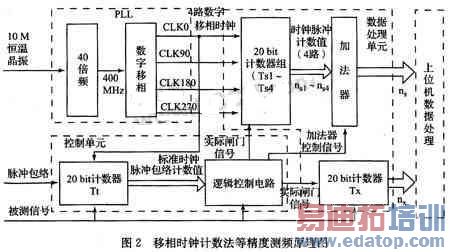

采用Altera公司StratixII系列EP2S15F484C5型FPGA为核心控制单元。内部的测频算法电路主要包括PLL输出时钟的走线、时序控制单元、数据处理单元。这些单元是实现测频算法的核心,需要将各单元按相互提供的接口在FPGA内部进行连接,构成完整的测频模块,实现等精度测频功能。输入信号分别为10 MHz的时钟信号、脉冲包络信号和被测信号;输出信号为时钟计数值和ns被测信号计数值nx,其原理总框图如图2。

利用PLL输出多路计数时钟,可在FPGA内部通过PLL级联的方式增大最大倍频数。首先利用EPLL将恒温晶振输入的10 MHz时钟倍频到50 MHz,传输给FPLL作为FPLL的基准时钟。FPLL再将输入时钟倍频到400 MHz,并移相、抽头得到四路移相时钟。FPLL移相度数设置为:0°、90.0°、180°、270.0°,最终实际度数和设置值一致。由于FPLL周围布置了4根全局时钟线,故FPLL的输出时钟全部可通过GLOBAL器件进行全局时钟线布线。

被测信号为脉冲调制波的载波信号。该信号经过整形放大电路处理后形成脉冲串输入到FPGA的专用时钟引脚。由于电路和器件的影响,脉冲串的头、尾部信号的幅度和频率均不稳定,在FPGA内部表现为频率波动较大,故只能选取脉冲串中间的稳定部分作为测量对象。

脉冲包络信号由检波电路提供,作为被测信号的脉冲宽度输入信号。若采用变闸门测频方式,脉宽计数器对每个脉冲包络的宽度进行测量,其脉宽值在脉冲包络下降沿时保存,并在下一个脉冲包络的上升沿之前提供给预闸门计数器作为预闸门计数参考值。

该测频方案需对连续波进行1 ms闸门时间的测量,对于400 MHz的标准时钟信号,采用二十位同步计数器对被测信号和标准时钟计数。二十位同步计数器的计数频率可达416 MHz,其最大计数值为1048576,用400 MHz的标准时钟信粤计数,对应的计数时间为2.6 ms。计数器用Quartus6.0软件中的Mega Wizard Plug-in Manager工具包调用ALTERA公司提供的IP核自动生成。

4 外围电路设计

外围电路包括为FPGA提供标准10 MHz时钟的恒温晶振电路;对输入信号进行放大、整形处理的整形电路;脉冲包络检测电路以及为整个模块提供-5 V、+1.2 V、+3.3 V、+5 V电压的电源电路。

本课题测频精度要求为±10-6,振荡器的频率精度至少要达到±10-7,只能选用压控恒温晶体振荡器构建标准频率源。本课题所用晶振为成都星华公司产品,通过仪器内部自带的Allan方差测试软件得到OCXO的秒稳在3.3×10-12,100 s的短稳在4.4×10-12。

信号接收机传送来的被测信号振幅通常只有毫伏量级,而FPGA的输入端口一般为LVTTL电平,故需要将输入信号进行电平转换。FPGA的 LVTTL电平格式输入端口的最高频率达到200 MHz,为了能和该频率值相配合,不形成速度瓶颈,采用超高速ECL电平输出比较器ADC-MP563完成信号整形功能,串接电平转换器 MC100EPT25完成差分ECL电平到LVTTL逻辑电平的转换。

脉冲包络检测电路检测被测信号的包络线,用于测量脉冲宽度。采用AD公司检波芯片AD8310构建检波电路,对被测信号的检波采用单端输入的方式。上位机用CV18.0构建人机界面。

5 仿真结果说明

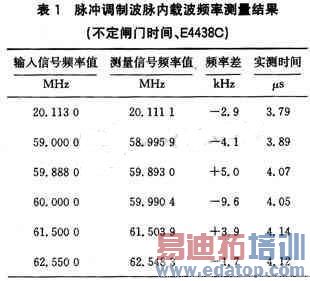

测试方法:分别用Agilent公司矢量信号发生器E4438C和任意波形发生器33250输出信号作为被测对象,用该测频模块对其信号频率进行测量,各计数值通过单片机串口上传到上位机处理软件,该软件通过程序实现式(2)的算法,计算测量频率值。测量结果如表1所示。

表1为不定脉宽脉内载波频率测量,闸门时间根据测量开始后第一个脉冲包络的脉宽测量值确定,由于E4438C在产生4μs脉宽时波动较大,故在某些频点实际闸门时间偏差较大。实验表明:系统对脉冲调制波载波测频,在不定脉宽(4μs左右)状态下对中频的测频精度优于±10 kHz。

表2为不定脉宽脉内载波频率测量。频率源为Agilent公司的任意波形发生器33250。实验表明:系统对脉冲调制波载波测频,在不定脉宽(≤400 ns)状态下对中频的测频精度优于±30 kHz。

6 结束语

本文所提出的基于多路移相时钟的等精度瞬时测频模块具有电路简单,性价比高的特点,可用于捷变频脉冲调制雷达脉内测频。最为核心的测频电路完全在FPGA内部构建,输入的标准时钟仅为10 MHz,不仅减小了布线和制板的难度,而且大幅提高了模块的抗干扰能力保证了测量精度。整个测频模块用一块板卡实现,通过测试达到预期效果,证明该设计方案具有很高的实用性。

上一篇:喷墨打印机在单片机测控系统中的应用

下一篇:超声波测距系统方案研究与设计