- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

5 Gsps高速数据采集系统的设计与实现

作者:吴琼之,蔡春霞,丁一辰,廖春兰

高速实时频谱仪是对实时采集的数据进行频谱分析,要达到这样的目的,对数据采集系统的采样精度、采样率和存储量等指标提出了更高的要求。而在高速数据采集系统中,ADC在很大程度上决定了系统的整体性能,而它们的性能又受到时钟质量的影响。为满足系统对高速ADC采样精度、采样率的要求,本设计中提出一种新的解决方案,采用型号为EV8AQ160的高速ADC对数据进行采样,考虑到ADC对高质量、低抖动、低相位噪声的采样时钟的要求,采用AD9520为5 Gsps数据采集系统提供采样时钟。为保证系统的稳定性,对模数混合信号完整性和电磁兼容性进行了分析。对ADC和时钟性能进行测试,并给出上位机数据显示结果,实测表明该系统实现了数据的高速采集、存储和实时后处理。

1 系统的构成

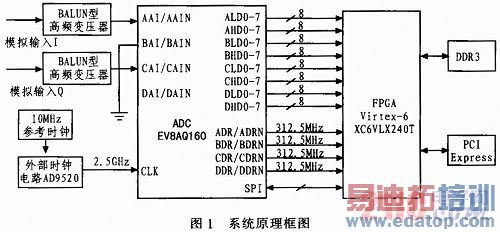

高速数据采集系统主要包括模拟信号调理电路、高速ADC、高速时钟电路、大容量数据缓存、系统时序及控制逻辑电路和计算机接口电路等。图1所示为5 Gsps高速数据采集系统的原理框图。所用ADC型号为EV8AQ160,8 bit采样精度,内部集成4路ADC,最高采样率达5 Gsps,可以工作在多种模式下。通过对ADC工作模式进行配置,ADC既可以工作在采样率为5 Gsps的单通道模式,也可以工作在采样率为2.5 Gsps的双通道模式。模拟输入信号经过BALUN型高频变压器完成单端信号到差分信号的转换,ADC对差分信号进行采样,然后把数据送入FPGA,FPGA将接收到的数据进行预处理后存储到第三代双倍速率同步动态随机存储器(DDR3)中,需要对采集的数据进行后续处理时,将数据从DDR3中取出,并通过PCI Express传送给上位机,上位机对数据进行处理后显示。整个硬件系统仅采用一片FPGA来处理,并作为主控芯片对整个系统进行通信和控制,大大提高了系统的运行速度。本设计采用Xilinx公司Virrex-6系列FPGA,型号为XC6VLX240T-1156C。

2 系统的设计与实现

2.1 高速ADC设计及其完整性分析

高速ADC芯片EV8AQ160在片内集成了4路独立的ADC,每个通道具有1.25Gsps的采样率,可以工作在3种模式下,最高采样率可达5Gsps。要求2.5 GHz差分对称时钟输入,可进行ADC主复位。EV8AQ160内部集成了1:1和1:2的数据多路分离器(DMUX)和LVDS输出缓冲器,可以降低输出数据率,方便与多种类型的高速FPGA直接相连,实现高速率的数据存储和处理。为了补偿由于器件参数离散和传输路径差异所造成的采样数据误差,该ADC具有针对每路ADC数据的积分非线性(INL)、增益(Gain)、偏置(Offset)、相位(Phase)的控制和校正。EV8AQ160提供测试功能,具有两种测试方式,方便用户根据自己的习惯对ADC是否正常工作进行测试。

在本设计中,ADC工作在单通道模式下,DMUX1:2输出,输出数据宽度为64位,数据输出率为625 Msps,输出数据的同时输出312.5 MHz同步采样时钟,FPGA在该时钟的上升沿和下降沿采集数据。

由于探测器、信号源等输出的信号通常为单端信号,而ADC的模拟输入端为差分形式,在其前端加入BALUN型高频变压器,不仅实现了单端输入到差分输入的转换,还起到了隔离、抑制外部噪声引入等功能。

高速ADC的8路输出均属于高速数字信号,而其输入信号为模拟信号,因此在进行电路设计时,要考虑ADC的布局、模拟信号走线、数据信号走线以及其采样时钟走线,还有时钟布局和FPGA的接口等,确保所涉及的系统完全满足信号完整性的规范要求,如振铃、反射、串扰和电磁干扰等。

本设计使用Mentor Graphics的PADS软件对高速模数信号PCB板进行设计,根据上面提出的信号完整性和电磁兼容问题,并结合本设计的实际情况,主要进行如下设计:

1)合理布局:采用具有独立的地平面和电源层的多层电路板,并按照电路功能,对器件进行分块布局,模拟电路采用平面技术和网状屏蔽技术。

2)合理的信号走线:ADC的模拟输入信号走线旁边不能有别的走线,其输出的数据信号和时钟信号尽可能远离时钟电路模块,为保证采样时钟信号与数据信号同步,走线时让它们都经历相同的延迟,此外还能保证其时序的一致性,从而消除了走线延时对后端数据接收的影响。在布线条件允许范围内,输出的同一路数据信号线按照最短路径布线原则在同一电路层上走线,差分对与差分对之间的距离要尽量拉大,或者尽可能地减少相邻传输线间的累积平行距离,以减小串扰。时钟输入信号作为模拟信号处理,远离任何模拟输入和数字信号。

3)所有高速信号和时钟信号尽量走在内层。在获得相同目标特征阻抗的情况下,应该将布线层与参考平面(地平面与电源层)间的介质层尽可能的薄,这样就加大了传输线与参考平面间的耦合度,减少相邻传输线间的耦合。

2.2 采样时钟电路设计及其完整性分析

时钟信号的质量是决定采样系统性能的关键因素,也是高速数据采集系统的一个难点。反映时钟质量的指标主要有两个:相位噪声和相位抖动。在高速、高分辨率的ADC电路中,采样时钟的抖动必然造成时基采样点的偏离,从而导致系统整体性能的下降,主要表现在对ADC采集数据信噪比和有效位数的影响上。

采样时钟完整意义上的抖动应包含时钟源孔径抖动、时钟驱动器件的孔径抖动以及ADC自身的孔径抖动。ADC自身的孔径抖动是一个常数,通,嵩谄骷手册中作为一项重要指标给出,时钟驱动器件引入的时钟的孔径可以通过其器件手册和相位噪声倍频公式获得,时钟源抖动则与时钟稳定性和相位噪声参数有关。

如果ADC时钟总的孔径抖动的概率分布均值为0,方差为σ2(σ=tj,tj为ADC孔径时间)时,系统信噪比与孔径抖动关系可以表示为:

![]()

其中n为ADC转换位数,ω为ADC转换频率。

如果系统采样频率为5 GHz,转换位数为8位,希望得到的有效位数需要大于6位,则通过信噪比与有效位数关系式:

SNR=6.02xENOB+1.76 dB (2)

可得系统信噪比要大于37.88 dB,从而可以算出时钟抖动需要小于7.82 ps。采样频率越高,则时钟抖动需要的值就会越小。

本设计中,高速ADC芯片工作在单通道模式下,为满足EV8AQ160对高质量采样时钟的要求,这里采用低抖动、低相位噪声锁相环时钟芯片AD9520提供2.5GHz采样时钟。AD9520片内VCO可从2.27GHz调节到2.65GHz,还支持外部3.3V或5V供电,频率高达2.4GHz的VCO/VCXO。 AD9520支持SPI和I2C接口,片内集成一片EEPROM可通过串行接口编程以及保存用于上电复位的用户定义存储器的设置。有4组共12个LNPECL时钟输出,任何一个LVPECL输出在时钟频率不大于250 MHz时均可重新定义为2个CMOS输出,并且在上电时可自动同步所有的输出。AD9520的时钟抖动低至十数量级fs,最高为百数量级fs,可以满足本系统对采样时钟的要求。

为了减小时钟相位的抖动和采样时钟偏移,在时钟电路的PCB设计上还采用阻抗匹配的微带线和对称等长走线,防止高速时钟信号反射,提高时钟的信号质量。时钟信号的驱动电路采用差分PECL电路,PECL器件的电平转换速度快,输出信号抖动小,可以减小ADC时钟的孔径抖动。

2.3 高速ADC与FPGA接口设计

ADC输出8路8 bit 625 Msps低电压差分信号(LVDS)逻辑的数据,在采集系统设计中对与其接口器件的性能要求也较高。Xilinx公司Virtex-6系列型号为XC6VLX240T-1156C的FPGA具有高达200个专用LVDS差分逻辑接收通道,双数据率(DDR)LVDS通道发送数据速率高达1.25 Gbps,接收数据速率也高达1.0 Gbps,能够满足接收EV8AQ160输出数据和逻辑控制的要求。由于ADC的输出和FPGA的输入均设计为LVDS逻辑标准,因此ADC可直接与FPGA相连。Virtex-6系列FPGA内部具有专门的LVDS处理单元,可实现LVDS逻辑的串/并降速转换,降低速率后的数据给到内部分布式处理算法(DPA)单元进行精确处理后存储到内部的存储单元或者外部存储器件DDR3中。当需要对数据进行进一步处理时,通过PCI Express将有效的采集、存储数据发送到上位机,经过软件编程实现采集信号的波形显示。

2.4 上位机软件设计

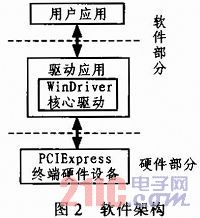

高速数据传输的上位机部分是以PC机为平台进行的软件设计。整个软件架构如图2所示,主要由用户应用程序和驱动程序两部分组成。

上位机系统通过PCI Express接口,控制板卡上的FPGA,并使上位机能够读取到FPGA以DMA方式连续上传的数据,实现上位机内存和FPGA之间数据的高速传输。该软件的驱动部分设计,依靠WinDriver的API函数和已有的PCI Express硬件设备驱动函数,完成对硬件设备的基本控制,为以后软件的进一步升级奠定良好的基础。而用户应用部分,主要是在Visual Studio环境中完成,通过调用可靠的设备驱动函数,成功地通过PCI Express接口与FPGA进行数据通信。

2.5 测试结果

1)ADC与时钟性能测试

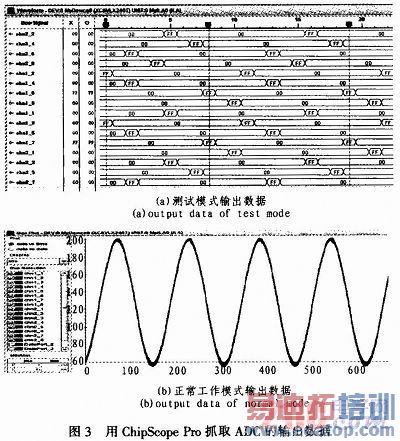

这里采用Xilinx公司ISE软件中的ChipScope Pro工具将逻辑分析器、总线分析器和虚拟I/O小型软件核直接插入到设计当中,直接查看ADC输出的数字信号,这些信号在操作系统速度下或接近操作系统速度下被采集,并从编程接口中引出,再将采集到的信号通过ChipScope Pro逻辑分析器进行分析。

首先让ADC工作在采样率为5 Gsps的单通道模式下,用特定的测试模式来检验ADC与FPGA之间的数据接口的准确性。将测试程序下载到FPGA并运行后,用ChipScopePro抓取ADC的输出数据如图3(a)所示。然后在单通道模式下不使用测试模式,输入2MHz的正弦信号,用ChipSco pePro抓取ADC的输出数据如图3(b)所示。

从图3(a)中的数据可以看出,各个通道均以约定的格式输出,说明ADC与FPGA之间数据接口已经准确连通。图3(b),输入正弦信号时用BUS PLOT工具将抓取到的数据实时画图,得到的波形平滑,计算其信噪比为42.9 dB,由式(2)计算得到ADC的有效位数为6.6 bit。实测表明,AD9520输出的2.5 GHz时钟以及EV8AQ160均具有较高的性能,整体指标达到设计要求。

2)上位机数据结果显示

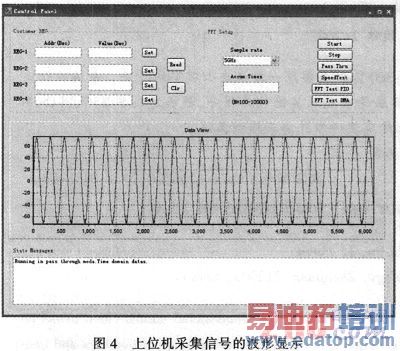

用户应用窗口程序的设计是在Visual Studio 2008环境下进行的,内部通过调用WinDriver提供的API函数及已编写的驱动函数,可以打开、查看、配置和关闭该PCI Express硬件设备。将系统配置为5 Gsps采样率的工作模式,用TeeChart画出实时采集到的波形,如图4所示,表明系统实现了数据的实时采集存储功能。

3 结束语

采用FPGA作为数据采集系统的控制核心,使用FPGA内部资源或者外部DDR3实现数据的缓冲存储,充分利用系统资源,便于调试和修改。实现了5 Gsps实时采样率、8 bits采样精度的高速实时数据采集系统。在完成电路的软件和硬件设计以后,通过对ADC和时钟进行测试以及上位机控制界面采集信号的波形显示,结果表明该系统可以稳定地工作,满足设计要求。

上一篇:用于雷达测试和验证的自动化测试设备

下一篇:气门综合检测系统的构成及特点