- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ADSP-TS201S的声雷达信号采集系统

在声雷达系统中,发射机定向发出不同频率的声信号,随后接收不同距离上的回波信号,利用回波中频率的偏离可以测定风速、风向随高度的变化。系统的多通道采样数据量接近500k×32b/s,一帧时间(约2.7s)内要求处理1100兆条指令,其大数据量和要求实时处理的特性对信号采集处理系统的设计提出了很高的要求,本文介绍的基于美国模拟器件公司的DSP ADSP-TS201S和ADC AD7864的信号采集系统能够满足这些要求。

系统的设计

1 系统功能模块划分

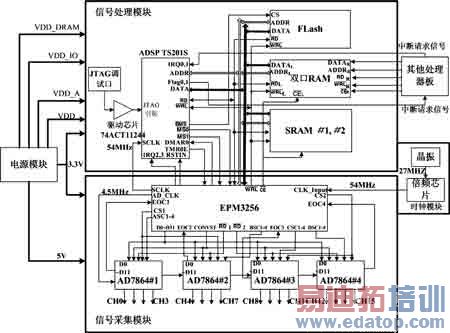

声雷达信号采集系统主要由信号采集、信号处理、电源和时钟四部分组成,如图1所示。信号采集模块由CPLD和4片ADC组成,负责完成A/D转换;转换后的数据送至信号处理模块,DSP ADSP-TS201S负责数据的接收和处理,两片512k×32b的SRAM完成了多帧数据的存储任务;一片双口RAM为ADSP-TS201S和其他处理器板交换信息提供了方便的接口,Flash用于存储用户的应用程序。电源模块为其他模块提供正常工作所需的电压。在时钟模块中,由晶振产生的27MHz时钟通过倍频芯片得到54MHz时钟后进入CPLD,它一方面作为ADSP-TS201S的系统时钟SCLK,另一方面在CPLD内12分频之后作为AD7864的工作时钟信号AD_CLK。

本系统之所以采用ADSP-TS201S芯片源于其强大的处理能力,可以对大量的回波数据作实时处理。它在600MHz的内核时钟下可以达到每秒48亿次乘累加(MAC)运算和每秒36亿次浮点运算(FLOP),具有比同类处理器高出50%~100%的处理能力。它内部集成了24Mb的存储器,这种片内大存储量与高达33.6Gb/s的内部带宽相结合,是提高性能的关键。其外部64位数据总线和32位地址总线时钟最高可达125MHz。

图1 信号采集系统电路图

声雷达系统中需要多通道同时采样,AD7864芯片的高速多通道和同时采样特性满足了系统的要求,简化了硬件设计,它的转换精度为12位,吞吐量最高可达520KSPS,单通道转换时间最快可达1.65μs,采样/保持时间为0.35μs。此外,其单电源和低功耗特性(最低可达20μW)也满足了系统的要求。

系统工作时,首先是由后端处理器板向ADSP-TS201S发出中断信号,通知TS201从双口RAM中读取命令字。根据命令字,TS201通过CPLD控制前端的ADC进行数据采集并利用DMA方式读取数据,处理好的数据存储于双口RAM中,TS201也通过中断方式来通知后端处理器板来读取数据并显示。

2 硬件电路设计

在时钟电路的设计中,晶振和倍频芯片的电源与本板电源之间要用电感或磁珠来隔离,防止它们对系统电源产生耦合干扰。为了抑制由电压波动引起的电流涌动和低频干扰,两者的电源引脚处要加上一个10μF的钽电容,0.1μF的用于抑制高频干扰的小电容也是必不可少的,而且要贴近管脚放置。此外,还应注意不要在时钟芯片底下走线,防止相互耦合干扰。倍频芯片输出端可以加一个33Ω的匹配电阻,以减少输出电流,提高时钟波形质量。为了减少EMI辐射和时钟抖动,要尽量减少过孔的使用。

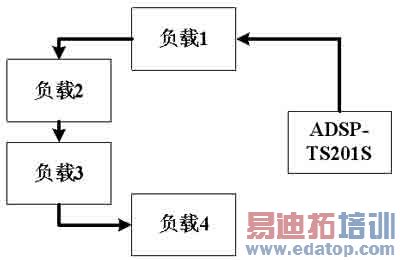

(a)环形结构

(b)星形结构

高频下总线的设计也是需要注意的,尤其是在系统中总线负载较重的情况下,不适当的设计会限制总线只能在低频下工作,甚至无法读取数据。由于环形结构上任一负载的变化都会影响到其他负载的工作,本设计中采用了星形总线结构,如图2所示。在布线过程中考虑到DSP总线的驱动能力,严格的将每根信号线的长度控制在6英寸左右。实践证明,采取的以上措施是必要而且正确的。

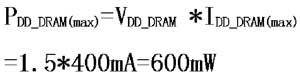

ADSP-TS201S和AD7864对电源的要求都非常高,例如,S201要求500MHz核时钟时,它的4个电源VDD、VDD_A、VDD_IO和VDD_DRAM的精度为±5%,因此,系统中采用了输出电压精度可达±1%的TPS54350作为电源芯片。

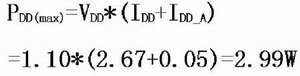

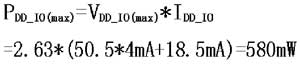

ADSP-TS201S的功耗可通过如下计算得到。以500MHz为例,VDD域消耗的电流可达2.67A,由式(1)可得,加上VDD_A的电流,内核最大功耗为 2.99W。

由式(2)可得,VDD_IO域上的最大功耗为580mW。

由式(3)可得,内部RAM的最大功耗为600mW。

基于以上数据,由式(4)可得,ADSP-TS201S在500MHz下的总功耗为4.17W。

(4)

(4)

ADSP-TS201S的功耗还是比较大的,因此在设计时要为散热片或风扇留出空间。电源部分的高频噪声会影响ADSP-TS201S的工作速度,尤其是电压低于1.5V的部分,所以在TS201的电源输入引脚附近要用低ESR的陶瓷贴片电容滤波,此外VREF和SCLK_VREF引脚也需要注意滤波。

由于系统是包括ADC的数模混合电路,设计中应注意以下问题。在AD7864和CPLD附近大面积的覆铜可以屏蔽外部对模拟信号的干扰,同时AD7864的电源引脚、参考电压输入引脚、VDRIVE引脚与模拟地之间要加0.1μF的贴片电容去耦;数字信号走线和模拟信号走线要分开布放;整板的数字地和模拟地要分开且保证单点相连,相连点选择在了模数信号汇集的地方;为AD7864供电的5V电源需要远离AD7864。

在调试过程中发现,如果不为ADSP-TS201S的JTAG口加驱动芯片,切入硬件仿真环境时Visual DSP会出错,所以建议即使是单片ADSP-TS201系统也要加一片驱动芯片,如TI公司的74ACT11244。

为了提高系统的灵活性,建议为ADSP-TS201S的SCLKRAT0~2(用于选择倍频系数)和DS0~2(用于选择总线驱动能力)引脚分别提供上拉和下拉两种选择,根据调试中的实际情况灵活配置。

3 软件实现

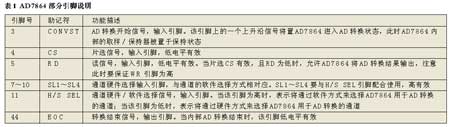

数据采集系统的软件设计部分包括CPLD的软件设计和DSP内部的程序代码。AD7864的一些输入引脚需要进行配置,完成这个任务的是Altera公司的CPLD产品MAX3256A。AD7864需要进行配置的各引脚的具体状态如表1所示。

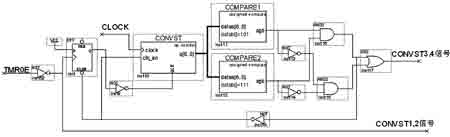

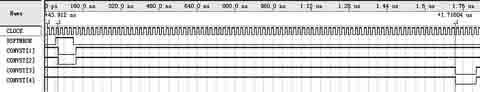

AD7864数据输出控制采取分时输出的方式。4片AD7864分为两组:1、2片一组,3、4片一组。采样信号来自于TS201的定时/计数器,每次定时器计数满时TMROE引脚上会产生4个总线时钟(SCLK,54MHz)的高电平,在CPLD里面把这个信号反向之后作为AD7864的CONVST信号。通过延时3、4片的CONVST信号可以控制两组AD7864分时工作,延时电路及仿真波形如图3所示。通过调节两个比较器的数值,可以产生符合系统需要的波形。

图3 CONVST延时电路及仿真波形

在数据传输上,1、3片的数据占据低位数据线,2、4片的数据占据高位数据线,分时输出防止了总线冲突的出现。由于AD7864-1是补码输出,因此DSP把数据读回后还需作数据提取和符号扩展处理。数据提取主要是把高低位的数据分开,符号扩展是根据采集回来的数据的第12位来判断数据的正负作不同的高位扩展,具体程序如下。

j0 = datum_out0;;

xr0 = [j0+=0];;//读取AD转换的数据

xr1 = 0xfff;;

xr2 = r0 and r1;;//提取AD转换的数据的第12位

xr3 = 0x800;;

xr4 = r2 and r3;;//判断符号位是否为1

if AEQ, jump data(np);;//如果符号位不为1,跳转

xr5 = 0xfffff000;;//如果符号位为1,高位扩展

xr6 = r5 or r2;;

xr2 = xr6;;//xr2里是扩展后的AD转换数据

data:

......//数据进一步处理

结语

经过测试,系统总线在54MHz时钟下正常工作,数据传输正确,在内核时钟432MHz下,圆满完成了数据处理及显示的任务(实际耗时1100M/432M约为2.55s,小于一帧时间)。目前本设计已成功应用于某声雷达信号采集系统。

上一篇:高速USB数据采集系统的设计

下一篇:数据采集的精度与分辨率考虑