- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

IC测试原理解析(第一部分)

本系列一共四章,下面是第一部分,主要讨论芯片开发和生产过程中的IC测试基本原理, 内容覆盖了基本的测试原理,影响测试决策的基本因素以及IC测试中的常用术语。

第一章 数字集成电路测试的基本原理

器件测试的主要目的是保证器件在恶劣的环境条件下能完全实现设计规格书所规定的功能及性能指标。用来完成这一功能的自动测试设备是由计算机控制的。 因此,测试工程师必须对计算机科学编程和操作系统有详细的认识。测试工程师必须清楚了解测试设备与器件之间的接口,懂得怎样模拟器件将来的电操作环境,这样器件被测试的条件类似于将来应用的环境。

首先有一点必须明确的是,测试成本是一个很重要的因素,关键目的之一就是帮助降低器件的生产成本。甚至在优化的条件下,测试成本有时能占到器件总体成本的40%左右。良品率和测试时间必须达到一个平衡, 以取得最好的成本效率。

第一节 不同测试目标的考虑

依照器件开发和制造阶段的不同,采用的工艺技术的不同,测试项目种类的不同以及待测器件的不同,测试技术可以分为很多种类。

器件开发阶段的测试包括:

特征分析:保证设计的正确性,决定器件的性能参数;

产品测试:确保器件的规格和功能正确的前提下减少测试时间提高成本效率

可靠性测试:保证器件能在规定的年限之内能正确工作;

来料检查:保证在系统生产过程中所有使用的器件都能满足它本身规格书要求,并能正确工作。

制造阶段的测试包括:

圆片测试:在圆片测试中,要让测试仪管脚与器件尽可能地靠近,保证电缆,测试仪和器件之间的阻抗匹配,以便于时序调整和矫正。因而探针卡的阻抗匹配和延时问题必须加以考虑。

封装测试:器件插座和测试头之间的电线引起的电感是芯片载体及封装测试的一个首要的考虑因素。

特征分析测试,包括门临界电压、多域临界电压、旁路电容、金属场临界电压、多层间电阻、金属多点接触电阻、扩散层电阻、 接触电阻以及FET寄生漏电等参数测试。

通常的工艺种类包括:

TTL

ECL

CMOS

NMOS

Others

通常的测试项目种类:

功能测试:真值表,算法向量生成。

直流参数测试:开路/短路测试,输出驱动电流测试,漏电电源测试,电源电流测试,转换电平测试等。

交流参数测试:传输延迟测试,建立保持时间测试,功能速度测试,存取时间测试,刷新/等待时间测试,上升/下降时间测试 。

第二节 直流参数测试

直流测试是基于欧姆定律的用来确定器件电参数的稳态测试方法。比如,漏电流测试就是在输入管脚施加电压,这使输入管脚与电源或地之间的电阻上有电流通过,然后测量其该管脚电流的测试。输出驱动电流测试就是在输出管脚上施加一定电流,然后测量该管脚与地或电源之间的电压差。

通常的DC测试包括 :

接触测试(短路-开路):这项测试保证测试接口与器件正常连接。接触测试通过测量输入输出管脚上保护二极管的自然压降来确定连接性。二级管上如果施加一个适当的正向偏置电流,二级管的压降将是0.7V左右,因此接触测试就可以由以下步骤来完成:

1.所有管脚设为0V,

2.待测管脚上施加正向偏置电流”I”,

3.测量由”I”引起的电压,

4.如果该电压小于0.1V,说明管脚短路,

5.如果电压大于1.0V,说明该管脚开路,

6.如果电压在0.1V和1.0V之间,说明该管脚正常连接。

漏电(IIL,IIH,IOZ):理想条件下,可以认为输入及三态输出管脚和地之间是开路的。但实际情况,它们之间为高电阻状态。它们之间的最大的电流就称为漏电流,或分别称为输入漏电流和输出三态漏电流。漏电流一般是由于器件内部和输入管脚之间的绝缘氧化膜在生产过程中太薄引起的,形成一种类似于短路的情形,导致电流通过。

三态输出漏电IOZ是当管脚状态为输出高阻状态时,在输出管脚使用VCC(VDD)或GND(VSS)驱动时测量得到的电流。三态输出漏电流的测试和输入漏电测试类似,不同的是待测器件必须被设置为三态输出状态

转换电平(VIL,VIH)。转换电平测量用来决定器件工作时VIL和VIH的实际值。(VIL是器件输入管脚从高变换到低状态时所需的最大电压值,相反,VIH是输入管脚从低变换到高的时候所需的最小电压值)。这些参数通常是通过反复运行常用的功能测试,同时升高(VIL)或降低(VIH)输入电压值来决定的。那个导致功能测试失效的临界电压值就是转换电平。这一参数加上保险量就是VIL或VIH规格。保险量代表了器件的抗噪声能力。

输出驱动电流(VOL,VOH,IOL,IOH)。输出驱动电流测试保证器件能在一定的电流负载下保持预定的输出电平。VOL和VOH规格用来保证器件在器件允许的噪声条件下所能驱动的多个器件输入管脚的能力。

电源消耗(ICC,IDD,IEE)。该项测试决定器件的电源消耗规格,也就是电源管脚在规定的电压条件下的最大电流消耗。电源消耗测试可分为静态电源消耗测试和动态电源消耗测试。静态电源消耗测试决定器件在空闲状态下时最大的电源消耗,而动态电源消耗测试决定器件工作时的最大电源消耗。

第三节 交流参数测试

交流参数测试测量器件晶体管转换状态时的时序关系。交流测试的目的是保证器件在正确的时间发生状态转换。输入端输入指定的输入边沿,特定时间后在输出端检测预期的状态转换。

常用的交流测试有传输延迟测试,建立和保持时间测试,以及频率测试等。

传输延迟测试是指在输入端产生一个状态(边沿)转换和导致相应的输出端的状态(边沿)转换之间的延迟时间。该时间从输入端的某一特定电压开始到输出端的某一特定电压结束。 一些更严格的时序测试还会包括以下的这些项目:

三态转换时间测试-

TLZ,THZ: 从输出使能关闭到输出三态完成的转换时间。

TZL,TZH: 从输出使能开始到输出有效数据的转换时间。

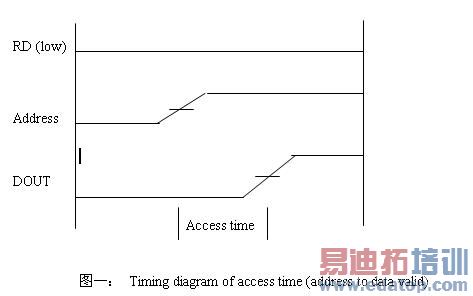

存储器读取时间-

从内存单元读取数据所需的时间。测试读取时间的步骤一般如下所示:

1.往单元A写入数据’0’,

2.往单元B写入数据’1’,

3.保持READ为使能状态并读取单元A的值,

4.地址转换到单元B,

5.转换时间就是从地址转换开始到数据变换之间的时间。

|

|

|

|

写入恢复时间 –在写操作之后的到能读取某一内存单元所必须等待的时间。

暂停时间- 内存单元所能保持它们状态的时间,本质上就是测量内存数据的保持时间。

刷新时间 – 刷新内存的最大允许时间

建立时间 - 输入数据转换必须提前锁定输入时钟的时间 。

保持时间 - 在锁定输入时钟之后输入数据必须保持的时间。

频率- 通过反复运行功能测试,同时改变测试周期,来测试器件运行的速度。周期和频率通常通过二进制搜索的办法来进行变化。频率测试的目的是找到器件所能运行的最快速度。

上面讨论了数字集成电路测试的一些基本目的和原理,同时也定义了测试上的一些关键术语,在接下来的章节里,我们将讨论怎么把这些基本原理应用到实际的IC测试中去。

参考文献:

Mark Burns, Gordon W。 Roberts

An Introduction to Mixed-Signal IC Test and Measurement Soft Test Inc。

Soft Test Inc。

The Fundamentals of Memory Test Methodology

The Fundamentals of Digital Semiconductor Testing

Anthony K。 Stevens

Introduction to Component Testing

Agilent Application Notes 1313

Agilent Application Notes 1314

许伟达

科利登系统有限公司

上一篇:IC测试原理解析(第二部分)

下一篇:电子电度表设计方案