- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用内部逻辑分析仪调试FPGA

推动FPGA调试技术改变的原因

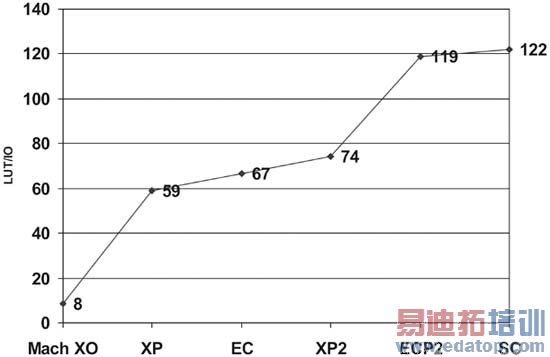

进行硬件设计的功能调试时,FPGA的再编程能力是关键的优点。CPLD和FPGA早期使用时,如果发现设计不能正常工作,工程师就使用“调试钩”的方法。先将要观察的FPGA内部信号引到引脚,然后用外部的逻辑分析仪捕获数据。然而当设计的复杂程度增加时,这个方法就不再适合了,其中有几个原因。第一是由于FPGA的功能增加了,而器件的引脚数目却缓慢地增长。因此,可用逻辑对I/O的比率减小了,参见图1。此外,设计很复杂时,通常完成设计后只有几个空余的引脚,或者根本就没有空余的引脚能用于调试。

图1 Lattice FPGA的LUT/可用I/O

第二,现在设计的复杂性经常需要观察许多信号,而不是几个信号。常用的技术是实现较宽的内部总线,以便在较大的FPGA中达到高的系统吞吐量。如果怀疑内部的32位总线里有坏的数据,则难以用几个I/O引脚来确定问题所在。

第三,通常需要在系统中测试复杂的功能。在这种情况下,在系统中调试时访问一些I/O也许是有限的。新类型的包还限制访问FPGA引脚。系统速度也是个问题,因为探针的连接可能会引起性能或者噪声信号降低。

最后,推动FPGA调试方法改变的关键因素是有了新的工具,这些工具采用内部或者嵌入式逻辑分析仪。

拥有这些工具可得到最佳的结果,而不是用与先前工具相同的方法。资源、静态参数和动态参数通常约束了内部逻辑分析仪和外部逻辑分析仪。本文对这两种类型工具的约束进行了比较,考察如何最佳地利用内部逻辑分析仪。

外部逻辑分析仪受到的限制

外部逻辑分析仪已经用了几十年了。外部逻辑分析仪的最大优点是能够存储大量的信号信息,或者用来跟踪数据。配置在不断变化,但大多数外部逻辑分析仪可以存储兆字节的数据。为了对FPGA使用外部逻辑分析仪,数据信号必须引到片外。可用两种方法中的一种来做。第一种方法是直接把信号送到用于观察的I/O引脚。取决于FPGA 的封装类型,接触I/O引脚 可能会有困难。 针对用这种方法进行调试的电路板 设计 要用连接器,例如与FPGA相连的MICTOR连接 器。然而这种方法不是很有效, 因为每个信号都需要一个I/O引脚。

第二种方法是插入能把信号引到I/O的核。这种方法的优点是这个核设计成能多路复用信号至I/O引脚,允许引脚共享。这种方法的局限是信号要被外部的逻辑分析仪实时捕获,多路复用大大降低了快速捕获信号的可能性。由于这个原因,通常使用2x 或者 4x多路复用方案。这意味着现在32 个I/O引脚可以支持64个或128个信号。这样得到了很大的改进,但是仍然有限制,例如要调试宽总线的情况。一旦信号连接到外部的逻辑分析仪,然后就设置触发和数据捕获条件。

使用外部逻辑分析仪设置的约束是有限的信号、高速触发逻辑和大量的跟踪存储器。大多数逻辑分析仪使用状态机触发机制。用户指定一个值等待这个信号,然后捕获这个数据,或者进入另一个状态,寻找不同的情况。这些信号本身是静态的,但各种情况是动态的,会在任何时候发生变化。给定约束后,这个方法很有效。因为限制了信号的数目,在信号组合的情况下减少了操作数。但是跟踪的存储器相对较大,试图找到一个接近的观察点是很普通的事,然后捕捉大量的数据以找到问题所在。

使用内部逻辑分析仪

用内部逻辑分析仪能与外部逻辑分析仪一样对FPGA进行功能调试。内部逻辑分析仪使用嵌入在FPGA设计中的一个或多个逻辑分析仪核。设计者使用PC在软件中设置触发条件,通过JTAG访问FPGA。一旦逻辑分析仪软核捕获了数据,通过JTAG将信息返回PC,然后设计者对这些数据进行观察。触发信号的复杂性和跟踪存储器的大小对信号数目有限制。大多数情况下,设计者可以观察成百上千个信号。

触发资源受FPGA限制,即未使用的逻辑和RAM。跟踪存储器有些实现需要RAM。有些则需要RAM或者LUT。然而,所需要的跟踪存储器比用外部逻辑分析仪大大减少,通常为数千位与数百万位之比。触发和数据捕获以设计的全速进行,因为信号不需要在FPGA片外复用。

用外部逻辑分析仪时,信号必须静态定义。改变信号经常需要FPGA再次执行,尽管有些工具提供只增加FPGA布线来改变部分或全部连接信号的能力。在调试期间,大多数实现部分或所有触发条件动态地改变。然而,触发的复杂性的变化取决于所用的工具。信号差别越多,所能提供的存储器就越小。为了获得最佳的结果,不同的触发选项驱动了使用内部逻辑分析仪的需要。

复杂调试的一个例子是在SMPTE SDI HD显示中寻找一个特别的像素。在特殊的情况下,找到EAV (end active video)时序是必须的,然后寻找与数据相关的特别线数,再寻找SAV (start active video)时序。最后根据线中对应的像素,计算字节数目,参见图2。

图2 SDI HD数据流实例

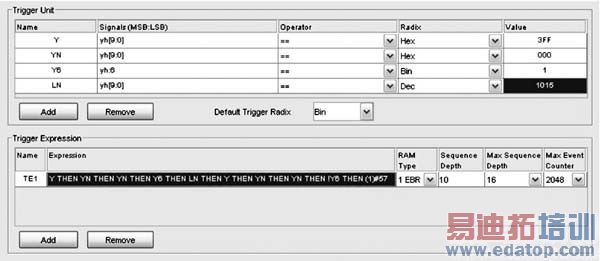

为了调试找到这种数据需要寻找值的时序,再找特殊值,然后结束序列,最后在捕获数据前数时钟的数目。为了理解是如何做的,必须查看具体的实现过程。莱迪思的Reveal硬件调试器使用触发单元和触发表示以决定触发点。触发单元是一个比较器,触发表示允许触发单元和序列值组合在一起。

对于这个SDI实例,用3个触发单元来定义EAV和SAV序列,另外的触发单元用于线数,最后在发现数据前的一个计数声明用于等待。触发建立的实例如图3所示。这个设置可以用来寻找任何要求的线数和像素,因为线数触发的值和计数可以动态地改变。

图3 触发设置的实例

结论

工程师将继续使用外部逻辑分析仪,因为用它分析系统级功能时是很有价值的。但是用于内部FPGA调试需要连接到电路板,信号的数目受到了限制。而内部逻辑分析仪在可用信号数目方面提供了很大的自由度,但是在触发逻辑和跟踪存储器方面受到约束。然而小心地使用触发选项使内部逻辑分析仪在精确的时间开始捕获数据,要最大化可用的资源。这个例子中,需要分析在SDI视频信号里特殊的像素(线和字)的复杂实现被分解成简单的元素,这种方法提高了效率。这个例子只是浏览了内部逻辑分析仪的使用和应用。由于FPGA设计复杂性不断增加,针对功能验证和调试,内部逻辑分析仪和类似的工具受到了设计者的青睐。