- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于时间一数字转换的精密时差测量系统设计

0 引 言

时差测量广泛应用于定位、测频、测时、测距等工程领域,例如:水声定位、无线传感器网络节点定位、雷达脉冲宽度测量等均对时差测量提出了高精度的要求。

目前,国内外的时差测量方法主要有直接计数法、模拟内插法和数字内插法。直接计数法虽然电路简单,量程大,但精度低,因此一般不单独采用。模拟内插法可以把计数法精度提高到皮秒量级,但由于基于电流的充放电技术,存在着线性度差、测量时间长、受温度影响较大和电磁辐射大等问题。作为数字内插法的一种,时间一数字转换法因其具有测量精度高、速度快等优点而受到国内外的普遍重视。

TDC—GPl是德国ACAM公司生产的通用时间一数字转换芯片,单通道测量精度为125 ps,双通道精度可达250 ps,具有多种工作量程和工作模式。这里设计了基于时间一数字转换器TDC—GPl和D889C450的单通道高精度时差测量系统,实现纳秒级的时差测量。

1 TDC时差测量原理

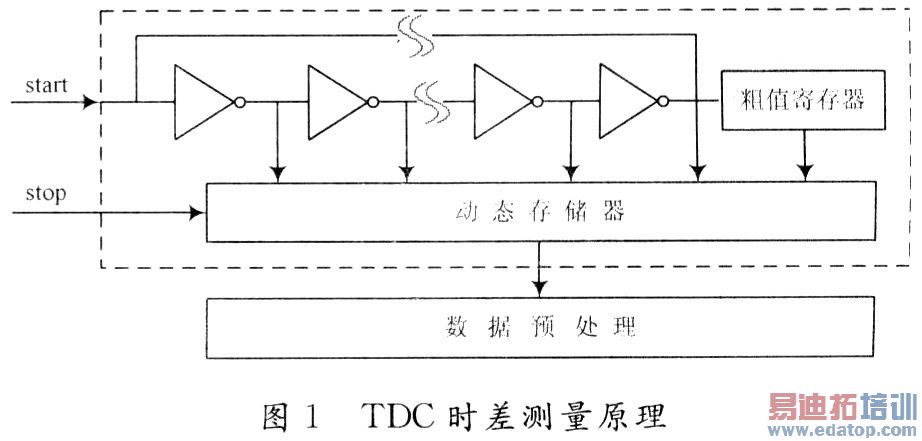

时间一数字转换(TDC)技术是利用信号通过逻辑门电路的绝对传输时间提出的一种新的时间间隔测量方法,测量原理如图1所示。start信号和stop信号之间的时间间隔由非门的个数来决定,而非门的传输时间可以由集成电路工艺精确地确定。目前的CMOS工艺可以很容易实现102ps量级的门延迟时间,因而可以实现精密时间测量。

TDC—GPl是德国ACAM公司基于0.8μm CMOS工艺设计的一种通用型双通道时间一数字转换芯片,支持两个工作量程,多工作模式,工作方式灵活。可精确测量时间、相位、频率等物理量。主要技术特性如下:

(1)双通道250 ps分辨率或单通道125 ps分辨率;

(2)每个通道可进行4次采样,排序可达8次采样;

(3)两个通道的分辨率完全相同,双脉冲分辨率大约为15 ns;

(4)可再次触发性两个测量范围:3 ns~7.6μs和60 ns~200 ms(需要前置配器,只能用单通道);

(5)双通道的8个事件可任意测量,没有最小时间间隔限制,时间间隔有可能是负值;

(6)分辨率调节模式:通过软件可对分辨率进行适应精确性调节;

(7)内部最多可存储4个校正值或8个非校正值,校正和控制时钟的频率在500 kHz~350 MHz之间(采用内部前置配器其频 率最高可达100 MHz);

(8)工作电压:2.7~5.5 V,极低的功耗,可用电池驱动。

2 系统硬件设计

2.1 系统总体设计

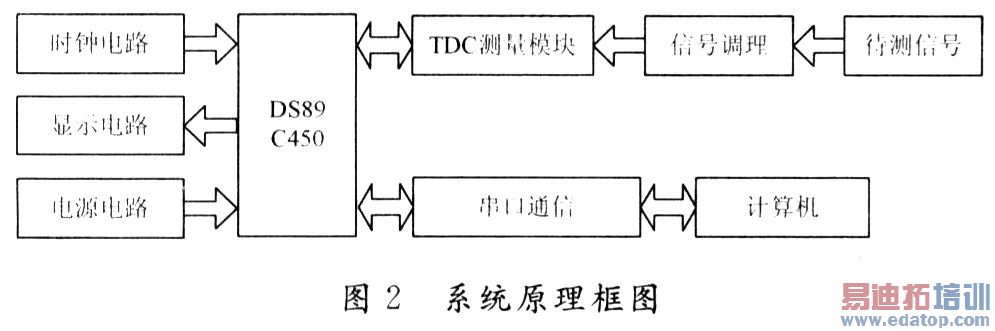

时差测量系统原理框图如图2所示。

当系统上电后,通过DS89C450单片机对TDC—GPl芯片进行工作通道、工作模式选择等初始化操作。当接收到经信号调理后的时差信号后,TDC—GPl按照预先的设置开始工作并将测量的结果存储在相应的结果寄存器中。当测量结束后,单片机读取测量结果并按照量程2中的时差计算公式完成相关的数据处理及显示等功能。

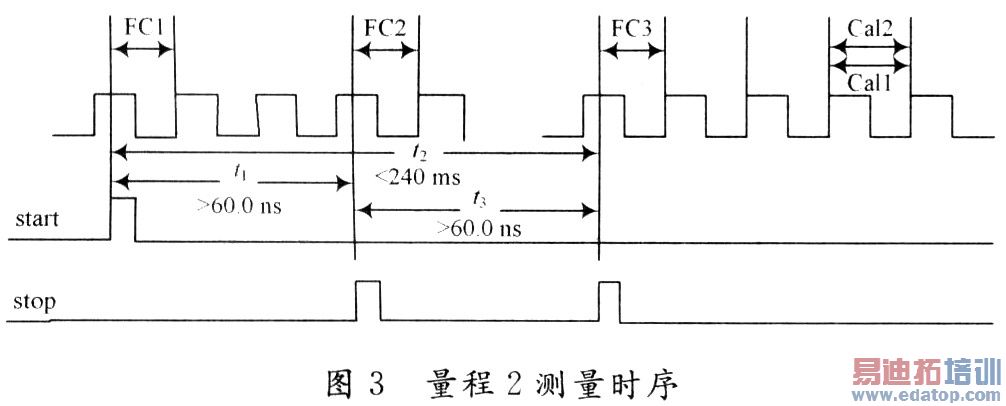

在该系统中,主要采用TDC—GPl的量程2进行设计。其测量时序如图3所示。

在量程2中启用了前置粗计数器,测量范围在60 ns~200 ms之间,可测量多个停止信号与起始信号之间的时差,对结果进行乘法运算,不能直接计算停止信号之间的时差,只能给出校准结果,因此寄存器0中的校验位必须被设置。

测量时间差计算公式为:

![]()

其中cc为前置粗计数器的计数值,period表示校准时钟周期。

2.2 微处理器电路

系统中采用MAXIM公司的超高速闪存微控制器DS89C450,它兼容于8051的引脚和指令系统,30 ns单指令周期,Dc~33 MHz工作频率,适合于微型化系统的设计。DS89C450是硬件系统的核心,用于完成对GPl的控制操作和与计算机进行通信等功能。由于GPl提供了8位数据总线和4位地址总线接口,操作时序符合通用微处理器的总线操作时序,使得GPl可作为DS89C450的外围电路。

2.3 前置调理电路

输入GPl的start/stop的脉冲信号边沿对测量结果有重要的影响,因此通过带施密特触发器的逻辑门电路和滤波电路对待测脉冲信号进行隔离、缓冲及滤波。这样不但去掉了毛刺,而且改善了波形的边沿,从而提高时间差的测量精度。

2.4 电源设计

由于TDC—GPl是一个不含模拟元件的完全数字化器件,利用了非门电路延迟实现时间测量,而门电路的传输时间对环境(温度和外加电源电压)的影响比较大,所以要取得高测量精度就必须保证高稳定的电源供应。该系统采用高效率、低静态输出电流、降压型开关电源模块MAX639,并且在硬件电路上放置了适当的低阻抗和低阻值的去藕电容,在电路的制作上采用独立的电源层和地层,以提高线路的抗干扰能力,保证系统的测试精度。

3 系统软件设计

3.1 系统主程序

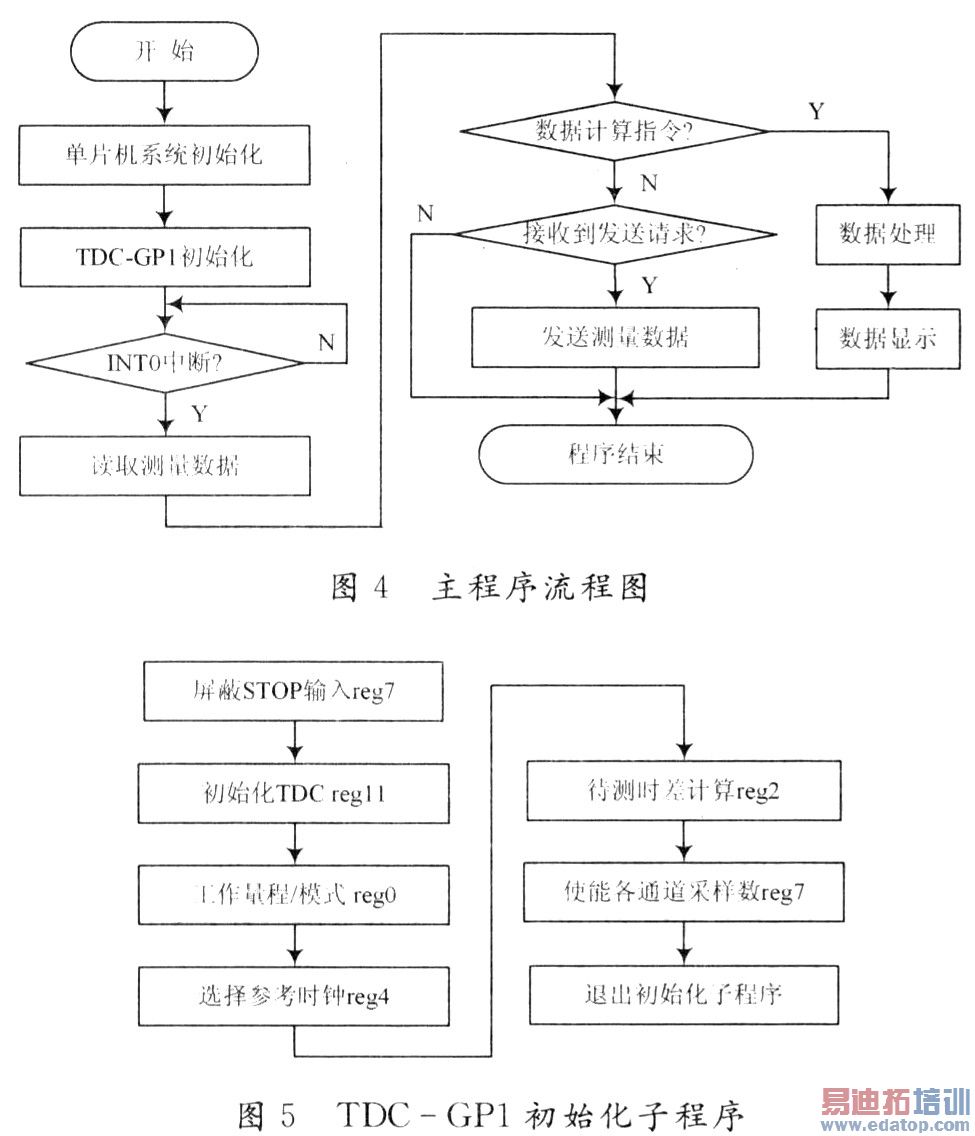

系统软件设计主要采用Ds89C450的汇编语言实现。主程序完成的主要工作是:单片机系统的初始化,TDC—GPl模块初始化和工作模式的选择设置,串口通信程序、数据的处理、显示和传输等,其中单片机与上位机的通信采用查询方式。主程序流程图如图4所示。

3.2 TDC子程序

对TDC—GPl的初始化子程序流程图如图5所示。置TDc芯片于写工作状态后,开始对TDC—GPl进行写操作。通过赋值控制寄存器7屏蔽所有的SToP输入信号;接着,写控制寄存器11,初始化TDC和ALU;然后,指针指向控制寄存器0,使芯片工作于量程2,自校准模式,无数乘功能;再写控制寄存器4,选择参考时钟SEL—TDC—CLK;再写控制寄存器2,令通道2第1个脉冲上升沿与通道1第1个脉冲上升沿作差;最后,通过写控制寄存器7,取消2个通道对STOP输入信号的屏蔽,允许多次采样。在测量中,各个寄存器的设置如下:reg7=00H,regll=07H,regO=78H,reg4=40H,reg2=2lH,reg7=04H。

当单片机查询到TDC—GPl芯片输出的中断信号后,程序进入中断服务子程序。置TDC芯片于读工作状态,单片机开始对进行内部结果寄存器数据的读出操作。通过选定起始地址可读出多重数据并能连续不断地进行读操作,最后根据设置完成测试数据的计算、处理、显示及传输等功能。

4 试验数据及分析

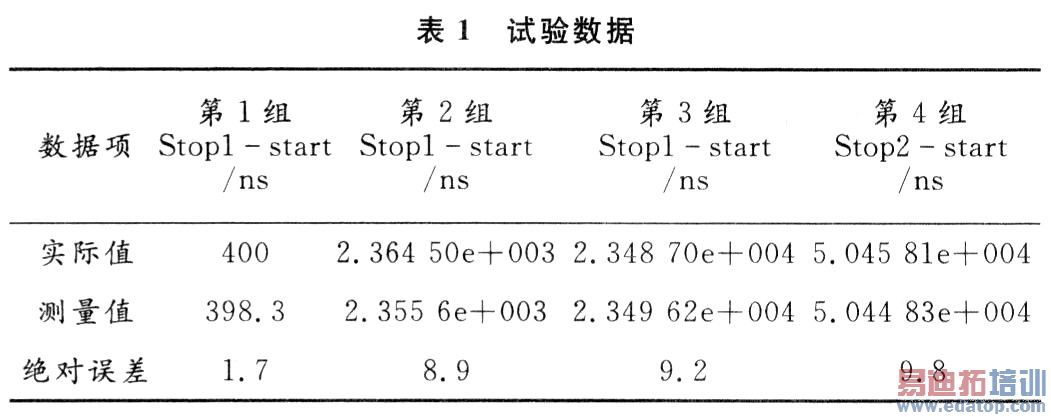

系统工作在室温25℃,5.03 V电压条件下,通过对CPLD信号发生电路产生的数字脉冲信号间隔进行实际测量,以验证系统工作性能。分别对单个(第1组及第2组)和多个(第3组和第4组)不同的脉冲宽度进行测量,并计算其绝对误差。测量数据如表1所示。

通过对表1分析得出,测量结果保持了的测试稳定度和测量精度,基本实现了精密时差测量的功能。但仍然存在一定的时间测量误差。另外,经过对相同时差多次测量发现,测量结果有一定的波动,主要原因是时间测量模块是采用内插延时线法测量的,在工作时间过长或外界温差较大时会产生热效应,导致延时链受温度影响而延长时间变化,采用高精度的系统工作电压和恒温措施可稳定延时线延时常数,进一步提高测量精度。

5 结 语

设计基于TDC—GPl和DS89C450单片机的精密时差测量系统,通过对测量数据的分析表明,系统实现了纳秒级的时间间隔测量,同时系统具有性能稳定、精度高、节能等有优点,因而在无线定位、测时、遥控遥测、激光测距、电子测量仪器等领域具有广阔的应用前景。