- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

NAND FLASU在储存测试系统中的应用

摘要:主要介绍了三星公司的NAND FIJASH存储器K9K8G08UOM、以FPGA为核心模块控制K9K8G08UOM的读操作、写操作和擦除操作,以及FLASH储存器在硬件设计中的具体接法。经实际电路测量验证了其功能的正确性。

关键词:NAND FLASH:K9K8G08UOM:FPGA:读操作

0 引言

计算机技术的高速发展,存储系统容量从过去的几KB存储空间,到现在的T8;乃至不久的将来要达到的PB存储空间,其数据存取的能力在飞速扩展。随之而来产生的SCSI、FC、SAN、iSCSI、IPStorage和数据生命周期管理等崭新的领域,更给计算机技术和网络技术赋予了蓬勃的生命力。存数性能的提升通常是通过在基础结构上增加更多的物理磁盘驱动数目或者采用更快转速的磁盘驱动器来完成。

机载存储设备要求具有高的可靠性和高抗撞击、抗震、防潮、耐高压和承受高温的特点,而磁盘驱动器存取数据时有机械转动,其抗冲击,抗震动性不强,所以不适用于航空航天等恶劣环境下使用。基于半导体存储芯片闪存的固态存储器(SSD)的出现很好的解决了以上问题。SSD作为储存介质,没有机械转动部件、存储密度高、可靠性高、体积小、重量轻,并且抗震动、抗冲击、温度适应范围宽,具有很强的环境适应性,可以满足苛刻条件下的数据储存要求,因此,高性能大容量固态存储器已成为军用重大项目中的只要数据储存方式。

1 NAND FLASH Memory的控制要求

1.1 NAND FLASI-1存储器结构功能介绍

我们选用的是三星公司的K9K8G08UOM型FLASH芯片作为存储系统的介质,该款NAND F1ash存储容量为8448Mbit,其中主数据区为8192M bit,辅助数据区为256Mbit,工作电压为2.7V~3.6V,I/O端口的宽度为8位。NAND FLASH不同于NOR FLASH,NOR FLASH在出厂时不容许芯片有坏块存在,而NAND FLASH容许成品中存在坏块,这是NAND技术所特有的现象。

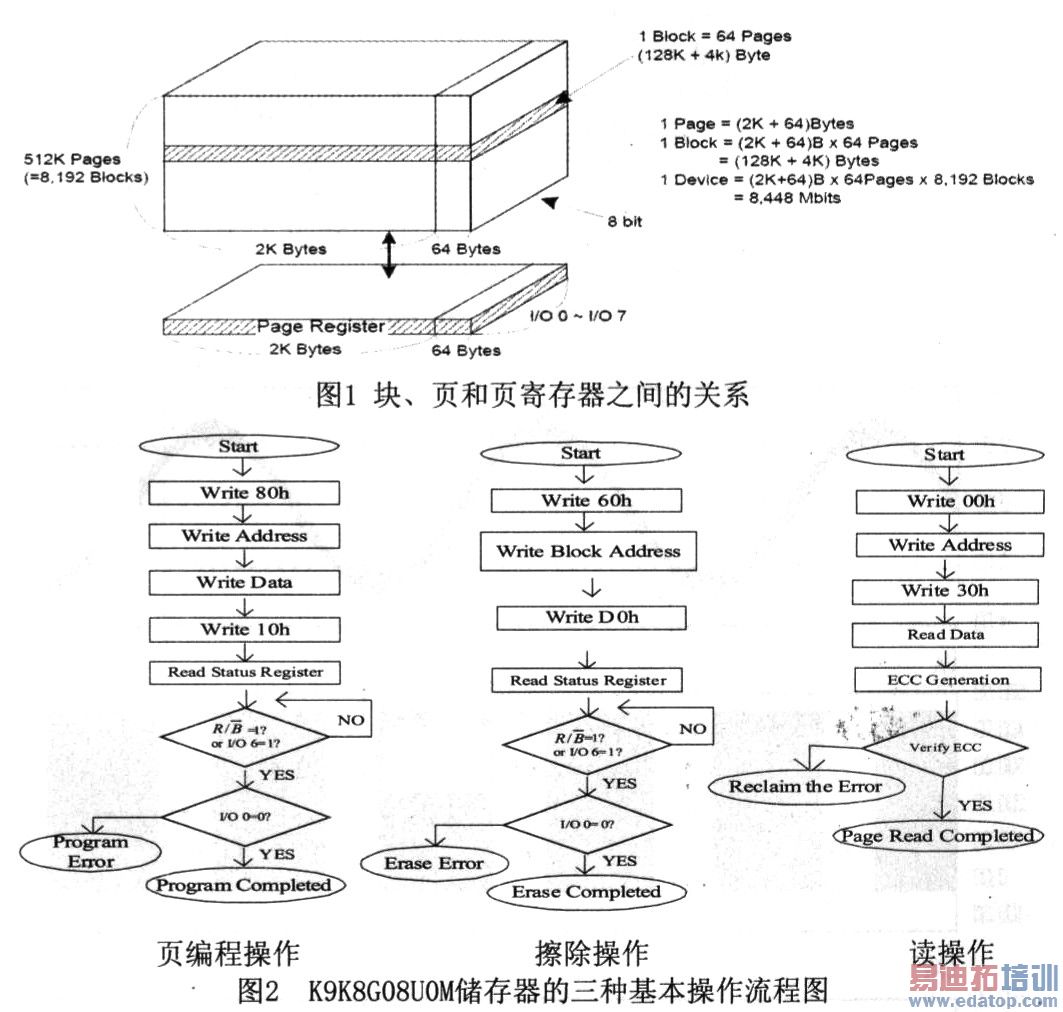

芯片内的8448M bit内存是按块和页的概念来组织的,一个FLASH存储器包含8192块(block),每块包含64页(page),每页有2112 Bytes。芯片内具有一个容量为2112 Bytes的数据寄存器,称为页寄存器,用来在数据存取时作为缓冲区,当对芯片内的某一页进行读写时,其数据首选被转移到此数据寄存器内,通过数据缓冲区和芯片外进行数据交换,以完成读写功能。页内的2112Bytes被划分为2048 Bytes的主数据区和164 Bytes的辅助数据区,主数据区存放用户数据,辅助数据区被用来储存ECC(Error correction Code,错误校验码)、坏块信息和文件系统相关代码。其组织关系如图1所示:

K9K8GOSUOM地址是通过复用8个I/O口送入芯片的。这样的设计显著减少了芯片的管脚数目,并为系统升级带来了方便。在CE和WP为低时,把WE置低可以把K9K8G08UOM的命令、地址和数据通过I/O口写进去。数据在WE的上升沿写入芯片。命令锁存使能(CLE)和地址使能锁存(ALE)用来区分I/O口的数据是命令还是地址。K9K8G08UOM有1G字节地址空间,需要30位的地址,所以字节的地址需要五个周期依次送入:行低地址、行高地址、列低地址、列中地址、列高地址。页的读操作和编程操作都需要同样的五个地址周期紧跟在相应的命令输入之后。然而,在块的擦除操作中,只要有三个地址周期。不同的操作通过往命令寄存器写不同的命令来区分。

1.2 K9K8G08UOM控制器技术

本系统中采用FPGA作为K9K8G08UOM存储器的控制器,可以在极少的软件操作下独立完成K9K8G08UOM的各种操作,从而降低系统对FLASH存储器的额外支出,提高读写速度。FPGA的控制逻辑时序是通过硬件语言VHDL开发的,VHDL语言以其快捷、独立、可读性等优点很好的完成FLASH基本操作的时序控制。下面是以VHDL语言以状态机的形式开发的部分读操作程序。

K9K8G08UOM储存器的基本操作由三种类型:读操作、页编程操作、擦除操作,其流程图如图2所示。

进行读操作时,首先通过FPGA的端口置低K9K8G08UJOM的片选信号/CS,然后置高CLE命令脚,并发送read1(0x00)命令,WE的上升沿发送,命令发送完毕后,置低CLE。在发送地址之前,置高ALE,在每一个WE上升沿依次写入5个地址周期,之后置低ALE,完成地址的选定。接着发送read2(0x30h),开始读取地址单元的数据。

数据页编程操作和读取操作流程类似。操作都是以页为单位进行的。当R/Bur信号为低时,说明正在对FALSH进行写入操作,当为高时,说明页编程操作结束。

擦除操作是以块为单位进行的,即一次擦除块内的64页,在发送地址时只需要3个地址周期。

图3是从K9K8G08UOM存储器中存入数据以后通过上位机软件读取的数据。经验证,读取的数据与往K9K8G08UOM存储器中写入的数据一致。

2 NAND FLASkI Memory的硬件部分

本设计当中,FLASH的数据输入输出口、控制端口通过调理电路与FPGA的端口相连,图4所示是其硬件连接电路。

从图4中可知,FLASH的数据输入输出端口I/00~7、控制端口/CE、是通过芯片SN54LV245与FPGA相连;FLASH的控制端口cLE、ALE、/WE、/RE通过芯片SN54LV245和芯片74HCl4与ITGA相连。其中F-CLE、F-ALE、F—WE、F-RE、F—CE、F-R/Bur是FPGA的I/O口,是FPGA逻辑的输入输出口。CLE、ALE信号是FLASH存储器命令、地址锁存使能信号,/WE是保证命令、地址、数据能否及时正确的写入FLASH的信号,/RE信号控制着数据的读取,这些信号的精确度关系着FLASH存储、读数功能的实现。所以,这些信号的好坏直接关系着FLASH的正常工作。经实践的电路调试,这些信号在传输过程中受到了其它因素的干扰,信号明显失真,在电路中加入74HCl4(非门)以后,信号会变得光滑,准确。

芯片SN54LV245是八进制三态总线收发器,DIR=1时,总线传输方向从A→B;DIR=0时,总线传输方向从B→A。/OE是片选信号。/0E,DIR信号是由FPGA内部编程逻辑控制的。

FL,ASH接口中,为了保证/wE、/RE、/CE、R/B控制信号初始状态无效,由硬件电路实现端口值拉高。本设计中不使用写保护功能,所以/WP端口也接上了上拉电阻。

3 结束语

基于闪存技术的固态存储器存储密度大,功耗小,可靠性高,体积小重量轻且成本也在不断降f氐,在航空应用中有良好的应用前景。在设计储存测试系统时选用大容量的NAIXD FLASH存储器大大提高了储存、读取速度,并且设计电路结构简单,易于修改。

上一篇:一种基于d-q变换的谐波电流检测方法

下一篇:VoIP声学回声消除算法研究