- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3测试的挑战及解决方法

前言

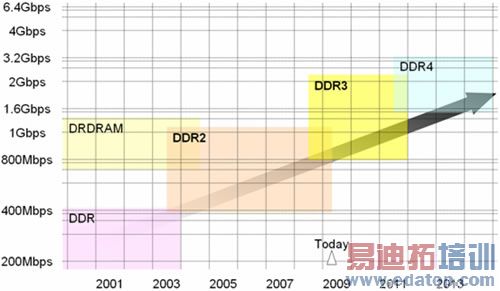

作为DDR2的继任者,根据JEDEC标准, 目前DDR3的数据速率跨度从800Mbps开始直至1.6Gbps。在带给用户更快性能体验的同时, DDR3却能保持较低的功耗,相比DDR2减少约20%。虽然2008年整个DRAM市场低迷,DDR3的出货量远低于原先的预期,但是随着Intel和 AMD相继推出DDR3平台的处理器,以及移动式平台的推广,DDR3代替DDR2成为主导将是今后的必然趋势。

价格也是DDR3平台是否能早日推广的重要因素之一,这也给各存储器厂商带来了不小的成本压力。高效、低成本的测试方案将是关注的重点。同时,由于速度的提高,测试平台必须提供更高的测试频率来验证DDR3芯片的可靠性,以及更精确的手段来进行时间参数的测量。

DDR3测试的挑战

•更高的工作频率

根据JEDEC的相关标准, DDR3的数据速率高达1.6Gbps。随着DDR技术的飞快发展,市场上甚至出现了2Gbps的DDR3模组。此外,为了实现更高的速率和更低的功耗,DDR3采用了更低的电压,仅为1.5V。在高频率和低电压的条件下对DDR3进行测试,信号完整性的好坏至关重要,同时也对测试设备的性能提出了更苛刻的要求。

图 1 DDR3的数据速率范围

•I/O死区

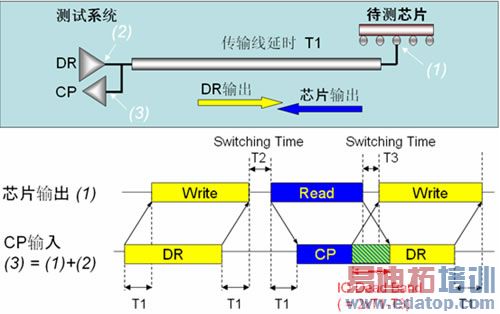

信号在传播的过程中存在一定的延时。写数据时,测试通道提前将数据输出,以保证其在预定时刻到达芯片管脚;读数据时,测试通道延迟触发采样信号,延迟的时间为信号传输延迟。在STL(Single Termination Line)连接方式下,由于测试周期的缩短,信号传播延时将变得不可忽视。在这种情况下,测试通道的输出与芯片的输出信号将会发生重叠,重叠的时间区域称为I/O Dead Band。

图 2 I/O Dead Band

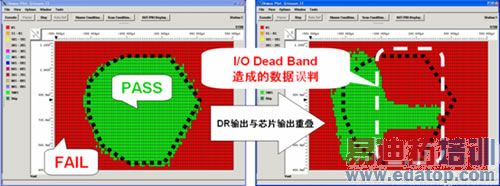

对比DQ信号的SHMOO眼图,可以清楚看到I/O Dead Band使得数据窗口的高度和宽度减小,原本PASS的区域变成FAIL,从而造成数据误判。

图 3 I/O Dead Band造成数据窗口缩小

•不可忽视的信号抖动(jitter)

随着数据速率的提高,数据周期的宽度将不大于1.25ns,甚至达到0.625ns。由于jitter的大小相对与周期宽度变得不可忽视,时间参数测试变得更加困难。此外,jitter还会造成有效数据窗口的缩小,造成信号的误判。因此,测试设备应能提供一种精确、高效的时间参数测量手段,以应对 jitter带来的不利影响。

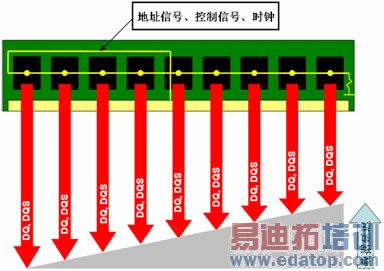

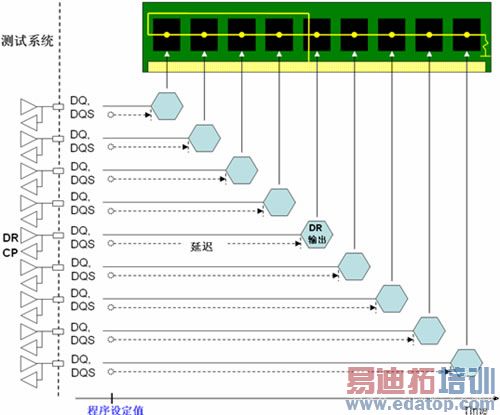

•Fly-by拓扑结构

为了改善信号完整性,DDR3内存模组采用了Fly-by拓扑结构。模组上的DDR3芯片共享一组CLK管脚、地址管脚和控制管脚。由于信号传播延迟的存在,模组上的DDR3芯片会在不同时刻进行数据的输入/输出。在进行模组测试时,测试设备应具备对不同测试通道进行时间补偿的能力。

图 4 Fly-by拓扑结构带来的信号延迟

DDR3测试的解决方案

针对DDR3测试所面临的特点和挑战,爱德万测试推出了高性能的T5503测试系统。

•提供更高的测试频率

系统可以提供高达3.2Gbps的数据速率, 并且能够通过更换HSPE(High Speed Pin Electronics)来进一步提升数据速率至4.0Gbps,完全覆盖了DDR3以及DDR4的速率范围。

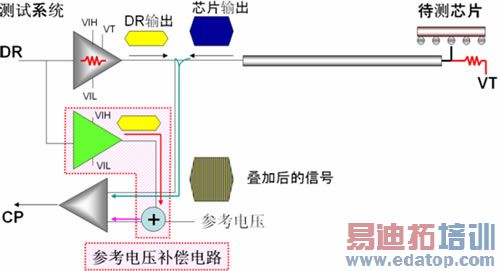

•提供I/O Dead Band Canceller功能(消除I/O死区)

I/O Dead Band Canceller功能可以解决I/O死区问题。系统中的测试通道配备了参考电压补偿电路。该电路可以根据DR输出的变化,实时地对参考电压进行补偿,保证了数据判断的可靠性,从而克服I/O Dead Band带来的不利影响。

图 5 T5503的I/O Dead Band Canceller功能

•提供Multi-Scan Strobe功能(强大的时间参数测量能力)

系统提供了Multi-Scan Strobe功能, 通过对芯片输出信号进行连续采样,记录并计算采样时的PASS/FAIL分界点。采用Multi-Scan Strobe功能所带来的好处是,在一个测试周期中可以连续触发多个采样信号,只需单次运行测试向量就可以获得PASS到FAIL以及FAIL到PASS 的转换点(即得目标时间点的具体数值)。相比以往业界常用的边界扫描方式(同一个测试周期触发一个采样信号,通过不断改变采样信号的时间,反复运行测试向量来寻找PASS/FAIL的转换点), Multi-Scan Strobe功能大大节约了时间参数测试的时间。通过以下几个参数测试的示例,本文将对Multi-Scan Strobe功能进行简要介绍。

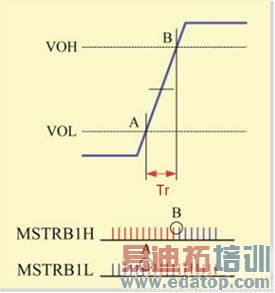

1. 测量Tr/Tf

图 6 Multi-Scan Strobe功能——测量Tr/Tf

以信号的上升时间(Tr)为例,Tr定义为:信号的上升沿上,电压为幅度的20%(VOL)和80%(VOH)的两个点的时间间距。在一组采样序列中,序列MSTRB1H存储了输入信号与VOH比较的结果(PASS/FAIL),序列MSTRB1L存储了输入信号与VOL比较的结果(PASS /FAIL)。在两个序列中,分别找出PASS/FAIL的分界点A,B。通过计算A,B间的时间差,可以得到Tr的值。

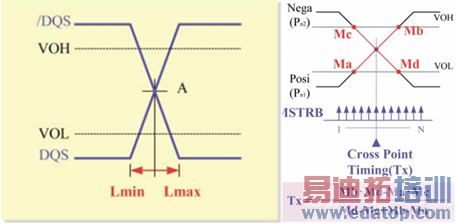

2. 测量Cross-point Timing

DDR3的CLK和DQS均采用差分信号。差分信号的交点(cross-point)定义了数据周期宽度。采用与测量Tr/Tf相同的方法,在一对差分信号的两个通道上分别进行测量,得到下图中四个参考点(Ma, Mb, Mc, Md)的出现时间。然后,借助公式可以计算出cross-point的位置(Tx)。

图 7 Multi-Scan Strobe功能——测量Cross-Point的出现时间

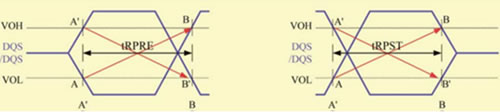

3. 测量Preamble/Postamble Timing

对于DDR3芯片,在DQ管脚输出数据之前,DQS信号会提前一段时间由高阻态变为低电平,这段时间为tRPRE;DQ完成数据传输之后,DQS信号会继续维持一段时间的低电平,再变为到高阻态,这段时间称为tRPST。

图 8 Multi-Scan Strobe 功能——测量Preamble/Postamble时间

以DQS信号为例,tRPRE可以表示为A点到B点之间的距离,tRPST可以表示为A’点到B’点之间的距离。与Tr/Tf的测试类似, Multi-Scan Strobe功能可以方便地得到测试结果。

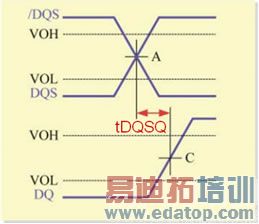

4. 测量 tDQSQ和Jitter分布

tDQSQ定义为DQS差分对的cross-point到 DQ输出的时间延迟。以往对于tDQSQ这一参数的Margin测试,通常采用调整采样信号时间沿,反复扫描的方式。这种方式的测试时间相对较长。下图是 tDQSQ的示意图,图中A点和C点之间的时间延迟就是tDQSQ。

图 9 Multi-Scan Strobe 功能——测量tDQSQ

参考前文中Preamble/Postamble Timing的测试方法, Multi-Scan Strobe 功能可以很容易地获得A点和C点的时间延迟。除了测试效率以外,测试结果的精确度也是我们必须考虑的。由于tDQSQ参数考量的是DQ的输出和DQS的输出在时序上的关系,其数值受到DQ和DQS jitter的影响。在信号频率较低,数据周期较宽的情况下, jitter的影响可以忽略,直接计算A点到C点的距离就可以得出tDQSQ。但是随着数据周期的减小,A点和C点出现位置的抖动变得不可忽略,jitter对数据窗口宽度的影响日益显著,给tDQSQ的测试带来了困难。

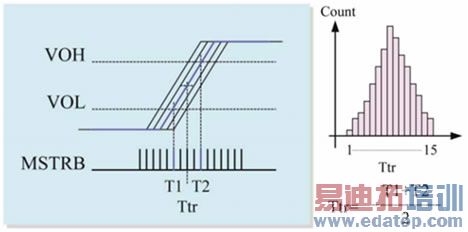

图 10 Multi-Scan Strobe 功能——测量Jitter

为了克服jitter带来的不利影响,Multi-Scan Strobe功对芯片输出信号的多个周期的进行采样,记录每次采样的结果(如信号的50%点,Ttr),并得到其正态分布。上图右下角,取Ttr分布最高处的点为DQ的50%点。同样,DQS差分对的cross-point也取分布最高处的时间点。此时,tDQSQ可以表示为两个分布最高点处的时间差。

•提供Per-Pin Offset功能(对Fly-by结构进行时间补偿)

系统提供了Per-Pin Offset功能,它可以灵活调整测试通道中波形产生的时间以及数据比较的时间,从而补偿Fly-by结构带来的延时。

图 11 T5503的Per-Pin Offset功能

•提供128 DUT/SYS的并行测试能力

根据ITRS的预测,随着测试频率的增长,由于测试接口布线复杂性的提高,在一个测试头(STN)上实现128DUT并行测试将是一个挑战。T5503配备有一个测试头,具备128DUT/STN的测试能力,可以有效提高测试效率、降低测试成本。

•具有多Site、低功耗、体积小的特点

系统的测试头由两个Site构成,每个Site可独立工作,允许多个用户同时使用同一系统。此外,得益于先进的系统集成技术,系统的体积和功耗削减了40%左右。

图 12 T5503的外观

总结

ADVANTEST的T5503系统可以满足用户对DDR3高速测试的需求。

ADVANTEST在存储器测试方面拥有着丰富的经验,一直致力于为客户提供优质、高效的解决方案。ADVANTEST专注于生产高品质的测试系统,针对客户需求和市场变化不断地推出有竞争力的产品,帮助客户解决研发和生产中遇到的问题。

上一篇:数字电视及其测量浅谈

下一篇:基于单片机的炭黑复合导电材料的电阻一温度测量系统