- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ARM9的高速数据采集系统的实现

摘要:随着雷达、通信、遥测、遥感等技术应用领域的不断扩展,人们对数据采集系统的采集精度、采集速度、存储量等

都提出了更高的要求。针对当前数据采集系统的缺点,提出了基于ARM9的数据采集系统的设计。详细论述了信号调理,时钟产生,数据存储与传输,抗干扰等关键技术及采取的相应措施。经实践证明,该设计方案具有采集精度高,数据采集速度快,数据存储量大的优点。

关键词:高速数据采集系统;ARM;模/数转换器;数据处理

l 引 言

在科研、生产和人们的日常生活中,模拟量的测量和控制是很常见的。为了对温度、压力、流量、速度、位移等物理量进行测量和控制,通过传感器把上述物理量转换成能模拟物理量的电信号,即模拟电信号,将模拟电信号经过处理并转换成计算机能识别的数字量,送入计算机,这就是数据采集。

数据采集的主要问题是采集速度和精度。采集速度主要与采样频率、A/D转换速度等因素有关,采集精度主要与A/D转换器的位数有关。高速数据采集系统的设计需要解决系统在速度、精度、数据存储等方面的矛盾。

2 数据采集系统的结构

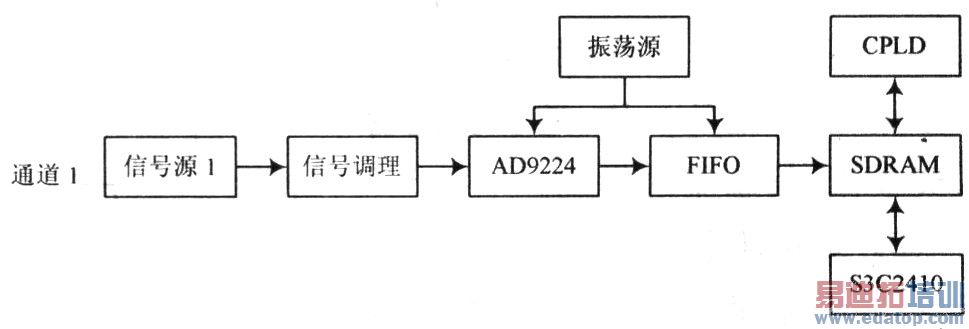

本文介绍的数据采集系统采用Samsung公司的S3C2410微处理器。数据采集系统按照功能可分为以下几个部分:模拟信号调理电路,模数转换器,数据采集和存储,时钟电路和系统时序及逻辑电路,如图1所示。

图1 数据采集系统结构图

3 数据采集系统关键技术分析

3.1 系统时钟电路设计

时钟信号的稳定性决定了采样系统的性能。相位噪声和相位抖动是反映时钟稳定性的的两个主要指标。其中相位噪声描述时钟信号的频谱纯度,相位抖动直接影响时钟的过零点。通常高速的AD采样系统采用三种时钟源:锁相环、晶振、模拟混频器。由于锁相环一旦失去基准频率,输出频率会立刻跳回振荡器本身的频率,此外当进行频率调整的时候,输出频率会产生抖动,频差越大,抖动会越大,不利与高速AD采样系统。模拟混频器速度慢,只适合在低频的条件下工作。因此,在高速电路的设计中,一般选择高频晶振作为时钟源。

在高速AD采样系统中,取样时钟的稳定性与信噪比的性能密切相关。任何时钟信号噪声及时钟信号相位抖动都会影响采样系统的精度,时钟信号相位抖动对模数转换信噪比(SNR)的影响,可通过公式计算:

![]()

其中:fs为采样时钟频率,N为模数转换器位数,△clk为时钟信号相位抖动量。

3.2 模数转换器的选择

ADC的选择除了要考虑数据输出电平,接口方式,控制时序,参考源,带宽等因素外,最重要的是根据设计需求计算动态指标:信噪比,采样率,满度范围等,从而可以得到ADC的位数、最高时钟频率、模拟输入范围等参数,既可选择所需要的ADC。本设计根据要求:采样频率20 MHz,实时采样20 Msps,转换位数12位,选择了美国AD公司的AD9224芯片。

3.3 模拟信号调理电路设计

被采样的信号经过模拟信号调理电路的低噪声放大,滤波等预处理后,进入输入通道。由于高速数据采集系统的输入信号多为高频信号,需要进行阻抗匹配和前置放大。因此可以选择高速低噪声信号前置放大器和信号变压器。

信号前置放大器的优势是放大系数可变,信号输入的动态范围大,还可以配置成有源滤波器,但是放大器的最高工作频率和工作带宽必须满足系统的需要,以避免信号失真。

信号变压器的性能指标要优于信号放大器,而且信号失真小。但是信号变压器的信号放大系数固定,输入信号的幅度受到限制。

3.4 硬双缓冲实现连续采集存储

图中序号1~6代表工作流程,采集数据经CPLD控制首先由FIFO写入存储器1,当存储器1数据写满后,产生硬件中断信号,该信号有两个作用:通知微处理器系统数据已经准备好,由微处理器从存储器1取回数据放入缓冲区;通知CPLD控制逻辑关闭FIFO与存储器1之间的数据通道,同时开启FIFO与存储器2之间的数据通道,后续数据得以连续无间断的存入存储器1。此时,存储器1的数据正被微控制器读出,当存储器2数据就绪后,同样产生硬件中断信号。如此交替循环就可以实现采集数据长时间连续无断点存储。

3.5 多路同步采集存储时序分析

要完成多路信号的同时存储且数据连续无间断点、无差错,对时序逻辑的设计提出了较高的要求,本文采用的CPLD器件,利用其在结构、密度、功能、速度和性能上的特点,并配合在线可编程(ISP)技术,实现了精确的时序控制,大大减少线路的噪声和功耗。

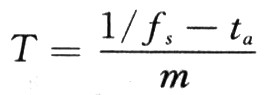

对多路信号同时锁存,若不允许丢失数据,必须在单个采集时钟周期内把多通道锁存的数据存入同一存储器中。假设同步采样频率为fs,通道数量为m,每个通道的存储时间为tn(n=1,2,3,…,m),则有t1+t2+t3+…+tm一1/fs,既所有通道存储时间之和为采样周期。

假设t1=t2=…=tm=T,则各通道存储时间相同的条件为:

![]()

从实际角度出发,在一个采集时钟周期内还有其他的时间消耗,如保持时间和转换时间等,假设其他时间消耗为ta,则:

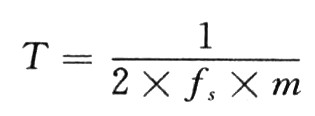

如果fs的占空比为1:1,根据ADC实际工作时的情况,可以近似认为ta=1/(2*,fs),既在一个采集周期中只有半周期的时间可供存储数据,则单个通道的存储时间:

根据上面的设计可以实现单采样周期内多路数据存储。

3.6 系统抗干扰设计

(1)电源设计方面

根据高速电路设计理论,AD采集系统中的电源应当采用线性电源,以避免开关电源引入噪声。为了降低电源阻抗,减小噪声对电源的干扰,通常采用电源层设计,尽可能增大电源面积。在设计每个芯片的供电电路时,在每个芯片的电源附近并联去耦电容和旁路电容。去耦电容为芯片提供局域化的直流。旁路电容可以消除高频辐射噪声和抑制高频干扰。

(2)接地技术方面

高速数据采集系统的模拟地和数字地应严格分开,最后单点共地。共地点通常选择在ADC芯片管脚所需电流最大的位置,这样可以使大电流对地回流最近,以避免对模拟电路的干扰,提高系统的采集精度。

模拟地和数字地可以通过磁珠连接,由于磁珠的高频阻抗大,而直流电阻为零,能够滤除高频电流减少地线上的高频噪声。

4 结语

高速数据采集系统一直是测控领域内研究的热点,本文就基于ARM9的高速数据采集系统的结构,详细讨论了系统时钟电路设计、模数转换器的选择、模拟信号调理电路的设计、硬双缓冲实现连续采集存储、多路同步采集存储的时序分析,系统抗干扰设计等关键技术。经实践证明,该设计方案效率是很高的。

在高速的数据采集过程中,要求数据存储和S3C2410读数据同时进行,在相关文献中提出了一种基于软件系统双缓冲模式的存储技术,但是经过分析发现其在解决连续存储和读数的同时也降低了微处理器的性能。在本设计中提出的基于硬件的双缓冲模式可以很好地解决这个矛盾,其工作原理如图2所示。