- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA和MV-D1024E相机的图像采集系统

摘要:分析了MV-D1024E系列高帧频CMOS相机的工作时序和参数,阐述了CAMERA-LINK接口协议,并对高速数据流的存储与处理机制进行分析,利用FPGA实现了相机的数据接口和控制,并设计灵活的USB接口,利用PC机作为参数输入和显示界面。完成一个从图像采集到存储、显示的高帧频图像采集系统的设计。该系统可靠性好、集成度高、功耗低,且满足不依赖于PC机的图像采集系统的应用要求。

关 键 词:MV-D1024E;FPGA;CAMERA-LINK;图像采集系统

1 引言

图像采集是数字图像处理、图像识别和机器视觉的基础,其应用领域非常广泛。主要采用CCD或CMOS等光电转换器件把光学影像转化为数字信号,然后利用相应的接口将数据输入到处理器中进行图像的数字分析和处理。MV-D1024E是基于CMOS的高帧频系列相机,具有CAMERA-LINK接口。CAMERA-LINK是一种丁业应用的高速数据连接协议,可为CCD或CMOS等数字式相机与图像采集系统间提供简单、灵活的通信接口。

通常情况下,图像采集系统以CCD或CMOS等数字式相机为基础,还需要采集卡来完成数据采集,常见的采集卡有基于DSP实现的和基于FPGA实现的,MV-D1024E系列相机也有厂家提供的采集卡,它接收到CAMERA-LINK的数据,经采集卡简单处理。数据通过PCI总线传输到PC机。但此类基于PCI总线的数据采集方法有一定缺陷,数据只能通过PCI接口连接到PC机,图像处理的功能只能由PC机完成。就使系统不能脱离PC机运行,在很多图像处理的应用场合,需要脱离PC机,并要求系统的体积小、重量轻、功耗低和便携性好。随着可编程逻辑器件的广泛应用,现场可编程门阵列(FPGA)以其可靠性好、集成度高、功耗低和运算速度高等优势,在高速实时图像采集系统得到广泛应用。这里采用FPGA控制MV-D1024E系列相机的数据接口,实现了脱离PC机的图像采集卡功能。为方便系统和用户输入,设计了基于USB的PC机接口。通过USB接口,同样可用于脱离PC机的系统。

2 图像采集系统结构框图

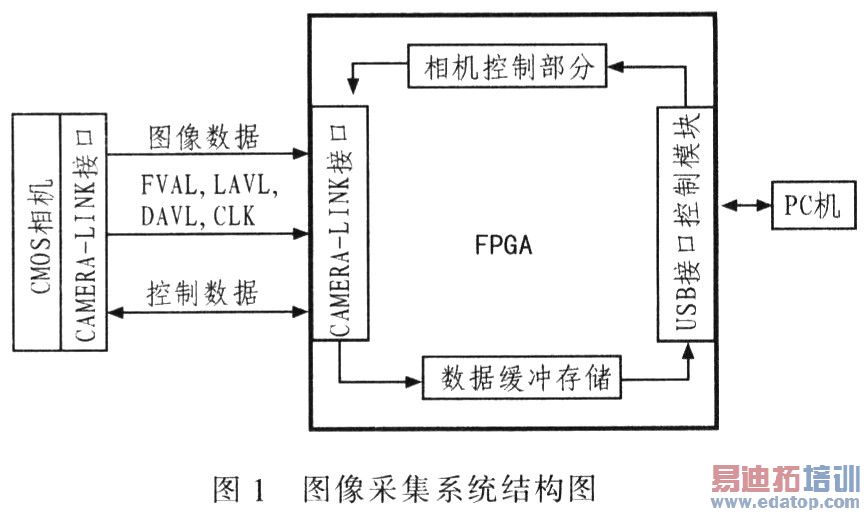

图像采集系统由CAMERA-LINK接口、USB通信接口控制、相机控制及相机数据缓冲存储控制等模块组成,其系统框图如图1所示。

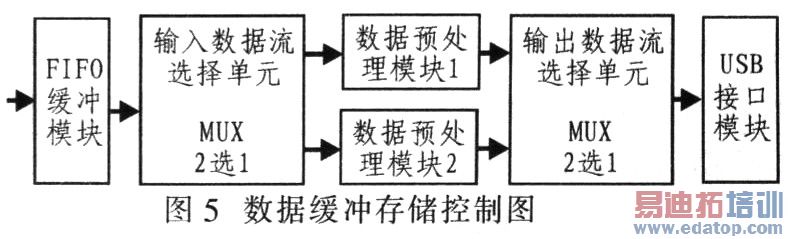

核心控制器选用Altera的Cyclone系列EPlC6Q240C8。通过PC机设定相机的曝光时间、帧频及显示窗口大小等参数,由USB将控制命令传送给FPGA内的USB接口控制模块,其内部集成的相机控制模块根据所接收到的参数,将已固化在FPGA内部ROM中的相机对应的控制代码传送至CAMERA-LINK模块处理,然后通过内部串行模块将控制代码发送给相机。相机得到控制命令后开始工作,通过封装在其内部的CAMERA-LINK模块将罔像数据、时钟信号、帧频信号、行频信号、数据有效信号发到FPGA的CAMERA-LINK模块,经过FPGA中的数据缓冲存储模块将高速数据流进行乒乓操作,然后将数据传送给PC显示及存储处理。

3 图像采集系统的设计

3.1 EP1C6Q240C8简介

FPGA主器件是Ahera公司Cvclone系列的EPlC6Q240C8,具有5 980个逻辑单元和120 000个典型门资源和185个可编程I/O端口,最高工作时钟可到300MHz以上,核心供电电压1.5 V,I/O缓冲供电电压3.3 v,通过JTAG接口实现系统配置。使用的配置器件EPC4串行ROM容量约为4 Mbit,可重复编程50次左右,JTAG接口符合IEEE Std.1149.1标准。

3.2 MV-D1024E相机及CAMERA-LINK接口简介

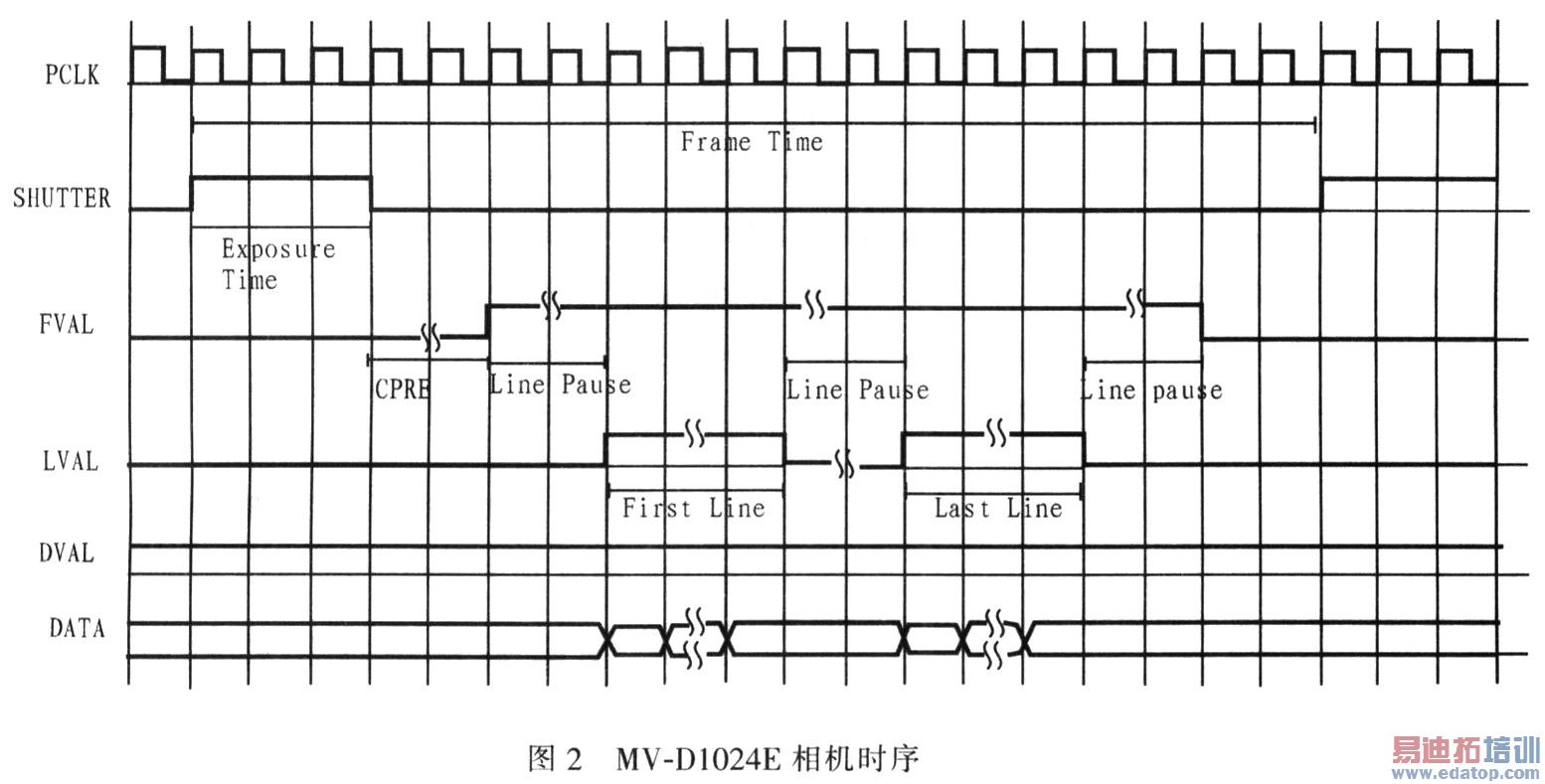

MV-D1024E是高速高动态的CMOS相机系列,采用CMOS主动像元技术,具有12位的采样分辨率和1 024×1 024的像素分辨率,在此分辨率下帧频能达到150帧/s,曝光时间由10 μs~0.41 s,25 ns步进可调,采用CAMERA-LINK接口,用串行口配置相机。CAMERA-LINK是美国国家半导体公司的驱动平板显示器的Channel Link技术的一种扩展技术,其传输率非常高,可达1 Gb/s,提供高分辨率和各种帧频的数字化数据,数据输出采用了LVDS格式,速度快而且抗噪较好。根据应用要求,其支持基本(Base)、中档(Medium)、全部(Full)等数字格式,该接口具有开放式的接口协议,兼容性好。它适用于CCD或CMOS等数字式相机与图像采集系统间的通信接口。如图2所示,当FVAL、LVAL和DVAL同时为高电平时,在相机时钟PCLK上升沿时数据总路线上才有数据。

3.3 相机接口及控制模块设计

3.4 USB接口设计

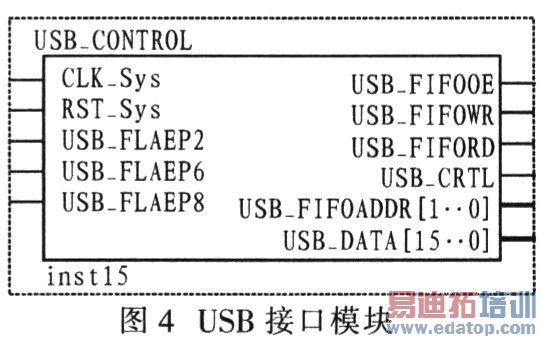

USB接口用于FPGA与PC机间的数据和指令的交换,USB(Universal Serial Bus)是通用串行总线,其具高速度、低成本、低功耗、即插即用和使用维护方便等优点,采用IEEE1394总线协议,最高带宽可达到480 Mb/s。采用Cypress公司的EZ-USBFX2系列器件中的CY7C68013,这是一种基于8051单片机的USB接口主控制器,它集成了USB2.O收发器、串行接口引擎(SIE)和增强型8051微处理器,还包括1个8.5 KB片上RAM、1个4 KB FIFO存储器及1个通用可编程接口(GPIF)。内部RAM运行的8051程序由固化好的外部储存器设备EEPROM提供,与FPGA接口如图4所示。

3.4 USB接口设计

USB接口用于FPGA与PC机间的数据和指令的交换,USB(Universal Serial Bus)是通用串行总线,其具高速度、低成本、低功耗、即插即用和使用维护方便等优点,采用IEEE1394总线协议,最高带宽可达到480 Mb/s。采用Cypress公司的EZ-USBFX2系列器件中的CY7C68013,这是一种基于8051单片机的USB接口主控制器,它集成了USB2.O收发器、串行接口引擎(SIE)和增强型8051微处理器,还包括1个8.5 KB片上RAM、1个4 KB FIFO存储器及1个通用可编程接口(GPIF)。内部RAM运行的8051程序由固化好的外部储存器设备EEPROM提供,与FPGA接口如图4所示。

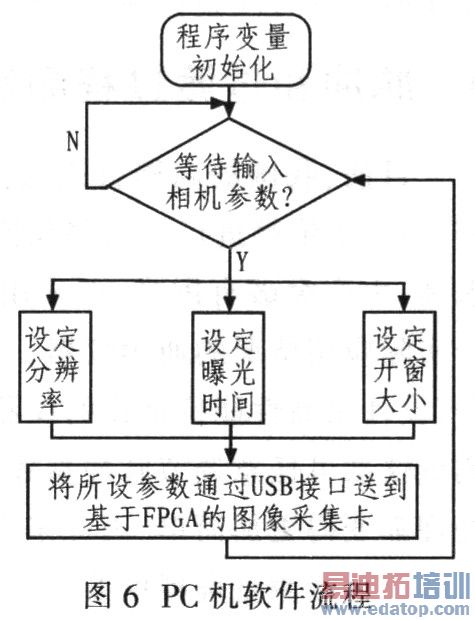

4 PC机软件设计

PC机主要用于用户输入和采集数据的显示,通过Visual C++6.O编译环境开发,结构简单,容易实现。其流程如图6所示,用户通过该界面设置相机的分辨率、曝光时间、开窗大小等参数。

5 结论

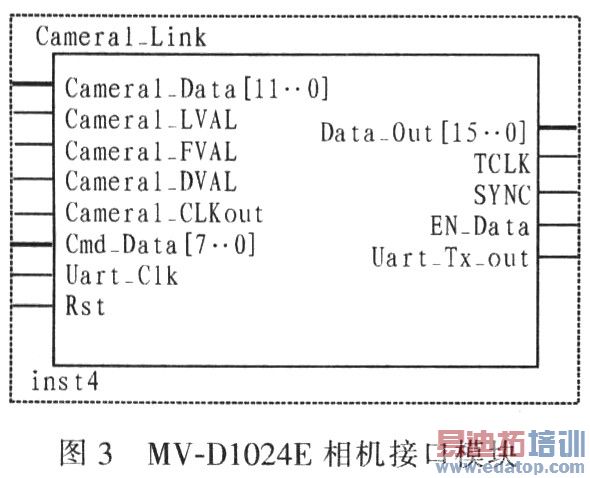

应用FPGA实现的图像采集系统,完成了对高帧频CMOS相机的数据接口和控制,用FPGA集成的USB接口,既可采用PC机作为简单的用户输入要求,又可完全脱离PC机,建立脱离PC机的图像采集及处理系统。MV-D1024E系列相机具有12 bit的数据输出,附加相机的时钟PCLK、帧频信号FVAL、行频信号LVAL和数据有效信号DVAL。图3为用FPGA设计生成的相机接口模块,该模块完成相机数据及各时钟信号的接入,并集成串行接口模块,将用户对相机的控制信号发送到相机。完成相机的参数设置功能。

上一篇:24位A/D转换称重数据采集系统

下一篇:基于虚拟仪器的新型汽车电子测试平台研究