- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ADS1298与FPGA的高性能脑电信号采集系统

脑电信号(EEG)是一种典型的生物电信号,是大脑皮层脑神经细胞电活动的总体反映,其中包含了大量的生理和病理信息,是临床检测的重要生理参数之一,也是认知科学、脑机接口和警觉度等领域研究的重要手段。由于传统脑电信号采集设备都比较庞大,不便于脑电信号的适时获取,因此研究便携式脑电信号采集设备具有重要意义。

脑电信号采集系统主要包括信号放大与调理、模数转换、信号处理与传输等。由于人体的阻抗高且变化大,脑电信号又很微弱,外部环境的干扰很大,因此脑电信号采集系统的放大与调理电路比较复杂,通常要包括高输入阻抗和高共模抑制比的前级放大、带通滤波、工频陷波、多级放大等,导致体积大功耗高。模数转换的精度和速率也决定了脑电信号采集系统的性能,采用10位的模数转换芯片,或者采用ADI公司最高采样率1.25 MBPS的12位AD1671芯片,或者采用16位模/数转换芯片。采用单片机、ARM和DSP作为控制器件的系统中,一般只能完成数据采集和处理较为单一的功能,其中以DSP的数据处理能力最强。相比之下,采用FPGA 作为主控芯片通过硬件描述语言编程可以灵活地进行配置,实现对多通道数据的并行处理,同时能将多个功能在单芯片上实现,基于FGPA和ADS1258设计了集成有视觉、听觉和体感刺激信号源与16通道脑电信号采集功能的诱发电位仪。脑电信号传输的手段以PCI总线、USB等有线方式为主,无线方式传输速率较低,但更易于便携式设计,因此可以针对特定的应用。

ADS1298是TI公司近年推出的一款针对心电和脑电信号采集的24位专用模数转换芯片,本文利用该芯片的高精度,以FPGA为主控制芯片,通过将工频陷波、带通滤波等模拟部分转移到数字侧,在保证性能的前提下简化脑电信号放大与调理的模拟电路,实现便携式脑电信号的采集。

1 系统结构

本文提出的脑电信号采集系统包括信号采集、模数转换和数据传输三个部分。脑电信号采集系统的总体框图如图1所示。

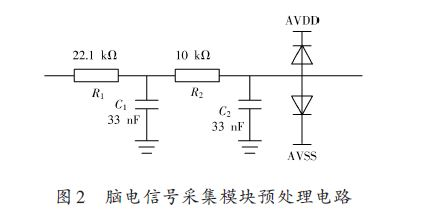

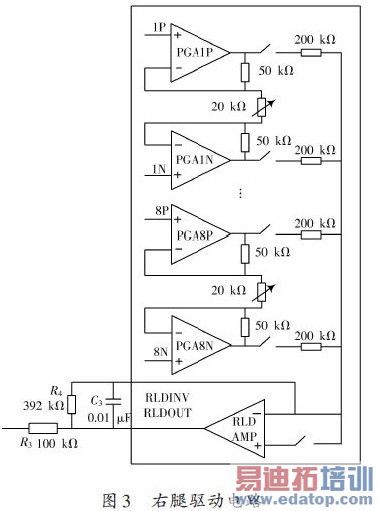

预处理电路包含RC低通滤波和过压保护电路,对脑电极采集到的信号进行低通滤波和过压保护后直接送入到ADS1298模数转换器中进行模/数转换。右腿驱动电路主要是用来抑制共模干扰,由ADS1298 内部的RLD电路以及外部的电容电阻构成的反向放大滤波电路组成。

系统采用FPGA作为主控制芯片,利用硬件描述性语言来编写配置I/O 口成通用串行SPI接口,与高精度多通道的模数转换芯片ADS1298 的SPI 接口相连实现通信,从而控制ADS1298 将脑电极采集到的模拟信号转换为数字信号,经过滤波陷波处理后存储在SDRAM中,作为采集数据的缓冲部分,以便为后续的传输模块做准备。

数据传输模块主要是采用FPGA配置I/O口作为以太网接口芯片DM9000A的控制接口,并与DM9000A的控制接口串联,实现其逻辑控制;采用UDP 协议将从SDRAM中读取的数据打包,通过RJ45网络接口,传输到上位机。8个通道1 kHz的采样率,理论上需要192 Kb/s的传输速率,以太网口10/100M的传输速率完全能满足需要。

2 硬件电路设计

2.1 脑电信号采集预处理电路

人体自发的脑电信号的幅值很小,一般为5~100 μV,而诱发脑电信号的幅值更小,只为2 μV左右。

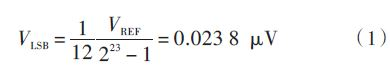

TI的ADS1298是24位、8通道差分输入模/数转换芯片,最大共模抑制比可达115 dB,直流输入阻抗1 GΩ,在内部增益设置为12 倍和参考电压VREF =2.4 V 的条件下,信号分辨率为:

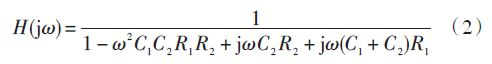

因此,将脑电信号不经过放大和调理直接经过简单的低通滤波后进行模数转换仍可以满足需要,故预处理电路设计如图2所示,其频率响应函数为:

由式(2)可知3 dB截止频率为96.2 Hz,脑电信号主要频带集中0.1~100 Hz,此预处理电路可完全涵盖脑电信号的有用信息。

2.2 右腿驱动电路

右腿驱动电路是抑制生物电信号采集系统中的共模干扰(特别是50 Hz的工频)的最常用、最有效的一种方法。由于ADS1298芯片内部集成了右腿驱动电路,因此只需要配置ADS1298 内部相关寄存器,并在外围使用少量的电子器件,即可实现该功能,具体右腿驱动电路如图3所示。从图3可知,电路由ADS1298内部的RLD电路以及外部的R3 ,R4 ,C3 组成,其中R3 起限流保护作用,R4 与C3 构成反向放大滤波电路。

2.3 FPGA接口电路

为了实现高精度、高可靠性的脑电信号采集,本系统采用Altera Cyclone Ⅱ系列芯片EP2C35F672 作为控制和处理的核心,EP2C35系列FPGA内部包含33 216个逻辑单元(LE),105 个M4K RAM 块,RAM 总量达到483 840位,35个内嵌乘法器,4个锁相环(PLL),可用最大I/O 口为475,内部资源完全满足高性能的脑电采集系统的需求。

本系统中与FPGA 相连的有模数转换芯片ADS1298、以太网接口芯片DM9000A和SDRAM.FPGA的接口电路就是把这些芯片的信号控制端口、数据读写端口和地址端口直接与FPGA的I/O相连,通过Quartus Ⅱ分配相对应的I/O口,即可实现接口电路的有效连接。

3 软件模块设计

3.1 FPGA内部信号处理控制模块设计

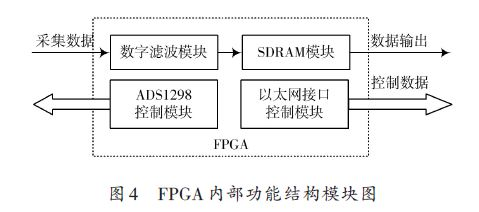

本系统使用Verilog HDL语言单独编写A/D转换器的控制模块、SDRAM存储器控制模块、数字滤波器模块以及以太网端口传输控制模块,通过功能仿真和时序仿真来验证各个模块是否能够独立完成相对应的控制功能。验证成功后,最终通过例化,在FPGA内部形成一个脑电信号采集系统的核心处理控制模块,图4为核心处理控制模块的具体功能结构模块框图。

3.2 ADS1298软件设计

本系统中最重要的一环就是模/数转换,这里重点介绍ADS1298的软件模块设计。ADS1298的工作流程主要包括:上电初始化、发送操作命令和配置寄存器、开始转换并读取转换数据。ADS1298的操作命令主要分为数据操作命令和寄存器读写命令。数据操作命令主要包含SDATA和RDATAC(连续读数据)。连续读数据只需要写入一次RDATAC 操作命令,就可以在每次的DRDY变为低电平时读取转换数据。寄存器读写命令分为RREG 和WREG.这两个操作命令分别包含两个字节,第一个字节为读写寄存器的起始地址,第二个字节为读写寄存器的个数。

FPGA 软件编程中具体的ADS1298 模块内部框图如图5所示。

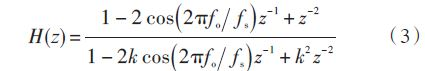

3.3 数字滤波模块软件设计

本系统的数字滤波模块主要为50 Hz 陷波器和数字带通滤波器,两者的软件设计方法相似,这里重点介绍50 Hz 的陷波器设计方法。本系统中设计的陷波器技术指标为:抽样频率fs 为1 kHz,陷波频率fo 为50 Hz,3 dB 带边频率为45 Hz和55 Hz,阻带上下边频率为49 Hz和51 Hz,阻带衰减不小于40 dB.为了便于硬件的实现,本文选用二阶的IIR 陷波器,其传递函数如式(3)所示:

k 的值决定了陷波深度,根据具体的信号进行调整,从而实现最佳陷波。对于EEG信号,最佳的k 取值为0.88.FPGA软件设计时需要根据传递函数设置几个寄存器存储系数和中间值,并在每个时钟对这些中间值移位更新,然后重新计算得到新的输出值。

4 结语

系统采用Altera Cyclone Ⅱ系列芯片EP2C35F672作为控制和处理的核心,8通道、低噪声、低功耗、24位的Σ-△模/数转换芯片ADS1298作为采集系统核心,简化了系统的硬件设计,具有功耗低、便携式、精度高等优点;采用FPGA和DM9000A以太网控制器相结合,成功的将脑电信号采集系统和PC上位机相连,避免了直接上传时的数据丢失,实现了彼此间的高速数据通信。本系统利用Quartus Ⅱ工具和Verilog HDL 语言对FPGA进行设计、仿真和验证,便于设计的修改和优化,大大缩短了产品的开发设计周期,因此本系统具有良好的使用价值和应用前景。

上一篇:第一页

下一篇:基于嵌入式图像信息采集与传送系统的设计