- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

便携式功率分析仪设计-----硬件设计(三)

3.3.4.2可变增益放大器

由于在信号调理通道上使用了具有较大衰减的无源衰减网络,为动态调整A/D的采样范围,我们在A/D采样模块之前加入一个可变增益放大器,以达到对微小信号或过大信号仍然能够进行采样。我们选用了AD8369,AD8369是一种以分贝为单位的线性数字可变增益放大器(DVGA),该芯片具有45dB的增益调节范围,3dB步长,工作频率从低频到400 MHz,20 MHz带宽内增益波动小于0.1 dB.AD8369的增益控制是通过一个数字接口(串行或并行)实现的。

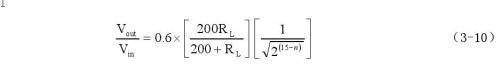

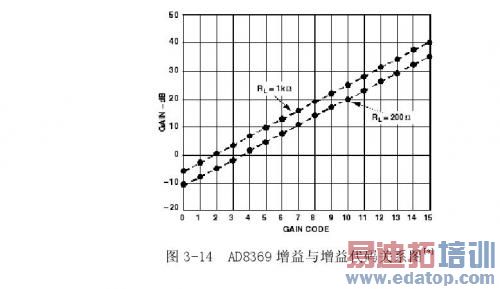

AD8369的内部电路结构由一个7阶R-2R梯形电阻衰减网络、固定增益放大器、3dB开关衰减器、互补电流源输出网络、偏置电路、增益步进控制电路和数字接口等部分组成。AD8369工作时,数字接口(并口或SPI串口)接收的4位二进制增益控制代码,其高3位用于控制跨导单元和梯形电阻衰减网络,实现步长6 dB、最大42 dB的增益调节,最低位用来控制3 dB开关衰减器,并配合前面的电阻衰减网络,最终实现在45 dB增益调节范围内,3 dB步长的数字增益调节功能。AD8369的输出电路采用两对互补电流源的全差分形式,差分输出阻抗200Ω。AD8369的电压增益可以用(3-10)式计算:

式中RL是外接负载电阻,单位是欧姆;n是增益控制代码,最小是0,最大是15.由图3-14可知,当增益控制代码不变时,负载RL增大,则芯片的增益提高;当负载电阻一定时,在整个45 dB增益调节范围内,AD8369的增益与增益控制代码之间都能保持良好的,以分贝为单位的,3dB步进的线性关系。

同时,AD8369在从低频到400 MHz工作频率范围内都能保持3dB步进和相对较平坦的频响特性。当工作频率低于300 MHz时,其噪声系数基本可保证小于7 dB.由此可以满足信号通道的要求。

3.3.4.3 A/D采样

A/D转换器是整个功率分析仪的重要组成部分之一,A/D转换器作为将模拟量转换为数字量的作用,可以将我们获得的峰值电压转化为数字量,通过单片机读人存储器,通过功率和峰值电压的线性关系,可以计算处理的到信号的功率。A/D转换的基本原理是,它通常有四个环节:采样,保持,量化,编码。其中量化和编码是必不可少的核心工作。采样是指对输入的模拟信号按一定的采样速率f s即按一定的时间间隔进行抽样。采样实质就是对模拟信号进行时间分隔,把连续的模拟量离散化,对采量速率要求f s≥2f min,即至少是模拟信号最低频率的2倍以上。采样得到的离散模拟电压必须保持一段时间以保证量化和编码工作的完成。量化是A/D转换器的关键一步,是对采样到的模拟信号进行幅度分割,既在幅值上使其离散化。具体的做法是用足够晓得标准单位一量化单位△来量度采样值并取整数倍,量化误差为±1△或±1/2△。量化取整所获离散幅值通过编码形成二进制或BCD代码的数字量输出。A/D转换器主要考虑的是转换的精度和速度的问题。由Dn = 2n /Vr*Ui(Dn为n维数据的输出,Ui是输入的模拟电压,Vr为基准电压)。可知,位数越高转化后的精度越高。根据我们需要达到的功率精度,我们可以选择恰当位数的A/D转换器。采样电路也是峰值功率测量的主要部分。其采样速率直接影响了仪器所能获取的最窄脉冲调制信号,其A/D转换位数影响着功率测量精度,并且其性能的好坏对整个系统工作的稳定性起着决定性作用。A/D采样得到的数据存入FPGA中的FIFO中,然后传给ARM芯片进行计算处理。

本系统接收信号的最窄调制脉宽为400ns,由奈奎斯特采样定理知采样频率必须大于被测信号最大频率的两倍,才能不失真的恢复原信号。但实际上以奈奎斯特频率采样很难获得采样精度的,所以通常是以信号频率的5~10倍的频率去采样。为了能准确地反映信号的大小,要求A/D采样的采样率不得低于12.5MHz.为保证其对输入信号细致特征的捕获能力,故暂选用8位的AD9480高速ADC.

此款ADC具有250msps转换速率,同时保持±0.25LSB的微分线性误差(DNL)即使工作在250M采样率的情况下仍然仅有590 mW的较低功耗。AD9480支持多路分配的TTL/CMOS输出逻辑和低电压差分信号(LVDS)输出,以便兼容现有的和下一代的专用集成电路(ASIC)。在CMOS多路分配模式下,AD9480可以交叉存储模式或并行模式,并以半时钟速率在两个8位通道中移动数据。当工作在LVDS输出模式时,AD9480通过单一输出通道以全时钟速率输出数据。

这款8位AD9480 ADC除了支持LVDS输出简化设计考虑,还具有46.4dB信噪比(SNR)和无失码等特点。AD9480在-40℃~+85℃的整个工业温度范围内提供±0.35LSB的DNL.该转换器采用3.3V单电源供电并且包含一个内部基准电压源和采样跟踪保持电路。AD9480与ADI公司的AD9041A高速ADC具有相同的引脚配置,允许设计工程师通过电路板修改升级其产品,从而降低系统开发成本。在系统工作时,AD9480工作在LVDS输出模式下,根据不同时基所提供的不同时钟,以全时钟速率采集数据。根据采样定律,采样率最高为250MHz的高速A/D转换器,能够满足对信号频率为50MHz以下信号的实时采集,由于检波器AD8318的最小响应时间为8ns,这使得AD8318对射频脉冲的检波能力为50MHz左右,故A/D采样芯片采样速度能够满足需要。

3.3.5控制电路的设计

3.3.5.1 ARM芯片简介及其外围电路连接

LPC2138微控制器是基于一个支持实时仿真和嵌入式跟踪的32位ARM7TDMI-S CPU,并带有512kB嵌入的高速Flash存储器。128位宽度的存储器接口和独特的加速结构使32位代码能够在最大时钟速率下运行。对代码规模有严格控制的应用可使用16位Thumb模式将代码规模降低超过30%,而性能的损失却很小。

较小的封装和很低的功耗使LPC2138特别适用于访问控制和POS机等小型应用中;由于内置了宽范围的串行通信接口和32kB的片内SRAM,它们也非常适合于通信网关、协议转换器、软件modem、语音识别、低端成像,为这些应用提供大规模的缓冲区和强大的处理功能。多个32位定时器、2个10位8路的ADC、10位DAC、PWM通道、47个GPIO以及多达9个边沿或电平触发的外部中断使它们特别适用于工业控制应用以及医疗系统。

主要特性:

- 32位ARM7TDMI-S核,超小LQFP64封装。

- 32kB的片内静态RAM和512kB的片内Flash程序存储器。128位宽度接口/加速器可实现高达60 MHz工作频率。

- 通过片内boot装载程序实现在系统编程/在应用编程(ISP/IAP)。单个Flash扇区或整片擦除时间为400ms.256字节行编程时间为1ms.

- EmbeddedICE RT和嵌入式跟踪接口通过片内RealMonitor软件对代码进行实时调试和高速跟踪。

- 2个8路10位的A/D转换器,共提供16路模拟输入,每个通道的转换时间低至2.44us.

- 1个10位的D/A转换器,可产生不同的模拟输出。

- 2个32位定时器/外部事件计数器(带4路捕获和4路比较通道)、PWM单元(6路输出)和看门狗。

- 低功耗实时时钟具有独立的电源和特定的32kHz时钟输入。

- 多个串行接口,包括2个16C550工业标准UART、2个高速I2C总线(400 kbit/s)、SPI和具有缓冲作用和数据长度可变功能的SSP.向量中断控制器。可配置优先级和向量地址。

- 小型的LQFP64封装上包含多达47个通用I/O口(可承受5V电压)。

- 多达9个边沿或电平触发的外部中断管脚。

- 通过片内PLL(100us的设置时间)可实现最大为60MHz的CPU操作频率。

- 片内集成振荡器与外部晶体的操作频率范围为1~30 MHz,与外部振荡器的操作频率范围高达50MHz.

- 低功耗模式:空闲和掉电。

- 可通过个别使能/禁止外部功能和外围时钟分频来优化功耗。

- 通过外部中断或BOD将处理器从掉电模式中唤醒。

- 单电源,具有上电复位(POR)和掉电检测(BOD)电路:

- CPU操作电压范围:3.0V~3.6 V (3.3 V±10﹪),I/O口可承受5V的电压。

ARM7TDMI-S是一个通用的32位微处理器,它可提供高性能和低功耗。ARM结构是基于精简指令集计算机(RISC)原理而设计的。指令集和相关的译码机制比复杂指令集计算机要简单得多。这样使用一个小的、廉价的处理器核就可实现很高的指令吞吐量和实时的中断响应。

由于使用了流水线技术,处理和存储系统的所有部分都可连续工作。通常在执行一条指令的同时对下一条指令进行译码,并将第三条指令从存储器中取出。

ARM7TDMI-S处理器使用了一个被称为THUMB的独特的结构化策略,它非常适用于那些对存储器有限制或者需要较高代码密度的大批量产品的应用。在THUMB后面一个关键的概念是“超精简指令集”。ARM7TDMI-S处理器基本上具有两个指令集:标准32位ARM指令集与16位THUMB指令集。

THUMB指令集的16位指令长度使其可以达到标准ARM代码两倍的密度,却仍然保持ARM的大多数性能上的优势,这些优势是使用16位寄存器的16位处理器所不具有的。这是因为THUMB代码和ARM代码一样,在相同的32位寄存器上进行操作。THUMB代码仅为ARM代码规模的65%,但其性能却相当于连接到16位存储器系统的相同ARM处理器性能的160%.

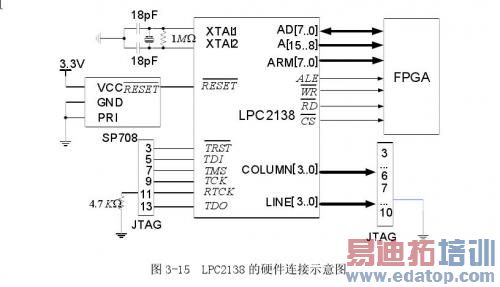

如图3-15所示,由于LPC2138芯片的高速、低功耗和低工作电压导致其工作噪声容限较低,对电源的纹波、瞬态响应性能、时钟源的稳定性和电源监控可靠性等方面也提出了更高的要求。

LPC2138可使用外部晶振或时钟源,内部PLL电路可调整系统时钟,使系统运行速度更快(CPU最大操作时钟为60MHz)。倘若不使用片内PLL功能及ISP下载功能,则外部晶振频率范围是1~30MHz,外部时钟频率范围是1~50MHz;若使用片内PLL功能或ISP下载功能,则外部晶振和外部时钟频率范围均为10~25MHz.本设计使用了12MHz外部晶振,XTAL1和XTAL2为外部时钟输入脚,分别接12MHz无源晶震的两端。由于LPC2138内部已经集成了反馈电阻,只需要在无源晶振的两端各接一个电容就可以起振。根据LPC2138的芯片手册查表可知,12MHz无源晶振的外接负载电容应为18pF.此外,为了使系统更容易起振,在晶振的两端并接了一个1MΩ的电阻。

RESET引脚是一个施密特触发的复位端,带有一个额外的干扰滤波器。复位干扰滤波器使处理器可以忽略非常短的外部复位脉冲,它决定了RESET保证LPC2138芯片复位所必须保持的最短时间不得小于300ns.在本系统中,LPC2138上电后即开始工作,中间不需要进行复位。而且为了保证系统的稳定性,要求LPC2138在工作过程中不得复位。因此本系统的复位电路采用了专用微处理器电源监控芯片SP708S,以提高系统的稳定性。MR是SP708S的复位脉冲输入脚,当MR引脚上出现低电平时,SP708S立即输出复位信号,RESET引脚输出低电平使LPC2138复位。根据系统实际要求,现将MR引脚悬空,不接任何复位信号,系统上电后,SP708S的RESET引脚即输出恒为高(3.3VCC),保证系统在整个工作过程中不复位。

LPC2138的47个IO口被分为二组(P0口,P1口),P0组有31个,P1组有16个,均可通过设置相应的管脚功能选择寄存器来实现第二功能。本设计中,LPC2138与器件的连接采用双向I/O方式,将P0口和P1口设为普通I/O接口,利用P0口的16个I/O口作为数据/地址线(低8位数据/地址复用,高8位为地址线)。虽然整个系统中的数据最宽为12位(12位的A/D采样数据),但是由于选用了8位A/D芯片AD9480,所以数据输入输出线也相应的设为8位宽(P0.8~P0.15),LPC2138提供I 2 C总线和串行总线,但在系统实际设计中,我们利用通用I/O口模拟总线传输方式,利用P0.27~P0.30模拟ARM的读写控制WR,RD以及ALE,CS.

JTAG接口电路采用ARM公司提出的标准20脚JTAG仿真调试接口,JTAG信号的定义及与LPC2138的连接电路如图3-15所示。LPC2138支持通过JTAG串行端口进行仿真和调试。跟踪端口允许跟踪程序的执行。调试和跟踪功能只在GPIO的P1口复用。这意味着当应用在嵌入式系统内运行时,位于P0口的所有通信、定时器和接口外设在开发和调试阶段都可用。同时,ARM的P1.16~P1.23口通过连接JTAG插座,外接控制键盘。

3.3.5.2 D/A转换电路

本设计系统中D/A转换电路输出主要用于调整通道直流偏置以及为比较器提供外部参考电压。D/A转换器的转换精度决定了通道偏置调整的步进的最小值,同时也决定了外部触发器的工作精度。因此,应当根据系统的需要选择适当位数的D/A转换器。本设计采用TI公司的4通道,8位D/A转换器TLC5620.其特性如下:

四路8位电压输出D/A转换器;

- 5V单电源工作;

- 串行总线接口;

- 高阻抗参考电压输入;

- 可编程1至2倍输出范围;

- 可方便地同时输出更新;

- 内部上电复位;

- 低功耗;

- 半缓冲输出。

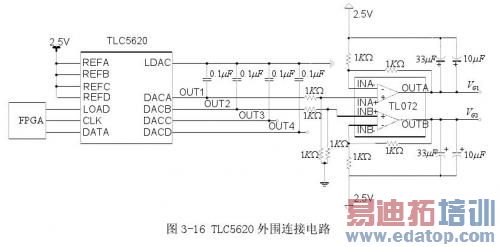

本设计中,TLC5620的外围连接电路如图3-16所示。图中,REFA~REFD为参考电压输入端,这里均接到一个稳定的2.5V电源上。TLC5620输出信号(DACA~DACD)的电压范围可编程选择为参考电压的一倍或两倍。LOAD、CLK、DATA为TLC5620的串行总线接口,通过这三根总线可对TLC5620编程实现数字控制。本设计中这三根总线与FPGA相连,实现由FPGA控制TLC5620相应通道的输出电压。

此外,TLC5620的信号输出端带有施密特触发器,从而使信号输出端(DACA~DACD)具有较高的噪声抑制能力。为了进一步减小控制电压上的噪声,本设计中还在每个输出端DACA~DACD各加了一个0. 1μF的电容进行滤波。由图3-18可以看出,TLC5620的通道A和通道B分别被用来作为信号通道偏置调整和外部比较器的比较电平,还需要在这两个通道的输出各加一级运放使其输出V G1和V G2能够在-2.5V~2.5V之间调整,本设计选择双通道的运放TL072.其负向输入端接2.5V,在TL072的两路输出端均加了33μF和10μF的电容对此增益控制电压进行滤波,滤波后的电压分别送去信号通道和比较器。