- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DDS频率源的设计与实现

摘要 介绍了DDS的基本工作原理,阐述了DDS技术局限性,最终实现了一种基于FPGA+DDS可缡编程低相位噪声的频率源,输出信号范围170~228 MHz。测试结果表明,该频率源具有高频率分辨率和低相位噪声等特点,能够满足通信系统对频率源的设计要求。

关键词 DDS;频率源;AD9912;FPGA

频率源是现代射频通信系统的核心,对系统的运行起着决定性作用。射频电路频率源的好坏关系着整个系统的稳定性。目前频率合成技术正朝着杂散和相位噪声更低的方向发展,同时还要求有更宽的频带和更高的频率分辨率。直接数字频率合成(DDS)正是在该需求背景下发展的,其具有微小的频率调谐和相位分辨能力。融合了模拟和数字技术的DDS是产生高质量高频谱纯度宽频带频率的理想方法。

文中基于ADI公司的AD9912芯片提出一个直接频率合成方案,输出频率范围为170~228 MHz,频率步进12.5 kHz,相位噪声优于98 dBc /Hz@1kHz。

1 DDS基本工作原理

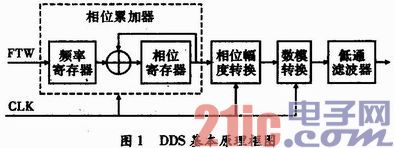

直接频率合成器DDS是一种高分辨率的数字分频器。通过频率调节字来分频系统时钟,以输出所需的频率。DDS有两个特点:(1)工作在数字域,其输出频率相位和幅度可在数字处理器的控制下,精确、快速地变换。(2)频率分辨率主要取决于频率调节字的位数,因此可达到较高的频率分辨率。DDS基本原理框图如图1所示,其主要包括:相位累加器、相位-幅度变换器、数/模变换器和低通滤波器。

1.1 相位累加器

对于正弦波而言,幅度不是线性变化的,而相位却是线性变化的,这便是DDS能够合成正弦波的基础。DDS依据频率调节字的位数M,将0°~360°的相位变化平均分成2M等份。假设系统参考时钟为fc;输出频率为fout在每个时钟周期转过一个角度360°/2M,则可产生一个频率为f/2N的正弦波的相位增量。因此,只需选择恰当的频率调节字K,使得fout/fc=K/2M,即可得到输出频率。

fout=(K×fc)/2M (1)

可以得到DDS的最小频率分辨率为

△f=fc/2M (2)

1.2 相位幅度转化器

根据相位累加器的输出,得到所需合成fout频率所对应的相位信息,是将累加器输出的数字相位信息变换成正弦波相应的幅度值。将正弦波相位到幅度的转换可通过查表操作完成,然后正弦波幅度数值以二进制的形式被送入DAC进行数模转换。

1.3 DAG数模变换器

从相位幅度转换器得到的二进制数字信号被送入数模转换器中,变换成模拟信号输出。此处DAC变换器的位数对输出频率的分辨率并无影响,但DAC变换器的位数应将不低于二进制数字信号的位数,这样输出频率的分辨率主要由频率调节字的位数决定。

2 DDS的局限性

2.1 输出频带范围有限

由于DDS内部DAC和波形存储器(ROM)的工作速度限制,使得DDS输出的最高频有限。目前市场上采用CMOS、TTL和ECL工艺制作的DDS芯片,工作频率通常在几十~400 MHz。设计采用的AD 9912芯片,其支持的最高时钟高达1 GHz,根据奈奎斯特采样定理,每周期的采样点≥2,则其输出的最高频率≤500 MHz。实际上,为保证输出波形的质量,实际采样点>2,因此AD9912能够输出的最高频率<400 MHz。

2.2 输出杂散大

由于DDS采用全数字结构,从而不可避免地引入了杂散输出。DDS杂散输出的来源有3个:相位累加器相位舍位误差造成的杂散;幅度量化误差造成的杂散和DAC非理想特性造成的杂散。

3 系统设计

3.1 硬件设计

设计采用ADI公司的高端产品AD9912作为系统的频率源。AD9912是ADI公司DDS系列产品中最新推出的采样速度达到1 GSample/s的DDS器件,其内部包括DDS核以及14位DAC,且具有PLL时钟倍频电路,串行输入寄存器,时序控制单元等。芯片内部的DDS核可由内部的锁相环提供达1 GHz的采样时钟也可以由外部时钟提供,其频率控制参数、相位控制参数和幅度控制参数由DDS核外各模块寄存器来提供。AD9912具有多种工作模式,通过SPI时序对寄存器操作来选择所需要的模式。控制字可以是固定值,也可是线性和非线性变化值,连续传送给核内相关寄存器。

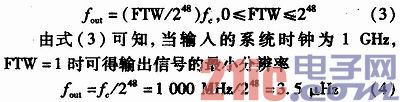

AD9912的DDS核由48位相位累加器和相位-幅度转换器组成,可提供高速的频率转化速度与极高的频率分辨率,当相位累加器开始计数并且频率控制字>0时,相位-幅度转换器将相位累加器的输出数据作为波形存储器的取样地址将相位信息通过查表操作转换为幅度信息,进而得到数字正弦波。输出信号的频率与频率控制字FTW之间的关系满足式(3)。

由此可知,AD9912能够满足频率步进12.5 kHs的要求。

3.2 低通滤波器设计

由于DDS芯片的输出频谱中具有大量的谐波分量和杂散输出。为得到高质量射频信号,即需要在DDS输出端加一个滤渡器来实现滤除杂波、平滑信号的功能,而低通滤波器能较好地实现此功能。因此为得到高质量的DDS输出频谱,选择和设计低通滤波器是关键。

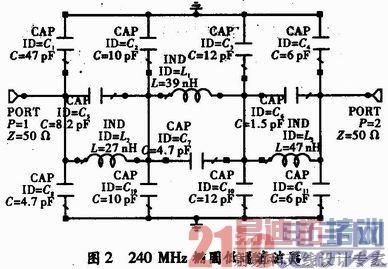

椭圆低通滤波器也叫考尔滤波器,因为其在离通带较近的地方增加了衰减极点,使椭圆滤波器相比切比雪夫滤波器和巴特沃斯滤波器具有更陡峭的过渡带,同时在相同衰减特性要求下,椭圆滤波器的阶数较低,所以在DDS中采用此滤波器。

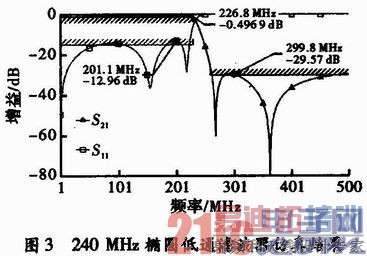

使用MWO设计阻带为240 MHz的椭圆低通滤波器如图2所示,仿真结果如图3所示。

从仿真结果可看出,采用椭圆低通滤波器具有通带内插入损耗小、过渡带陡峭以及带外抑制接近30 dB的特性,能够较好地抑制各种带外杂散。

3.3 编程控制

设计采用FPGA作为AD9912频率输出的控制器。AD9912正常工作DDS上电启动后,FPGA通过SDO CSB SCLK按照SPI时序向AD9912写入频率调节字(FTW)。在写完频率调节字后,将I/O_Update置位,则AD9912将映射寄存器内的频率调节字更新到寄存器,在输出口测得的频率随即改变。频率更新时间取决于SPI时序对于寄存器的写入速度,而DDS核的转换时间几乎可忽略不计。因此AD9912可作为高速跳频的频率源。

4 测试结果

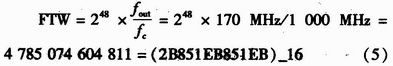

设计中采用的参考时钟频率fc=1 000 MHz要求输出频率fout=170 MHz,则其频率调节字

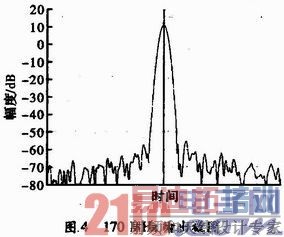

通过式(5)可计算得到任何的频率调节字,将其转换为16进制的数据格式后,通过FPGA严格按照SPI时序要求写入AD9912的寄存器。输出结果如图4所示,从图中可看出,AD9912的输出频率的相位噪声达到了99.56 dBc/Hz@1kHz,且输出频率准确度高杂散小,通过快速的配置寄存器就可完成快速的频率捷变,可作为跳频频率源,并能够满足设计要求。

5 结束语

根据射频短波通信系统中的频率源需求,介绍了整个频率源的实现方法,完成了使用FPGA+DDS实现射频短波频率源。采用ADI公司高端芯片AD9912,时钟输入使用AD9912内部通过锁相环(PLL)产生的低杂散高性能时钟信号,且增加外部椭圆低通滤波网络,从而有效提高了输出信号的质量。通过对输出信号的测试,证明了该方案输出在170~228 MHz的频带范围内具有相位噪声小、频率值精准及频率分辨率高等优点,可满足短波射频通信对频率源的要求。总之,该频率源设计具有外围电路简单、操作控制简便、可实现快速跳频输出以及信号频谱质量高等特点,适宜作为短波通信的频率源。