- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何利用逻辑分析仪来缩短嵌入式系统的开发时间

前言:

今日依据微控制器(MCU)和数字信号处理器(DSP)所设计的嵌入式系统功能是越来越复杂,其脚位数设计也越来越多,不过当您需要数字设计的重要信息时,也唯有设计复杂精密的逻辑分析仪才能处理先进电子产业不断增加的性能及复杂性。

所以使用逻辑分析仪通常是最佳(有时是唯一)的办法;例如,若要观测状态模式中的逻辑,或在众多的频道中检查时序关系,您就非得使用逻辑分析仪不可了。

目前还是有许多研发工程师依赖着其所熟悉的示波器,用来量测大量的数字信号和除错(Debug)复杂的数字电路设计,也许您会觉得为什么不可以用示波器来量测,当然可以,只是当您使用逻辑分析仪来替代示波器量测和除错(Debug)数字的相关信号时,您的研发时间将会大量的缩短,节省您宝贵的研发时间,现在您不用马上相信我,但当您看完下列说明后,相信您马上会爱上逻辑分析仪!

量测通道:

在目前的新式微处理器和微控制器其设计的脚位数是越来越多,所以如果还是使用示波器(量测通道2~4CH)来观察分析的话,那肯定会浪费很多的研发时间,进而造成新产品的上市时间的延长。以下举例说明:假设有一微处理器(MCU)是20PIN的脚位数,共有8个I/O脚位数,当工程师想要同一时间来观查分析所有I/O脚之变化和相互间的关系;此时使用示波器就没办法办到,因为示波器最多就只有四个量测通道,所以最多一次可以同时间观察四个脚位的I/O变化,所以要观察八个脚位的I/O变化,并不是用示波器看两次,就可以达到,而且要相互间的关系也很难作判断,我想几乎所有工程师只要使用示波器用来量测此案例,一定都会非常苦恼,而且浪费在此段的量测时间差不多是占整个研发周期1/4;但是假如工程师用逻辑分析仪来量测此案例时,您知道会有多简单吗 因为逻辑分析仪拥有的量测通道从16~数百个不等(如图一),逻辑分析仪可以一次将同一时间八个脚位的I/O变化和相互间的关系,显示在同一窗口上,可以让工程师很容易的去观察分析,并发现相互间之差异性,如此,使用逻辑分析仪量测此案例,将会缩短1/5的研发周期。

也许您会认为那么多的量测信道,怎么会记得哪一个通道量测哪一个脚位或是信号,关于这一点逻辑分析仪也帮您设想到了,您可以针对每个量测通道更改名称,只要将通道名称更改为您所量测的脚位或是信号名称,哪怕您将此波形档案储存起来,等后续您还要再来分析此波形时,也会很容易进入分析状况,不会完全搞不清楚状况。

图一 逻辑分析仪拥有多个量测通道

放大分析功能:

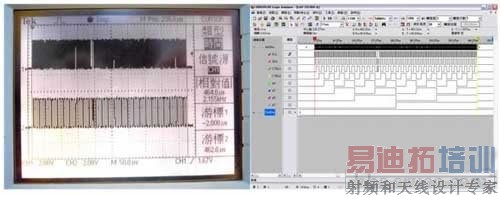

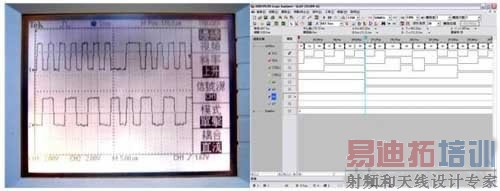

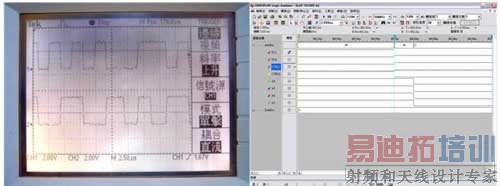

在目前的消费性数字电子产品,其功能设计是越来越精良,也越来越复杂,且其所要求的质量却不会因为功能性的提高,而降低产品质量,反而是要求越来越高,所以研发工程师所面临的问题,就是其所要观察分析的波形数据长度越来越长,而且最好能把一个CYCLE程序的波形数据全部显示出来,供工程师可以一次性的观察分析波形数据。以下举例说明:有一工程师用MCU设计了一个八位的计数器程序,从0x00开始计数到0xFF结束,且其震荡器是使用8MHz;此时当工程师使用示波器和逻辑分析仪来观察分析此计数器的计数从0x00~0xFF是否正常时,它们是否可以一次将0x00~0XFF的波形数据全部抓取显示出来 (如图二)所抓取下来的波形数据是否可以全部无限制放大来分析和放大后波形是否会失真 (如图三和图四)

图二 均可以抓取0x00~0xFF的波形

图三 根据上图目测发现Bug的波形,将波形放大来观察分析

图四 当示波器再放大时,波形显示已经是失真状态,但是逻辑分析仪却没有这个限制,反而利用水平放大的功能,来寻找目测难以发现的Bug,如图本来0xFF之后是要接0x00,但是经过放大后,却发现在0xFF和0x00之间有一个Bug,波形数据为0xF0,而且这也要归功逻辑分析仪拥有多个量测信道和总线分析的功能,才能很容易发现这个Bug。

总线(Bus)分析功能:

相信工程师们对这各名词应该是很熟悉,因为在产品的研发上,处处都可以看得到它的身影,如数据总线(Data Bus)、地址总线(Address Bus)和控制总线(Control Bus)等,它的好用之处相信工程师们也应该很清楚,但是工程师对它是又爱又恨,我为什么会这样说呢 因为总线(Bus)大部分都是8~16bits不等,所以当工程师要用示波器来解读总线(Bus)里的信息时,就非常麻烦了,因为示波器最多就只有四个量测通道,所以最多一次可以同时间观察4bits的信息,所以要观察8bits信息,用示波器就要分两次来量测,并且要做记录,工程师再根据记录来判读总线(Bus)里的信息,假如要转换进制的话,工程师还要计算才会得知转换后的进制值是多少,所以用示波器来量测解读总线(Bus)是非常不明智的选择,而且浪费在此段的量测时间差不多也是占整个研发周期1/4;但是假如工程师用逻辑分析仪来量测解读总线(Bus)时,您知道会有多容易吗 因为逻辑分析仪本身就具有分析总线(Bus)的功能,您只要将要分析的八个I/O(8bits)组合起来成为一总线(Bus) (如图五),还可以专为此总线(Bus)命名,如此工程师在分析总线(Bus)时,就可以很容易的来解读总线(Bus)里的信息(如图六),并且逻辑分析仪还具备进制转换的功能,您只要选择转换后的进制种类,逻辑分析仪就会自动帮您转换,并把转换后的进制值显示出来(如图七),让您不用在浪费时间去做进制的转换计算,如此使用逻辑分析仪量测此案例,将会缩短1/5的研发周期。

图五 匯流排分析功能设定

图六 匯流排解读显示

图七 进制转换功能设定

触发功能:

说到触发功能,相信工程师们都已经很熟悉了,因为在目前所有的量测仪器当中,几乎99%都拥有此功能,只是大家的触发条件设定不同,假如工程师将触发功能应用的得心应手,那量测仪器所抓取的波形数据将会是使用者最想要分析的那一段,而不会造成让量测仪器抓取一大推的无用数据,进而浪费工程师在Debug的时间。

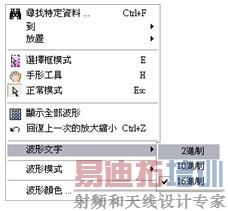

触发功能是如此的重要,但是示波器的触发功能的条件设定却只有两种边缘触发(上升缘和下降缘),而且只能单一量测通道可以设定触发条件,如此少的触发功能,相信工程师使用起来真的是苦不堪言,因为常常所撷取到的波形数据不是他所想要分析的,进而延长产品的开发时间;但是说到逻辑分析仪之触发功能,其功能之强大,要强过示波器好几千倍,您一定会认为我夸大其辞,但是相信您看完我下面之介绍,一定会改变您的想法,逻辑分析仪除了可以设定触发条件外,还有触发参考电压准位、触发位置、触发次数、触发页、触发延迟各种触发功能之应用,逻辑分析仪之触发条件设定共有六种(如图八),任意信号、高准位、低准位、上升缘、下降缘和任一边缘供工程师所需来设定,而且所有的量测信道均可以做组合触发设定,但需注意要所有触发条件同时成立时(即所有触发通道做AND),才会触发成立,光这一个触发条件设定就已经比示波器还要强大,假如工程师再加入触发位置之选择,可以同时观察触发条件成立之前后的波形数据,或是利用触发次数、触发页和触发延迟可用来分析触发后更后面的波形数据,以解决内存深度的不足,进而可以分析长时间大量的波形数据。

图八 触发条件设定

同时观看模拟和数字信号之方法:

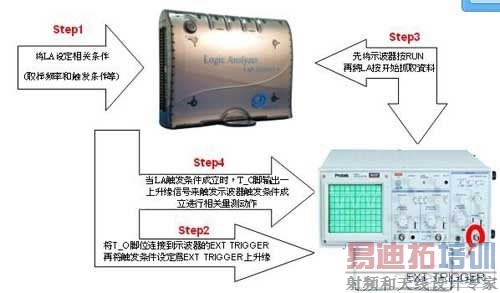

目前市场上很少有产品电路是纯数字或模拟设计,下面介绍利用逻辑分析仪之触发状态输出(Trigger Out)和示波器的外部触发源(EXT Trigger)搭配使用,用以达到在同一时间点可以同时抓取数字和模拟信号;当工程师所设定的触发条件成立时,触发状态输出(Trigger Out)脚位会输出一上升缘波形,所以当工程师想利用此信号输出来触发示波器,只需将此触发状态输出(Trigger Out)脚位连接到示波器的外部触发源(EXT Trigger),并将其触发条件设定为EXT Trigger上升缘,如此使用者只需要执行逻辑分析仪,就可以利用其触发条件成立时,即可以同时触发示波器触发条件成立来进行相关量测动作,其连接方式请看(如图九)。

图九 示波器和逻辑分析仪搭配示意图

结论:

综合前面所述的逻辑分析仪功能,只是它强大功能的冰山一角,所以逻辑分析仪在嵌入式系统的研发过程量测当中,是占有极大的关键地位,但是在目前市场整个产品研发当中,示波器和逻辑分析仪其实是要相辅相成的,如此在产品的研发时间才会更加快速,也才会更加缩短产品的上市时间,进而为公司赚取更大更多的获利,所以工程师必须对示波器和逻辑分析仪这两种量测仪器都要非常的熟悉,要如何运用个别的特性来抓取自己所需的波形数据,如何来搭配相互使用也是一大学问,这些问题都是值得工程师们去深思熟虑!