- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于AD7762和FPGA的数据采集系统设计

摘要 为了满足音频数据采集过程中对频率和分辨率等技术指标的要求,设计了一种高速数据采集装置。文中设计采用Altera公司的Cvclone系列FPGA芯片EP1C4F400在QuartusⅡ环境下使用Verilog语言控制ADI公司的AD7762A/D转换器实现数据采集。通过串口将数据传给上位机,完成数据分析和显示功能FPGA控制整个系统的采集时序。

关键词 数据采集;AD7762;FPGA;寄存器控制;串口

随着通信技术的发展,通信业务不断扩大,人们越来越重视高速数据采集和处理技术。数据采集系统主要包括增益放大器、A/D模数转换器、功能控制端。文中设计了一种以FPGA为控制核心,用于控制A/D的转换时序及数据传输的高速数据采集系统。

1 系统总体结构

设计系统以FPGA芯片EP1C4F400作为采集系统的核心控制单元,采用模数转换芯片AD7762作为数据采集的核心模块。由A/D转换后产生的数字信号通过串口传输到上位机,由上位机对数据进行一系列分析。该系统主要南前端处理模块、A/D转换控制模块、FIFO缓存模块及串口模块组成,系统如图1所示。

2 硬件设计

2.1 模数转换模块AD7762

AD7762是ADI公司近年推出的一款高性能、低功耗、并行24位Sigma-Delta模数转换芯片ADC。宽输入带宽,在625 khit·s-1时信噪比为106 dB的高速Sigma-Delta转换,使得其能够高速获得数据。片上集成用于信号缓冲的差分放大器,低通数字FIR数字滤波器,需要最少的外围设备。另外,AD7762还提供了可编程的采样速率和可调整的FIR数字滤波。AD7762要求在无复杂的前后端信号处理设计中有较高的SNR。

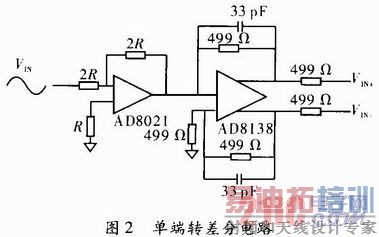

在应用正常模式下,为实现指定性能,差分放大器需要被配置为前端平滑滤波器,前端使用低噪声,高性能的运算放大器对其进行配置,实现单端信号转差分号,然后驱动AD7762。运算放大器使AD8021,差分放大器使用AD8138。信号由AD8021运算放大器输入端口接入,根据A/D输人信号的幅度标准进行输入信号幅度的调整,经由AD8138差分放大器进行单端转差分处理,之后送入模数转换器中。其电路实现如图2所示。

AD7762有许多用户可编程寄存器。控制寄存器用于设置滤波频率、滤波器配置、时钟分频器等。AD7762使用16位双向并行接口,该接口受控于![]() 。

。

2.2 主控制FPGA模块EP1C4F400

系统的主控制器采用Altera公司Cyclone系列的EP1C4F400C8N。Ahera Cyclone系列FPGA从根本上针对低成本进行设计,具有专业应用特性。器件基于成本优化的全铜1.5VSRAM工艺,输入输出电源电压是3.3 V。内核供应电压是1.425~1.575 V。Cyclone FPGA综合考虑了逻辑、存储器、锁相环(PLL)和高级I/O接口。具有专用外部存储器接口电路,支持DDRFCRAM和SDRAM器件以及SDR SDRAM存储器的连接。支持单端I/O标准如3.3 V、2.5 V、1.8 V、LVTTL、LVCMOS、PCI、和SSTL-2/3,满足当前系统需要。通过LVDS和RSDS标准提供多达129个通道的差分I/O技术支持,每个LVDS通道信号数据率高达640 Mb·s-1。FPGA中有两个锁相环(PLLs),提供6个输出和层次时钟结构,以及复杂设计的时钟管理电路。FPCA中包括17个M4K存储块。每块提供288 kbit的存储容量,能够使配置支持多种操作模式,包括RAM、ROM、FIFO及单口和双口模式。

2.3 系统后端数据传输模块

在数据传输模块中,设计调用FPGA片上资源实现FIFO缓存。存储深度为256×16 bit。由于A/D的采样频率和串口的读写频率不同,因此设计中采用读写时钟异步的FIFO。FIFO中的数据通过串口传输到上位机,设计中串口芯片采用美信公司专门为RS-232标准串口设计的单电源电平转换芯片MAX3232芯片,使用+3.3 V单电源供电。

3 软件设计

系统利用Ahera QuartusⅡ软件完成FPGA程序的编写。Altera QuartusⅡ软件提供完整的多平台设计环境,能够直接满足特定的设计需要,为FPGA开发提供全面的设计环境。QuartusⅡ开发软件支持多种设计输入方式。由于FPGA支持Verilog/VHDL混合开发,设计主要采用文本形式文件输入方式和存储器数据文件出入方式,采用的Verilog/VHDL硬件描述语言设计输入,易于实现自顶向下的设计方法,易于模块划分和复用、移植性好、通用性强,具有较好的硬件平台无关性,设计不因芯片工艺和结构的改变而改变,利于向ASIC移植。

3.1 A/D转换器的控制寄存器

A/D时序分为写时序和读时序。写时序控制A/D寄存器的写操作。写操作包括两部分,先写控制寄存器2,给A/D加电,控制寄存器2的地址是0X0002,高10位全部是0。低6位的内容如图3所示。

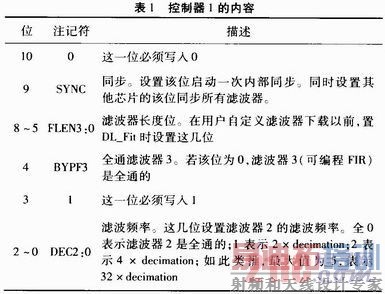

![]() 设置A/D的时钟分频比率,CDIV=1,则ICLK=MCLK。CDIV=0,则ICLK=MCLK/2。设计硬件电路中连接的时钟是MCLK=40 MHz,但A/D中允许的最大的ICLK时钟是20 MHz,需要对外部时钟进行分频,因此此位设为0。D1PD位置高将关断片上差分放大器,本设计中置0,第二位写入1。再写控制寄存器1,设置A/D的滤波频率、滤波器长度位、数据输出频率等。控制器1的内容如表1所示。

设置A/D的时钟分频比率,CDIV=1,则ICLK=MCLK。CDIV=0,则ICLK=MCLK/2。设计硬件电路中连接的时钟是MCLK=40 MHz,但A/D中允许的最大的ICLK时钟是20 MHz,需要对外部时钟进行分频,因此此位设为0。D1PD位置高将关断片上差分放大器,本设计中置0,第二位写入1。再写控制寄存器1,设置A/D的滤波频率、滤波器长度位、数据输出频率等。控制器1的内容如表1所示。

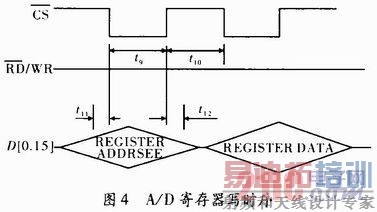

控制寄存器1的地址是0X0001,设计中控制寄存器1的内容设为0X001B。设计中通过写控制寄存器1设置输出数据频率。读时序控制A/D采样数据的输出。A/D的控制时序及工作状态如图4所示。

在寄存器写操作时![]() 始终保持高电平,由

始终保持高电平,由![]() 控制。在

控制。在![]() 为低电平期问依次将两个寄存器的地址和内容写入A/D中,控制A/D的工作状态。

为低电平期问依次将两个寄存器的地址和内容写入A/D中,控制A/D的工作状态。

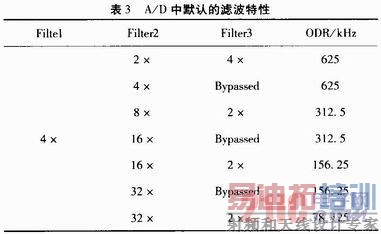

AD7762串联了3个滤波器。通过使用不同的滤波频率、滤波器选择和全通的结合,可以获得大范围的采样速率。通过设置寄存器1的低3位滤波器的状态设置数据输出速率Rate,A/D中默认的滤波特性如表3所示。

表3是在A/D内部时钟为20 MHz时,可看出当rate=3’h3时→625 kHz;rate=3→312.5 kHz;rate=4→156.25 kHz;rate=5→78.125 kHz。

3.2 A/D读时序控制

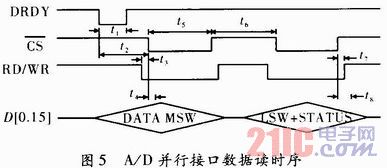

AD7762的读时序如图5所示。

A/D寄存器写成功后,A/D会根据寄存器设置的工作状态进行数据采样和传输。当一个新的转换数据结果有效时,A/D的![]() 引脚会产生一个低脉冲信号送给FPGA,当FPGA接收到这个低脉冲信号时开始接收A/D的采样数据。由于AD7762是24位分辨率的A/D转换器,而外部是16位数据线,所以从AD7762中读取一个转换结果,需要执行两次16 bit读数据操作。当

引脚会产生一个低脉冲信号送给FPGA,当FPGA接收到这个低脉冲信号时开始接收A/D的采样数据。由于AD7762是24位分辨率的A/D转换器,而外部是16位数据线,所以从AD7762中读取一个转换结果,需要执行两次16 bit读数据操作。当![]() 同时为低电平时,数据总线开始传播数据。在二次读操作之间,

同时为低电平时,数据总线开始传播数据。在二次读操作之间,![]() 必须置高一个ICLK周期的高电平。数据传输结束后

必须置高一个ICLK周期的高电平。数据传输结束后![]() 保持高电平,数据线处于高阻态,等待下一次有效数据的传输。

保持高电平,数据线处于高阻态,等待下一次有效数据的传输。

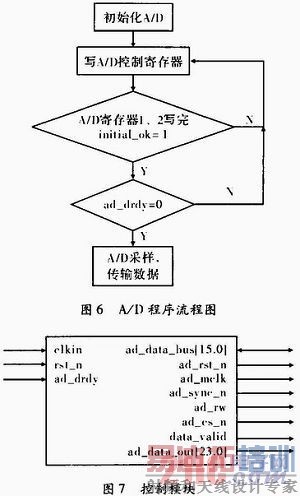

控制A/D的程序流程图如图6所示。程序编译后生成的A/D转换器的控制模块如图7所示。

模块中ad_data_bus[15.0]与FPGA的IO口进行连接。ad_rst_n是A/D的复位信号,而rst_n是系统的复位信号。ad_mclk外接40 MHz晶振,进入A/D后经过寄存器设置进行二分频。ad_sync是同步信号,可以同步多片ADC,此处不操作。

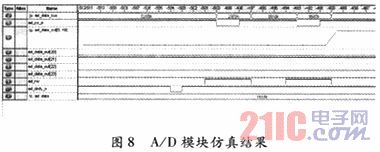

将程序通过FPGA的JTAG口下载到硬件系统,进行仿真得到的A/D模块仿真结果如图8所示。

对A/D进行仿真。从仿真图中可以看出,A/D产生![]() 低电平后才开始根据

低电平后才开始根据![]() 的高低电平控制传输数据。

的高低电平控制传输数据。

3.3 FIFO数据缓存模块

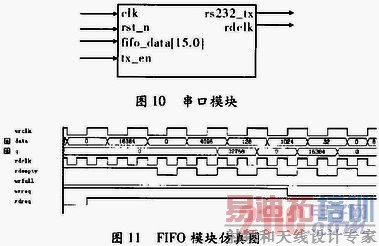

FIFO用于存储FPGA接收的A/D采集的数据,FIFO模块的读时钟受前端A/D模块巾的data_valid信号控制,写时钟由后面的串口模块产生,已达到FIFO数据读取与串口传输的数据一致。保证数据准确地通过串口传输到上位机。FIFO的读写控制信号分别由wrfull和rdempty控制,FIFO模缺如图9所示。

3.4 串口数据传输模块

串口模块的开启和关闭信号tx_en受FIFO模块的读信号rdreq控制。

4 结束语

数据采集系统设计中,AD7762内部设置差分放大器和灵活设置的寄存器,使得外部的电路设计简单且成本低。FPGA控制更为灵活方便,若想改变A/D的工作状态只需要更改寄存器的设置内容即可。减少外部控制线的数量,使系统减小干扰,更为可靠。若将此系统作为音频信号分析系统的前端,将使整个系统的稳定度及精确度得到提高。

上一篇:TEK:简化高速串行数据调试验证和一致性测试问答(二)

下一篇:TEK:简化高速串行数据调试验证和一致性测试问答(一)