- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DM642的实时多协议转换器设计

摘要:为了解决虚拟试验系统中具有不同总线类型的各实物子系统互联的实时性问题,设计了一种多协议转换器。按协议高低优先级分配软硬件资源,硬件设计采用DM642+FPGA的结构,使用FPGA实时匹配高优先级协议,并对DM642分类返回不同中断信息;软件设计时,按地址分块存储协议以提高的协议的查找效率,并根据DSP/BIOS中各类线程的特点,合理分配任务并分类触发不同任务,以加快数据处理速度并保证高优先级协议实时性。

关键词:多协议转换器;实时性;DM642;DSP/BIOS

0 引言

在虚拟试验系统中,需要将不同总线类型和不同传输协议的各实物子系统进行互联,实物设备子系统常采用1553B,ARINC429,RS 232等总线,协议转换的实时性对整个虚拟试验系统试验结果的真实性具有重要的影响,因此设计了基于DM642的实时多协议转换器。

协议转换方法有过程控制级转换和现场设备级实现。OPC(OLE for Process Control)为最常用控制级转换方法,所有的工作全部在上位机中由软件完成,简单方便,但总线系统中节点间的通信较慢,实时性较差。采用现场设备级转换方法的协议,如Profibus,DeviceNet等,需专门开发软硬件,但可以实现差异较大协议总线间的转换,可以满足实时性要求。曾翠荣等采用现场设备级转换方法,设计出通用报文格式和地址分配方法,简单明了,但不同总线协议间的转换必须借助于上位机和网络,仅满足传输延时小于20 ms。本文借鉴现场设备级转换方法,设计了一种高实时多协议的转换器。设计中,采用C6000系列高速DSP,将协议分为高低优先级,采用FPGA实时识别高优先级协议,按地址块存储协议描述信息,使用了DSP/BIOS提供的不同类型线程,并采用触发不同消息的方法跳转线程,有效地保证了实时性。

1 协议传输格式及描述方法

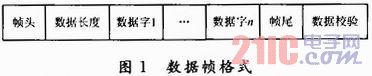

虚拟试验系统中不同总线上传输的数据流通常按如图1所示的方式传输,一帧数据由帧头、数据长度、数据体、帧尾、数据校验等组成,帧头标志不同协议,帧尾或帧长标志该帧数据流的长度,帧头和帧尾可以是1个、2个或者4个数据字,数据体由多个数据字组成。但协议以数据元素作为基本单位进行编解码,数据元素由一个或多个数据字组成,有具体的物理含义,可以表示一个具体的物理量,也可以按位表示多个不同的工作状态。协议解码时,先根据帧头识别出协议类型,然后根据数据长度或帧尾提取出数据体,再按协议提取出数据元素,将数据元素乘以或加上特定系数转换为具体物理意义数据,或提取出每一状态位;编码过程为解码的逆过程。

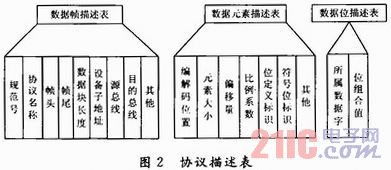

为便于协议的识别、编解码,建立由数据帧、数据元素、数据位三级描述结构体组成的协议描述表,各级协议描述结构体所描述的信息如图2所示。

2 硬件设计

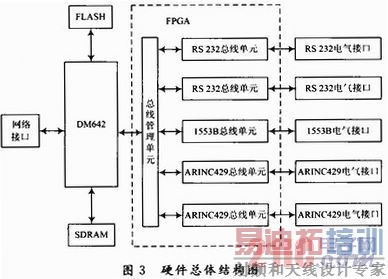

本系统采用如图3所示的DM642+FPGA的设计方式,实现了双通道RS 232总线、双通道ARINC429,单通道双冗余1553B总线以及LAN总线的通信。DM642为TI公司的C6000系列高速DSP,其主频最高可达720 MHz,数据处理能力达4 800 MIPS,其收发通道独立的EMAC和MDIO可以很好的支持10 Mb/s和100 Mb/s以太网。DM642还扩展32 MB SDRAM和8 MB FLASH,用于缓存数据和存储协议。FPGA选择Altera公司的EP3C55F4 84,其LE单元、储存单元、可用I/O均比较丰富。DM642实现以太网接口,控制系统并完成协议的编解码。FPGA中的总线单元实现RS 232等总线的物理层收发,总线管理单元协调DM642与各总线单元间的通信。采用专业芯片实现各总线的电气转换。

总线管理单元管理各总线,并协调各总线与DM642的通信。为防止总线冲突,总线管理单元中记录DM642及RS 232等总线单元的工作状态。1553B总线与RS 232总线和ARINC429总线不同,其收发是相关的,无论其收发数据时,总线管理单元都视其被占用。当DM642处理高优先级协议时,总线管理单元将对DM642屏蔽低优先级协议产生的中断,直至DM642完成相应数据处理。对为了防止总线被“锁死”,总线管理单元对超过一定时长处于忙状态而未被使用的总线复位,并对DM642产生总线异常中断。

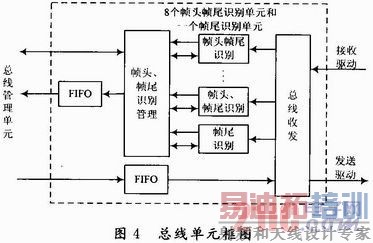

每个总线单元都采用如图4所示的结构,“总线收发”实现相应总线物理层收发。在总线单元中实现8个帧头识别单元和一个帧尾识别单元,实时匹配和提取协议。帧头识别单元记录有高优先级协议的帧头、帧尾、帧长等信息,DM642在识别出低优先级协议后,将该协议的帧尾、帧长等信息写入帧尾识别单元。无论是DM642还是任一帧头帧尾识别单元协议匹配成功后,帧头帧尾识别管理单元都将使其它帧头帧尾识别单元处于非工作状态,在该帧头帧尾识别单元根据帧尾或帧长提取完协议后,其它帧头帧尾识别单元将再次使能。帧头帧尾识别管理单元在识别出协议和完成协议提取时,将向总线管理单元产生不同中断。总线发送FIFO由非空变为空,也产生发送完成中断。

3 软件设计

3.1 协议存储、加载方法

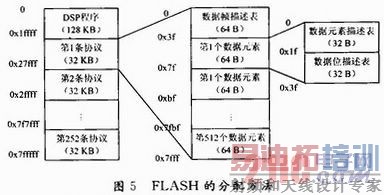

为了使上电复位后无需重新加载协议,将协议描述表存储于FLASH中,FLASH的分配方法的存储空间分配方法如图5所示。

8 MB存储空间的前128 KB存储空间用于存储DSP程序,剩余的空间划分为252个32 KB大小的数据块,每个数据块用于存储一条协议的所有信息;每个32 KB大小数据块在划分为512个64 B大小的次级数据块,第1个次级数据块用于存储数据帧描述表,后511个次级数据块存储数据元素的相关信息;64 B存储空间的前32 B用于存储数据元素描述表,后32 B用于存储数据位描述表,同一个数据元素最多支持8个数据位操作。采用这种协议存储方法的好处是,方便了协议的加载及修改,DM642很容易计算出每个数据帧、数据元素、数据位描述表的地址,加快了协议信息的查找,但对存储空间的浪费也比较大。

3.2 DSP程序设计

软件程序调用CCS 2提供实时操作系统DSP/BIOS,DSP/BIOS采用抢先式多任务内核,支持硬件中断、软件中断、任务、后台线程等4种线程,并提了同步机制。在DSP/BIOS下调用NDK的函数库进行TCP/IP协议编程时,需配置EMAC并开启线程监控网络接口,参考文献详细介绍了DSP/BIOS下的TCP/IP协议编程,这里把网络总线视为普通接口。

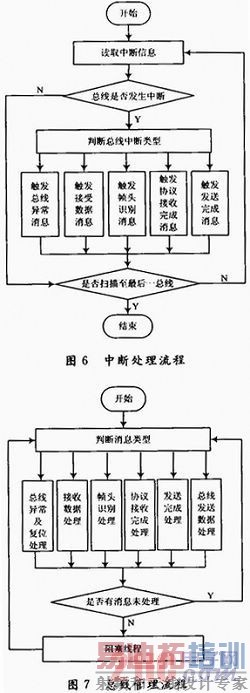

为了保证系统实时性,需合理使用DSP/BIOS提供的不同类型线程,并协调好各线程间的通信。协议及各总线的配置数据均存储于FLAS-H,也上电后通过以太网在线动态加载至DM642。在主线程中对DM642和FPGA进行初始化配置。硬件中断的实时性最高,监控各总线状态,并根据从FPGA读回的中断信息,生成相应消息并触发软件中断和线程。硬件中断的流程如图6所示,依次扫描各总线中断信息,根据中断信息触发总线异常、接收数据、帧头识别、协议接收完成、发送完成等中断的处理程序。

在接收数据所遵从的传输协议未知时,先触发软件中断识别协议类型,在传输协议已知时,直接触发总线管理线程。任务可以被阻塞和挂起,支持动态内存分配等API函数,对以太网及RS 232等总线建立线程分别建立总线管理线程。各总线管理线程的流程如图7所示,根据触发的消息类型,建立和释放缓冲区,编解码协议,触发数据发送总线,监控总线状态,协调总线发送通道的使用。在识别出传输协议为高优先级协议时,总线管理线程会调用API函数提高自身优先级,以达到抢占CPU的目的,处理完协议后会再次恢复以前的优先级。软件中断优先级低于硬件中断,对堆栈要求小,用于低优先级协议的帧头识别。采用触发跳转至相应处理程序的方法可以加快数据处理,保证高优先级协议的实时性。各级线程都会尽量在等待数据或资源时跳转至阻塞状态,以便释放CPU。

4 结语

本设计采用以下几个方法保证多协议转换实时性:采用高速DSP加快数据处理速度;将协议分为高低优先级,采用FPGA实时识别高优先级协议,大大提高了高优先级协议匹配速度;按地址将协议的帧描述表、数据元素描述表、数据位描述表等信息存储与FLAsH,提高了协议信息的查找效率;使用了DSP/BIOS提供的不同类型线程,并采用触发不同消息的方法跳转线程,提高了数据处理效率,并保证了高优先级协议优先编解码。FPGA识别协议、DM642编解码、线程转换所产生的延时均为微秒级至几十微秒级,因此本设计在一定程度上可以保证对高优先级协议单个数据元素的编解码延时小于1 ms,但在支持协议的通用性上可以进一步研究。