- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

数据采集系统设计

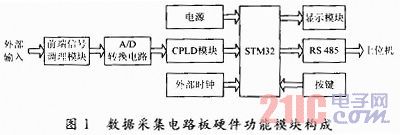

摘要:设计一种基于STM32和CPLD的数据采集系统,实现现场数据的采集、传输、显示和存储。数据采集过程由CPLD控制,采用Verilog HDL语言设计输入通道选通和A/D采集控制程序,进行数据的滤波、放大、转换,实现多通道数据的采集;在STM32中实现数据处理、传输,并在PC机中开发上层数据管理软件,实现数据的显示、存储。系统可实现多通道数据采集实时显示的要求,电路设计方法简单、可靠性高,能满足实际应用的要求。

关键词:STM32;CPLD;实时数据;数据管理

0 引言

随着自动控制和计算机技术的成熟和发展,以及它们和传统工业的结合,加工设备的自动化程度有了大幅度的提高,各种控制设备与控制技术得到了广泛应用,大大提高了加工制造的效率,当然这种高效的生产对检测量的精确性和实时性也提出了更高的要求,而依靠传统的数据采集方法(即由操作工人凭借简易测量工具进行测量)已无法满足这种要求。

目前,生产设备的参数采集手段主要有便携式检测仪和在线检测系统,采用便携式仪器需要花费大量的人力和时间,采集到的数据不能实时反映设备加工的状态,具有一定局限性;一般的在线检测系统,检测数据相对单一,不能满足多成分分析的需要;对于一些大型的在线检测系统,虽然能满足实时检测和精度要求,但系统体积庞大、投资多、难以推广使用,并且国内很多在线检测系统,对检测到的数据缺乏综合利用和管理,不能很好地为工艺和装置的优化节能及节能减耗改造服务。因此开发出具有实时数据采集、存储、传输等功能的在线数据采集系统是十分必要的。

1 系统的整体方案与工作原理

数据采集系统是基于CPLD和STM32的弱信号采集电路,可用于各种弱信号检测的应用研究中,整个系统由信号滤波、信号放大、数据采样处理和主计算机传输接口等组成。信号滤波防止信号产生“混叠现象”;信号放大对输入信号进行调理,使信号在A/D转换能够转换的电压范围内,以满足采样的要求;数据采样处理完成模拟信号的采样保持和数字化;与主计算机的数据接口,将数据上传给计算机,满足信号检测的实时性,进行数据的存储、显示等。数据采集电路板硬件功能模块构成如图1所示。

2 系统硬件结构

整个系统由信号预处理、信号采集和数据传输三大模块组成,其中信号预处理进行信号滤波、信号放大,预处理模块由MC1558,MC1556等组成;信号采集进行信号选通、A/D转换;信号采集模块由AD508、A/D转换芯片、CPLD组成;数据传输进行数据的软件滤波、通过通信口与上位机进行通信,数据传输由STM32芯片、信号输出接口模块组成。

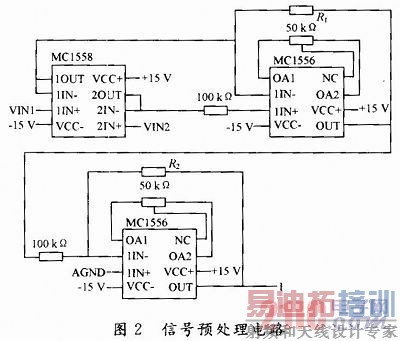

2.1 信号预处理电路

由于待采集电压信号输入动态范围较宽,且极性各异,采用输入电压范围可调的信号预处理电路。信号预处理电路如图2所示,信号放大倍数为R1×R2/(100×100)。

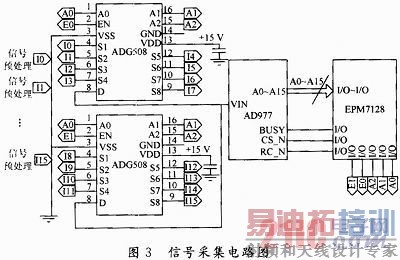

2.2 信号采集模块

CPLD是在PAL、GAL等逻辑器件的基础上发展起来的,同以往的GAL、PAL等相比,CPLD的规模比较大,适合于时序、组合等逻辑电路的应用场合。采用Altera公司的EPM7128SQI100作为数据采集的控制芯片,负责信号采样、A/D转换、数据输入控制等。EPM7128SQI100具有128个宏单元,84个用户I/O管脚,工作电压为5.0 V,具有2 500个可用门和ISP,管脚间延迟为6.0 ns,计数器速度可高达125 MHz,可以很好地满足系统的需要。信号采集电路如图3所示。

ADG508是一款8通道CMOS模拟多路选择器,具有高速转换速度和低内阻特性,通道切换具有防短路功能。在CPLD控制下,它可对采集信号进行有序通道切换。A/D转换芯片选用AD977,AD977是ADI(Analog Devices)公司推出的一款高速16位A/D转换器,输入电压范围为-10~+10 V,单极5 V电压供电,采样频率可达100kHz。数据采样系统最大采样速率可达50kHz,信号分辨率可达0.3mV。通过采用多路转换开关ADG508与16位A/D配合使用,降低了成本。

2.3 数据传输模块

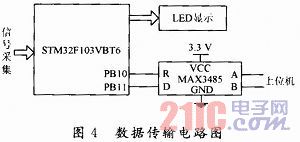

STM32是数据通信芯片,主要负责数据处理、传输控制、参数设置等。采用STM32F103xB系列ARM芯片,该系列芯片是意法半导体基于Con tex-M3内核的32位微处理器,可以满足高性能、低功耗和低成本特性的嵌入式应用。芯片具备72 MHz时钟频率,拥有丰富的外设装置,包括128 KB嵌入式闪存、20 KB的SRAM、两个ADC接口、三个UART、支持USB、CAN和七个DMA通道等丰富的外围模块,以其高速的指令执行速度、方便的JTAG调试方式和低功耗等特性为数据采集与处理的设计提供了一个较为完善的平台。数据传输电路如图4所示。

STM32F103VBT6的所有I/O端口兼容CMOS和TTL,在5V引脚上的输入电压最小值为-0.3 V,最大值为5.5 V,低电平电压范围为-0.5~0.8V,高电平电压范围为2.0~5.0V,经EPM7128输出的数据直接与STM32F103VBT6连接,简化了电路。

3 软件设计

根据设计任务的要求,系统软件主要完成数据的采集、滤波处理、串口与PC机的通信,数据采集软件由信号采集与通信模块软件、上位机监控软件两部分组成。

3.1 信号采集与通信模块软件设计

数据采集系统的固件驱动程序(又称单片机程序)是固化到CPU模块内的软件,采用模块化设计,主要模块包括:信号采集控制模块和数据传输模块两大部分。信号采集控制模块软件固化到CPLD中,数据通信模块软件固化到STM32中。

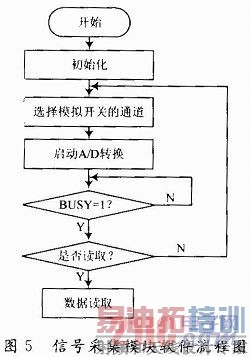

信号采集控制模块软件利用Altera公司的Quartus开发软件实现,采用Verilog HDL语言设计,主要功能包括输入通道选通、数据采样控制。通过CPLD芯片分别控制ADG508和AD977,进行模拟量输入通道的选择和启动A/D转换。数据的采集算法过程中,根据香农定理,采样频率大于被采集信号的2倍频率。信号采集模块软件流程图如图5所示。

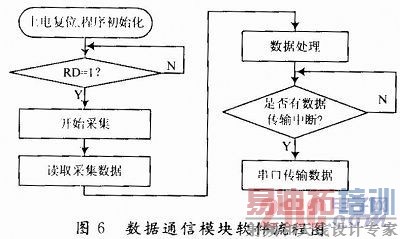

数据传输模块软件在Real View MDK环境下编写,主要功能包括数据接收、数据处理、串口通信。STM32通过握手信号启动CPLD的数据采集程序,在启动A/D转换器转换下一路信号。软件设计上,采用极值滑动平均滤波抑制叠加在模拟输入信号上的噪声;应用软件拦截技术、软件看门狗技术、故障处理自恢复技术等措施使受干扰而“跑飞”的程序回到正常的轨道上;采用I/O自检等程序预先发现故障并定位故障所在,提高系统的可靠性。数据通信模块软件流程图如图6所示。

3.2上位机监控软件设计

用户应用服务程序直接面向用户,是控制数据采集软件的最上层,不仅提供与用户交互的界面,还能通过发送各种控制命令来控制采集模块的丁作。利用微软公司开发的软件开发平台VC++6.0没计上层界面,进行数据的实时显示、存储。采用串口传输协议,将底层采集到的数据传输到上位PC机,并在VC++6.0设计的上层界面中实时显示。

制定通信协议:通信双方的波特率设定为9 600 b/s;帧格式:一个起始位,八个数据位,一个可编程的第九位,一个停止位;工作方式:PC机采用查询方式,STM32采用中断方式;功能标志:发送请求标志#0F1H,接收请求标志#0FFH;校验:通信双方采用求和校验的方式,即发送一串字符,双方计算累加和,与PC机比较,有错即重发。

4 结论

数据采集系统采用CPLD选取输入通道、控制A/D转换,实现数据采样;利用STM32具有的丰富外设接口进行数据处理、数据通信,提高了系统设计的灵活性,使系统易于升级和扩展。本系统开发周期短、运行稳定、性能可靠、使用方便。配合上位机采集界面,方便进行操作使用以及各种采样数据的存储,在多种模拟量输入的数据采集和控制系统的应用中前景十分广阔,将数据采集系统应用到工业现场数据的采集中将是本研究下一步将要进行的工作。