- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ADSP-TS201S的二维DMA数据传输

摘要:针对高速信号处理系统中数据总线传输的瓶颈问题,采用二维DMA方式进行外设高速缓存到DSP内核的数据块实时传输。对二维DMA控制和状态寄存器组进行编程控制,结合FPGA与DSP链路接口设计,将存储区的数据块作为一个数据阵列进行传输,使DSP在DMA中断中获得数据。试验结果证明,二维DMA传输方式可解决高速外设数据块的连续传输和处理问题,保证整个系统并行信号处理流水线的顺序执行,是一种解决数据总线传输瓶颈问题的实用方法。目前该技术已成功应用于某水声测量系统中。

关键词:ADSP-TS201;二维DMA;LVDS;链路口

0 引言

随着数字滤波技术在水声信号处理中的广泛应用,在降低系统硬件复杂度的同时,对数字信号处理的实时性也提出了更高要求。数字滤波器处理后的大量数据需要实时高效地传输给DSP内核,以便进行相应的数字信号处理;为了提高工作效率,信号处理系统通常会采用流水线操作。另外为了不打断系统的运行流水线,数据传输不仅要满足实时高速传输的要求,还需具备DSP内核并行处理的排列顺序要求。

DMA(Direct Memory Access)是在处理器内核不干预情况下的后台高速数据传送机制,不占用DSP内核的处理时间,特别是二维DMA数据传输方式,能够将数据块按要求顺序传输。本文以ADSP-TS201S(以下简称TS201)为例,针对二维DMA数据传输方式进行探讨。

1 TS201的DMA传输

1.1 DMA简介与分析

TS201内核工作频率高达600 MHz,是一款性能极高的静态超标量处理器,专对复杂信号处理任务和通信结构进行了优化,其Tiger SHA RC静态超标量结构使DSP每周期能够同时执行4条指令,24个16位定点运算和6个浮点运算。支持14个DMA通道,可完成片内存储器、片外存储器、存储器映射外设、链路口、主机处理器和其他处理器(如FPGA)之间的低开销高速传输。TS201片内的DMA控制器允许将数据传输作为一个后台任务执行,从而将处理器核释放出来,进行其他数字信号处理操作。在复杂信号处理系统中,特别是需要大量数据传输和搬移的操作系统,采用DMA方式可以释放处理器内核,提高工作效率。

1.2 TS201的链路口DMA

TS210具有适合多DSP并行处理的突破性体系结构,除了多条独立的128位宽数据总线外,具有4位宽的4个双向LVDS(Low Voltage Differ ential Signaling)链路口是其组成并行系统的关键。链路口可以直接由处理器核控制,也可以由DMA控制器控制,每个链路口的接收和发送都有指定的DMA通道。通过编程控制可以将链路口设置成4位并行或者1位的方式进行传输。

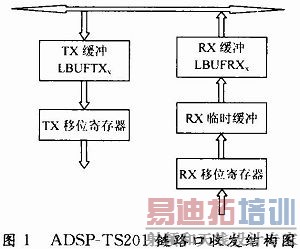

TS201链路口通过写TX缓冲寄存器完成数据的发送,读取RX缓冲寄存器数据完成数据的接收。只要TX移位寄存器为空,所有写TX缓冲区的数据都会拷贝到移位寄存器。当RX移位寄存器为空,或者RX缓冲器有多余的空间可以从RX移位寄存器接收完整的4个字的接收数据时,接收方才允许数据输入。RX缓冲器为空,有4个字的接收已经完成,才会从移位寄存器读入数据。如果RX缓冲器已满,会将数据拷贝至RX临时接收缓冲器内,一直保持到RX缓冲器为空。片上每个链路口都与2个DMA通道相连,分别进行数据的发送和接收。2个DMA通道都与内部寄存器、外部寄存器及其他链路口缓冲器相连接。链路口收发结构见图1所示。

1.3 二维DMA

TS201可以寻址和传输1个二维存储阵列,二维DMA将存储区的数据块作为1个数据阵列进行传输,这对制定矩阵操作的DSP算法十分有用。存储器中的二维存储块可以通过链路口向外发送,由链路口接收的数据块也可以按照二维存储阵列的形式保存到存储器中。接收端存储器矩阵的大小可以与发送端的不同,只要两边所含的总字节数相等即可。二维DMA的优点如下:

(1)允许任意一个矩阵区域的数据交叉存取,以一种比较直观的处理顺序将数据放入存储区。例如,将同一个A/D经过不同数字滤波器后的并行数据,以数据块的形式进行搬移,自动存入各自的高速缓存区或片内存储区。

(2)能够实时高效地完成数据块存取。DMA控制器和DSP内核同时存取向不同存储块的操作均可在一个时钟周期内完成。例如,当DSP内核对一子存储块的数据进行操作时,DMA可以向另一个存储块存放数据。在某些条件下,甚至可以同时访问同一个存储块。

(3)允许有选择的数据传输,即只选择需要的输入数据块而不是全部数据。例如,系统在处理不同通道的数据时,可以在二维DMA传输过程中进行数据的实时更改与选择。

(4)链式二维DMA可以在DSP内核不干预的情况下进行无限制的多次DMA传输,并且每次操作的属性和I/O都可以不同。

(5)允许在一个激活的二维DMA链中插入高优先级的链式DMA,能实时实现DMA链的更新,继续二维DMA数据传输。

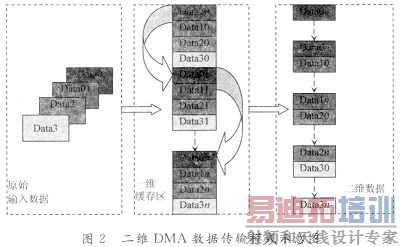

假设某系统中存在4种并行数据(如并行A/D采集数据)的二维DMA传输,通过乒乓缓存的方式进行数据的转存,其数据块二维传输过程如图2所示。

图2中的Data0…Data3表示连续产生的4路并行数据,Data00…Data0n表示Data0的n个数据块。左侧表示为原始输入数据,例如A/D数据经过数字滤波器后的4路并行数据。中间表示为高速缓存区内部的一维排列数据,右边表示经过二维DMA链路口传输后的二维数据块排列。从图中可以看出,二维DMA传输将原来不适合DSP流水线操作的数据,实时高效地传输到DSP内部,并将数据块按照流水线要求顺序排列存储。

TS201的二维DMA控制和状态寄存器组,包括DMA控制寄存器、DMA状态寄存器、清除寄存器和传输控制寄存器等。通过对寄存器组编程可以允许相应DMA产生中断,整块数据传输完毕后,DMA将产生中断。中断发生在计数寄存器减至0,而且是最后一个数据单元传输后。每个DMA控制块都有自身的中断,DMA中断会锁存在ILAT寄存器中,并由IMASK寄存器打开。但需要注意的是,DMA中的计数器必须是减到零,向计数器寄存器写零并不会产生DMA中断。

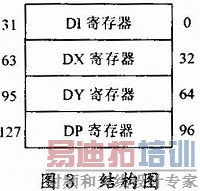

DMA传输控制块寄存器是一个128位的四字组寄存器,含有DMA块传输所需的控制信息。在DMA发送时,4个字包含了原数据的地址、将要发送的字数量、地址增量和控制位。在DMA接收时,4个字包含了目的地址、将要接收的字数据数量、地址增量和控制位,其结构如图3所示。

其中,DI寄存器是一个32位的DMA索引寄存器,它包括了将要发送或者接收的数据源地址或者目的地址,既可以指向内部寄存器和外部寄存器,也可以指向链路口。DX寄存器包含一个16位的汁数值和一个16位的修改量,计数值保存在高16位,修改量保存在低16位。如果使能了二维DMA,则该寄存器保存的只是X方向的计数值和修改量。计数值和修改量均以32位字为单位。DY寄存器和DX寄存器结合使用,该寄存器保存了Y方向上的16位修改量和16位计数值。如果只是进行一维的DMA传输,就不需要设置该寄存器。DP寄存器包含了DMA传输的所有控制信息。22位到31位包含了所有控制信息,0位到21位包含了链式信息。

一般情况下启动二维DMA的步骤如下:

(1)保存TCB DI寄存器中的当前地址,启动一个DMA存储器周期。

(2)在该周期内,将TCB DX增量寄存器中的X修改量与TCB DI寄存器中的当前地址相加。

(3)TCB DX计数寄存器内容减1,若TCB DX计数寄存器值为零,则执行第4步。

(4)重新加载TCB DX计数寄存器值。

(5)DMA寄存器中Y维增量加到TCB DI寄存器中的当前地址。

(6)TCB DX计数寄存器内容减1。

(7)若TCB DX计数寄存器值等于零,则DMA传输结束,在再次设置TCB前,需禁止它。

2 二维DMA应用

2.1 硬件设计

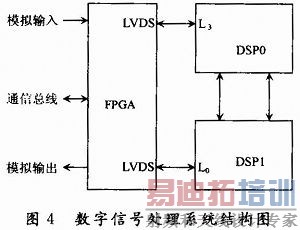

水声信号处理系统的复杂性和连续性要求信号处理系统具有较高的实时处理能力,所以设计时采用多片TS201来构成并行处理系统,以提高系统的数据处理能力。各DSP之间仅通过链路口无缝连接,片间连线少,降低了PCB布线难度和层数,节约了制板成本。此外,数据传输采用链路口的二维DMA方式,并不占用DSP内核的运算时间,可以提高处理板的实时性能,保证系统流水线操作的顺利执行。系统硬件结构图见图4所示。

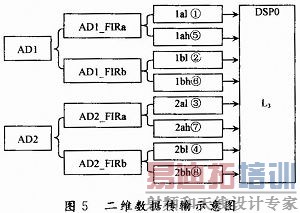

模拟输入端采用2片18位的高速A/D进行模数转换,每一片A/D的数据分别经过FPGA中的4个FIR滤波器,产生的8路并行数据通过链路口二维DMA传送给DSP组,进行相应的数字信号处理。具体数据传输框图见图5所示。

其中,①,②,…,⑧表示LVDS链路口数据传输顺序;lal表示AD1数据经过FIRa滤波器后的低1 KB数据,lah表示AD1数据经过FIRa滤波器后的高1 KB数据。滤波后的A/D数据进入乒乓缓存,最后通过链路口将数据传输到DSP内部。这里要求,在下一个数据块采样结束之前,需要完成上一个数据块的传输、滤波、相关及功率谱分析等一系列较为复杂的数据处理。由于AD1,AD2是同步采样的,经过数字滤波器的数据通过LVDS链路口顺序传输,为了减少数据块调整和挑选的时间,这里采用链路口的二维DMA传输方式,可以快捷地将A/D采集的数据块按照流水顺序写入DSP内部存储区。

2.2 软件设计

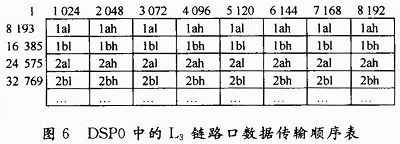

以图4中所示的FPGA与DSP0的L3链路口的二维DMA数据传输为例,假设数据块大小设定为1 024点,其链路口数据排列顺序如图6所示。

上标表示DSP0内部存储区内的偏移地址,每次DMA中断传输4×1 024个数据,即每次传输4行1 024列大小的数据,8次DMA中断即可获得一个时间片内的2个A/D采集数据经过4个FIR滤波器后的全部数据,而且数据块按照DSP0的流水线顺序排列。

DSP0软件需要完成L3链路口的初始配置和接受中断函数的设计,首先进行DSP系统时钟和UART及FIR滤波器系统的初始设置,然后进行二维DMA寄存器控制和内存块的分配,然后开启硬件A/D采集,等待二维DMA中断,进入中断后获得最终数据。软件流程见图7所示。

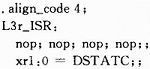

二维DMA中断处理代码如下:

其中的L3r_data为数据存储区的首地址。

3 结语

本文介绍了TS201的二维DMA传输,结合实例说明了链路口二维DMA设置及应用方法,给出软件设置流程图及关键代码。实践证明,二维DMA传输能够保证大量数据的可靠传输,同时又解决了多处理器之间共用总线所产生的I/O瓶颈问题,增强了多处理器系统的并行处理能力,提高了系统流水线运行效率。