- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电接枝技术助力高深宽比TSV

3D-IC设计者希望制作出高深宽比(HAR>10:1)硅通孔(TSV),从而设计出更小尺寸的通孔,以减小TSV通孔群在硅片上的占用空间,最终改进信号的完整性。事实上,当前传统的TSV生产供应链已落后于ITRS对其的预测。以干法和湿法工艺为基础的传统解决方案把那些专门设计应用于MEMS或双嵌入式的昂贵的工具转而应用到工艺窗边缘或工艺窗外部的工艺处理中。这样做的结果要么影响产品的性能,要么使工艺占有成本高得无法接受。当AR>5:1时,PVD薄膜会变得不连续;由于使用纳米喷涂工具,电离PVD或ALD的成本变得极其昂贵。

当前,采用一种纳米技术解决方案可实现HAR>20:1的结构,而成本只占传统工艺的一部分。这种工艺被称为电接枝技术(Electrografting),通常要沿着TSV的内壁形成表面活性共形膜。这种膜比较薄,具有连续性和粘着性,且十分均匀。这项湿法工艺使用标准电镀工具,具有极高的成本效益。

TSV对3D-IC设计的影响

虽然把TSV融入主流半导体工艺还需要解决一些技术难题,但研究TSV对3D-IC设计流程的影响却十分必要。总的来说,TSV技术革新受到性能和功能进步等设计要求的带动,相反,多芯片模块(MCM)解决方案受到技术进步的推动,却一直不被主流技术所接纳。因此,通过简要讨论3D-IC的设计问题可以对SAR TSV技术的主要推动力进行深层次分析。

我们的研究实例是一个移动通信应用的新型CPU子系统,在堆叠封装(PoP)结构中包含一个ARM11基微处理器、一个2Gb NAND存储芯片和一个1Mb DRAM芯片,带有500个I/O引脚,其中一半用于电源和接地的布线。此外,需要大约80个内部连接把三个IC连接到PoP中;这样,信号I/O的总数为330。采用低功率65nm技术制作的用于最新智能电话的三星S3C6410就是这种CPU子系统的典型实例。

为了对这一实例进行分析,我们设计了一个这种子系统的3D-IC堆叠,并使用TSV技术把3个芯片连接起来,其中小型低功率微处理器位于堆叠顶部,两个存储IC位于下部。虽然从功耗的角度来看这种安排并不一定十分理想,但考虑到对微处理器的低功耗和小尺寸要求,这种选择就显得比较合理了。当然也可以使用其它结构,不会影响从这一范例获得的结论。

让我们详细介绍一下微处理器的相关技术参数,并做出以下假设:IC尺寸为8×8mm,#信号TSV为330,#电源和接地TSV为660 (经验数据:是#信号 I/O的2倍),晶圆成本/mm2为0.10$。

假设共有1000个TSV,通孔密度可达16TSV/mm2。这样就可以计算出1000个TSV在IC上的空间占用情况。对深宽比分别为5:1、10:1和20:1的三种TSV进行了比较,前提条件是使它们保持相同的通孔深度和相同的禁用区标准。表1概况了所有相关数据并说明了硅片的实际占用情况。

表1清楚地表明了高深宽比TSV对缩小硅片面积的重要影响。节省的硅片面积随TSV深宽比的增大呈指数增长,随TSV密度的增大呈线性增长。换而言之,电接枝技术使TSV深宽比增大了3倍,使单位面积TSV的数量增加了8倍。在当前的范例中,采用深宽比为20:1的TSV取代5:1的TSV将使每个晶圆的成本收益达到731$。

信号完整性

不断缩小TSV的直径可能使信号完整性下降,这是它的不利之处。通孔排列得越紧密,串扰和其它寄生效应就会变得越明显。这个问题应当属于设计技巧的范畴,而TSV工艺限制却不属于设计问题,而应当属于设计最佳实践。举例来说,由于对TSV数量的要求不断增多,设计者便把许多TSV用作信号通孔周围的接地屏蔽。通过合理排列TSV,使每个TSV传送不同的信号, 9个小尺寸TSV的传输特性优于 1个大尺寸TSV(图1)。

电接枝技术

如上所述,电接枝技术是一种基于表面化学配方和工艺的纳米技术解决方案。它用于导体和半导体表面,通过特定先驱物分子与表面之间的原位化学反应的激发作用,使各种薄覆盖层自定向生长。它属于湿法工艺,但与电镀或喷涂工艺不同,它的化学反应发生在硅表面,而不是发生在电解容器或电解槽中。各种膜物质被直接还原到晶圆表面,最终的稳态也不呈溶液形式。膜是从表面向上生长的,而不是淀积到硅片表面,从晶圆到籽晶层形成具有高粘着性的共价键薄膜堆叠。电接枝膜能与各种形状的表面保持共形。整体工艺(隔离、势垒、籽晶)均使用标准电镀工具,工艺成本大幅度下降。

虽然电接枝技术的工艺成本只占传统工艺的一部分,但TSV深宽比>20:1时形成的隔离和金属化膜的台阶覆盖率(底部/顶部厚度比)可高达90%,且具有极好的粘接性和均匀性,能够满足各种类型的电和热-机械性能要求(表2)。

在电接枝工艺过程中,来源于偏置表面的电子可充当先驱物分子的“键合籽晶”,在第一层籽晶先驱物和表面之间形成共价化学键。这是一种不使用喷涂或旋涂工艺就能把聚合物绝缘层直接“接枝”到硅表面的有效方法。形成的第一个接植层可用作绝缘层(衬垫层),也可用作采用化学接枝技术进行势垒层淀积时的粘接促进剂。化学接枝技术与电接枝技术的原理相同,但用于非导体表面。选择专用化学材料把势垒催化剂与聚合物坚固地键合在一起。这样,通过化学接枝技术改进了势垒和聚合物之间的粘着性。然后再把湿铜籽晶电接枝到导电势垒上,即使在高深宽比TSV条件下也能形成高台阶覆盖率。电化学电解槽非常稳定;膜生长速率及厚度分别受电流密度和电荷的控制。图2示出TSV深宽比为18:1,被电接枝膜完全堆叠所覆盖的TSV的SEM截图,还清晰展示了带有隔离、阻挡和Cu籽晶的高扇形通孔的顶部近观图。

占有成本(COO)

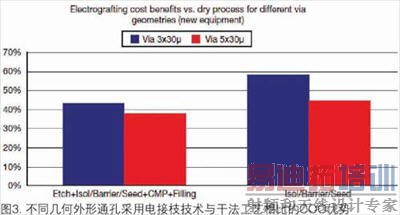

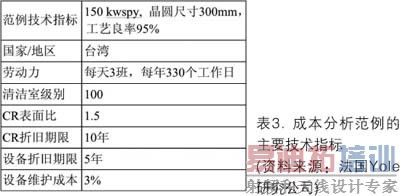

商用、批量生产电镀工具与电接枝技术所用的工具完全兼容,因此,与干法工艺相比,电接枝技术有很强的成本优势。图3对深宽比为6:1和10:1的TSV晶圆的批量生产成本优势进行了量化分析。对每个晶圆的膜淀积工艺(隔离、阻挡、籽晶)和完整的TSV制造流程(DRIE+隔离、阻挡、籽晶+CMP)的COO进行了比较。电接枝技术的成本效益远远超过了薄膜淀积工艺:在进行高速(=廉价的)DRIE工艺时,电接枝膜没有受到严重扇形边缘的影响而产生退化;由于这种膜具有高台阶覆盖率特性,晶圆表面只有少量的冗余材料需要通过CMP去除。这使TSV制造流程的总体成本下降了42%(表3)。

结论

每次对样品范例进行批次更新时,都要对基础设施进行重新改造,从而补充一些先进的技术要素。TSV也不例外,需要摆脱传统的真空基晶圆级工艺对成本和工艺的限制。电接枝技术运用了最尖端的设计原则,是一种适合批量生产的、可靠的TSV纳米制作技术。这种技术可在两方面使投资迅速得到回报:在工艺方面,与传统技术相比成本减半;在设计方面,通过使用HAR TSV使硅片的面积下降了10倍。随着当前半导体工业正从历史最低迷时期得以恢复,正是考虑资本部署的最佳时机。对于集成器件制造商(IDM)来说,要想实现专用产品的加工能力,只需要在湿法或干法ROI工艺之间做出抉择。而对于外包性半导体组装和测试供应商(OSAT)来说,就会遇到更加严峻的问题:是使用现有的制作凸点和WLP的基础设施,还是接纳前端工艺昂贵的工具购置费?一些原本具有系统级收益的前景光明的新型SiP产品,如集成无源器件(IPD)和Si中间层,可能面临更大的风险。

上一篇:基于LM317K的实用型LED照明电路

下一篇:速调管高功放维护及故障处理