- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于高速A/D转换器的视频数据采集系统

摘要:针对视频采集系统需要对摄像头输出的复合视频信号进行快速转化、采样、存储的要求,设计基于高速A/D转换器TLC551O的视频采集系统。模拟视频信号通过A/D转换器转化为8位灰度值,16位微处理器MC9S12DG128B通过普通IO口,控制FIFO存储器uPD42280写入和读取A/D转换结果,实现视频图像数据的高精度采集。分析了主要芯片的工作原理及时序,描述了软件控制图像数据采集流程。并将采得数据经过处理,与实际图像对比。实验结果表明,该系统在单行扫描时问50μs内能采集160个以上的有效像素点,成像质量高,能满足简单图像处理算法对数据的要求。

关键词:A/D转换器;FIFO存储器;时序;视频图像数据

国内外的视频图像采集方法很多,基本分为两大类:自动图像采集和基于处理器的图像采集。自动图像采集多采用专门的视频解码芯片,如SAA7113,TVP5150等,自动完成模数转化,并输出行、场信号以实现存储器地址产生,一般以DSP为主处理器,除了对采集模式进行初始化设置外,主处理器不参与采集过程。这种方法的优点是采集不占用CPU的时间,实时性较好,适合于对图像数据的精度要求较高和算法复杂的场合,如车道识别、车辆识别等方向的应用。但是该方案对处理器的速度有很高的要求,成本较高,且电路复杂。基于处理器的图像采集则采用视频同步信号分离芯片产生行、场中断信号,用微处理器内部的A/D转换器实现图像的采集。图像的采集过程在CPU控制下完成,由CPU启动A/D转换,得到转换数据。该方案的特点是电路简单,成本低,易于实现,能满足简单图像采集系统的需要。但数据采集占用CPU时间,采集速度受微处理器A/D转化时间限制。

本文提出了基于独立的高速A/D转换器TLC5510的视频采集系统设计方案,能高速采集较高精度的视频数据,可适用于智能车比赛、室内导盲、车队仿真平台、移动机器人平台等道路环境相对单一。图像处理算法简单的场合。

1 系统架构

本系统主要适用于符合PAL制式的模拟摄像头输出视频信号的采集。一般的模拟摄像头的主要工作原理是:按一定的分辨率,以隔行扫描的方式采样图像上的点,当扫描到某点时,就通过图像传感芯片将该点处图像的灰度转换成与灰度成一一对应的电压值,然后将此电压值通过视频信号端输出。同时,视频信号端输出还隐含了场同步信号、行同步信号、奇偶场同步信号等信息,因此实际输出的是复合视频信号。

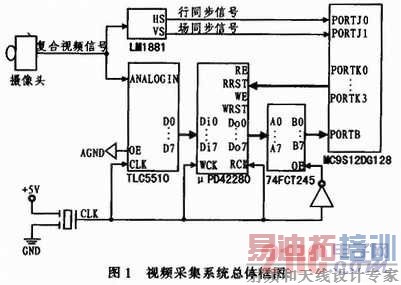

本系统采用MC9S12DGl28B作为处理器,针对信号特点,主要设计思想如下:首先,通过专门的视频同步信号分离芯片LM1881提取复合视频信号的行同步脉冲、消隐脉冲和场同步脉冲,并将它们转换成数字式电平直接输给单片机的中断口作为控制信号。同时采用高速A/D转换器TLC5510对视频信号进行A/D转换,使视频电压模拟信号转换为代表图像灰度的数字信号输出。接着采用FIFO存储器uPD42280作为视频数据的缓存,在行中断服务函数中对其进行写控制,将A/D转换数据写入其内存中。最后,当一场图像结束时,在场中断服务函数中通过单片机的8位IO口将视频数据读回。为了保证数据的稳定,在单片机与FIFO存储器之间加了一级74HC245,作为数据缓冲。为保证采集同步,LC5510 uPD42280和74HC245采用同一有源晶振作为转换和读写的时钟源。本系统框架如图1所示。

2 系统硬件设计

视频采集系统一场图像时间内的采集数据量决定了成像质量,也就是常说的分辨率或者叫像素。按照我国PAL制式的信号特点,每秒扫描25帧图像,每一帧图像又分奇偶两场,那么,一场图像的扫描时间就是20 ms。目前市场上的摄像头,不管是CCD或是CMOS成像的,纵向分辨率基本都在400线的以上。因此推得单行视频信号的持续时间小于20 ms/400=50μs左右。那么,如何在50μs内对视频信号进行快速地A/D转换,得到更多的灰度值数据,以提高横向分辨率就成为视频采集系统设计的关键问题。

2.1 高速A/D转换器

TLC5510是美国TI公司生产CMOS,8位高阻抗并行的模数转换器件(ADC)。它采用+5 V单电源工作,能提供的最大采样率为20 MSPS。TLC-551O的满输入量程是2 V,TLC551OA的满输入量程是4 V。TLC5510采用了半闪速结构及CMOS工艺,所以大大减少了器件中比较器的数量,并在高速转换的同时能够保持较低的功耗。在推荐的工作条件下,TLC5510的功耗仅为130 mW。

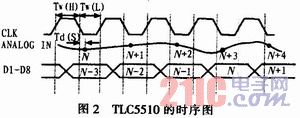

TLC5510模数转换器内含时钟发生器、内部基准电压分压器、1套高4位采样比较器、编码器、锁存器、2套低4位采样比较器、编码器和1个低4位锁存器等电路。TLC5510的外部时钟信号CLK通过其内部的时钟发生器可产生3路内部时钟,以驱动3组采样比较器。基准电压分压器则可用来为这3组比较器提供基准电压。输出A/D信号的高4位由高4位编码器直接提供,而低4位的采样数据则由2个低4位的编码器交替提供。 TLC551O的工作时序如图2所示。时钟信号CLK在每一个下降沿采集模拟输入信号。第N次采集的数据经过2.5个时钟周期的延迟后送到内部数据总线上。此时如果输出使能端OE有效,则数据可送至8位数据总线上。

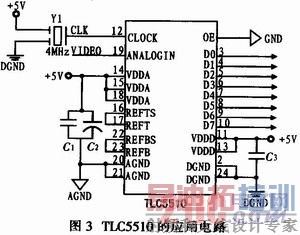

TLC5510不仅具有高速的A/D转换功能,还带有内部采样和保持电路,从而大大简化了外围电路的设计。只需要使用内部基准电阻和VDDA构成基准分压器即可实现2V的满量程转换范围。因为正常的复合视频信号最大电压值不超过2V,所以在本系统设计过程中,将TLC5510的REF-BS端短接至REFB端,REFTS端短接至REFT端,从而获得2V基准电压。视屏信号从ANALOGIN引脚输入,同时采用4MHz的有源晶振提供时钟信号。通过计算可知,该芯片在单行视频信号扫描时间内可进行200次的A/D转换,对于简单图像算法而言,横向分辨率已完全能够满足要求。如果提高TLC5510工作时钟频率,可以继续提高横向分辨率。若使TLC5510工作在极限情况下(20 MHz的采样率),横向分辨率可达到约800个点,也就是30万像素以上。上电以后,由于将TLC5510的OE引脚接到GND,芯片始终处于低有效状态,所以A/D转换将持续工作。8位数据输出直接接到下一级FIFO存储器的输入,由处理器决定存储器是否将A/D转换数据写入。

具体的应用电路如图3所示。需要注意的是,因为TLC5510的AGND引脚和DGND引脚在内部没有连接,所以在外部需要连接。建议采用电感或磁珠连接,用以去除模拟地对数字信号的噪声。同时,在VDDA与AGND,VDDD与DGND引脚之间,应分别使用0.1 μF的电容去耦,建议使用陶瓷电容,并配以10 μF以上的钽电容储能。

2.2 FIFO存储器

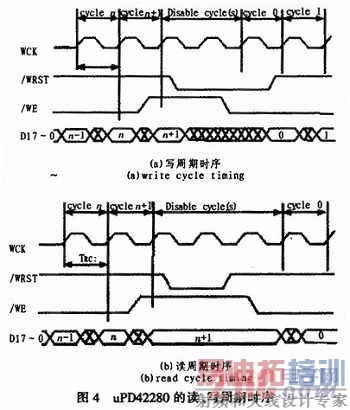

uPD42280是一种2 Mbit的双口FIFO(先入先出)存储器。在本系统中作为A/D转换数据的缓存,容量大且性价比较高,能满足一帧图像数据约25万个像素点存储的要求。A/D转换数据按照一定的时钟节拍顺序写入或读出,它的读写时钟速率最高可达33 MHz。uPD42280本身的数据是8 bit并行输入输出,通过控制它的WE引脚、WRST引脚、RE引脚和RRST引脚的电平高低,实现数据的写入和读取。图4为uPD42280的读、写周期时序。

在写控制周期,WE若处于低有效状态(WRST此时为高电平),数据在下一周期上升沿到来前写入存储器地址中;WE若处于高禁能状态。写入暂停,写地址指针保持。在WE处于低有效状态时。若WRST处于低电平,则写地址指针将从当前地址回到地址0,WRST回复高电平后,数据也将从地址0开始写入。在读控制周期,RE若处于低有效状态(RRST此时为高电平),数据在下一周期上升沿到时被读取;RE若处于高禁能状态,读取暂停,读地址指针保持。在RE处于低有效状态时,若RRST处于低电平,则读地址指针将从当前地址回到地址0,RRST回复高电平后,数据也将从地址0开始读取。

在本系统中,uPD42280的读写时钟与TLC5510的工作时钟使用同一信号源(4 MHz),既保证了FIFO的写操作与A/D转换操作的同步,避免出现数据漏接或混接现象,又可以使数据读取时,读取速率仅由处理器IO口的读取时间决定。通过处理器IO口控制读、写使能信号,读、写地址复位信号,可完成一帧图像数据的读写和更新。在处理器的总线频率为32 MHz时,单行视屏信号扫描时间内(约50 us),IO口最终可读入约190个有效像素的灰度值。去除行消隐区和图像中心对正需要省略的点,本系统每行视频信号可采集到的有效像素点为160个。

需要注意的是,uPD42280本身外围电路很简单,只需要在电源与地之间加1个去耦电容即可。但是由于FIFO存储器有别于RAM,是不能进行内部寻址操作的,只能是简单的地址复位。所以在软件控制时一定要注意逻辑,严格按照读写时序去控制4个引脚,才能保证一场图像的完整写入和读取。

本系统创新之处在于将高速A/D转换器TLC5510与FIFO存储器uPD42280联合使用,实现视频信号的转换和数据存储。这样做使得整个前端的转换和存储完全由几个IO口控制,对单片机本身的性能要求低、资源要求少,仅仅用到了单片机的两路中断和多路普通IO口。这样的设计使得本系统移植性很强,可用于多种单片机或DSP。并且这两款核心器件都是8 bit并行数据输入输出,速度很快,可以实现视频数据的高速传输。

3 软件流程

软件部分主要包括初始化、写操作、读操作和图像处理。首先将处理器的IO口,中断口初始化,PORTB8位作为数据入口,输入使能;PORTK0~PORTK3作为存储器的读写使能和地址控制线,输出使能,PORTJ0、PORTJ1分别响应行、场中断,上升沿触发。

主函数是一个无限循环,不断检测图像是否采集完成,如果采集完成则进行图像处理,然后作出相应的控制输出。场中断服务函数的主要功能是将行计数器清零,写地址回零,为新一帧图像作准备。行中断服务函数主要功能是行计数器自加,用以判断图像当前的行数。判断采集是否开始,控制写入使能,判断采集是否结束,控制写入禁能,控制读取地址回零,读取使能,将数据经过一级缓冲,通过8位数据总线读入单片机的二维数组中,并通知主函数图像数据准备好了。具体流程如图5所示。

4 实验数据

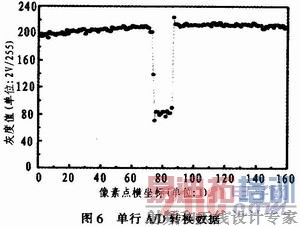

实验环境是白底黑线的模型跑道,一场图像数据的实际采集像素点为160个x20行,图像处理的算法主要是边缘检测和一次线性插值,目的是得到跑道的中心线轨迹。图6所示为单行A/D转换数据,其中灰度值高的对应白板,灰度值低的对应黑线,横坐标为每个采样点在实际图像中的X轴的比例坐标,量纲是1。

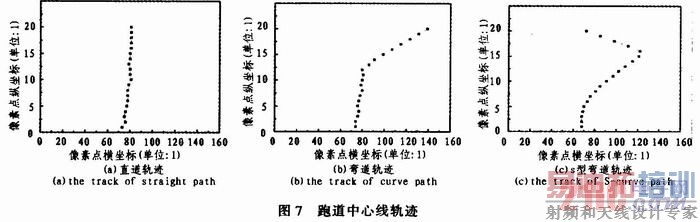

图7所示为该系统对不同道路类型的识别情况,上边是摄像头拍摄的实际图像,下边是图像数据经边缘检测和线性插值处理之后得到的中心线轨迹。横坐标为每行中心线在实际图像中的X轴的比例坐标,纵坐标为每行中心线在实际图像中的Y轴的比例坐标,量纲为1。该横、纵坐标可以通过对图像的实际测量标定得到现实世界的二维坐标。再将对应值存入单片机一个静态的二维数组中,控制需要时通过查表提取使用;也可以根据三维坐标变化计算得出。

可以看出,在跑道中心线轨迹与实际图像符合得较好。曲线的轨迹能很好地反映跑道特征,从而较为容易地判断跑道类型,为下一步控制策略提供了可靠的信息依据。

5 结论

本文提出基于高速A/D转换器TLC5510和FIFO存储器uPD42102的视频采集系统,为普通单片机实现视频信号的高速、高精度采集提供了一种新思路。该系统电路简单稳定,移植性较强,对徽处理器要求低,可适用于绝大多数CCD或CMOS摄像头输出的复合视频信号采集。实验证明,该系统可以为图像处理提供可靠的前端硬件平台。