- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

测试小型存储器阵列的新方法

传统上,测试数字集成电路可以采用功能性向量,或是由自动测试向量生成(ATPG)工具所产生的向量。此类软件工具主要为随机逻辑生成基于扫描的测试向量,对于待测组件(DUT)的存储器部分,却无法提供测试方案。得依赖存储器内建自测试(BIST)的方法来测试寄存器。

尤其是那些采用先进工艺的存储器阵列,存在着许多难以预测的潜在瑕疵。传统的存储器BIST方案会利用March或其它算法重复简单的测试序列来侦测大部分的寄存器故障。在一种存储器BIST方法中,DUT中的状态机自身能产生和分析那些测试存储器中的每一个地址所需用到的测试向量,免去了外部ATE机的测试工作。另一种方法,则是让片上处理器来测试存储器,其缺点在于通常得等到DUT设计接近完成的时候,才能判断出这种方法的有效性。

由于会影响芯片的面积与性能,小型存储器阵列通常并不适合增加存储器BIST逻辑。那些地址空间很少但端口很多的存储器尤其不适合BIST。因为相对于阵列大小,存储器端口数量对BIST控制电路规模的影响更大,所以,可能导致实现BIST控制电路所需的门数甚至会和存储器本身一样大。同时,BIST还要求所有存储器的输入引脚都有一个多路选择器来选择BIST信号与系统信号。对多端口存储器而言,多路选择电路会引起布线拥挤,并且导致性能的严重下降。

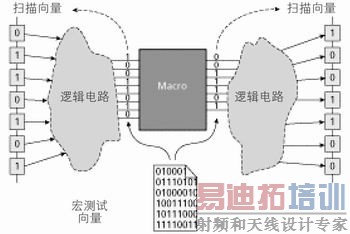

图1 宏测试采用向量转换的技术,

在扫描单元与内部宏单元,如嵌入式存储器

阵列之间传递测试向量。

嵌入式存储器测试方案

考虑到BIST对小型存储器阵列造成的负面影响,一个简单的选择便是不去测试 — 但用户极有可能会收到瑕疵品。或者,在办公室里花更多的时间,为每一个存储器阵列,手工生成完成测试算法所需的向量。好在还有一种更有效的选择 ─ 那就是利用ATPG工具和待测组件的扫描仪单元,在每一个嵌入式存储器的输入端生成测试向量,并从输出端得到响应。这项新技术,有时候被称为“向量转换”,或者是“宏测试”(macro testing)(见图1)。如此一来,工程师便可以运用一组宏向量序列,来测试独立的嵌入式模块(也可以称之为宏)。一些EDA 公司可以提供有此功能的软件工具。这些工具可以把那些为独立的嵌入式存储器(宏模块) 所设计的宏向量自动转化成芯片级扫描向量,并把结果传送到扫描单元,供作验证之用。

宏测试完成嵌入式模块所需的测试不需要附加测试逻辑电路。其次,最终的嵌入式存储器扫描向量还可以像标准的阻塞扫描向量一样,具有简单的测试协议,因此能够减少在产品测试机台上向量的调试时间。有些公司应用宏测试技术平行测试100多个存储器。如此一来,宏测试扫描向量也不过是与最长的向量长度相同。这项技术可用于测试任何嵌入式模块,即便是所谓的“黑盒子”(black box)。只要在模块的I/O端定义向量,那么这些向量便可以传递通过外围的逻辑电路。

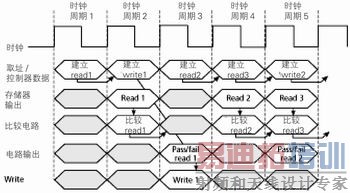

图2 流水线处理能够让连续的读/写操作在连续的

时钟周期内完成,提供全速存储器BIST功能。

嵌入式存储器中的时序故障

如同一般的随机逻辑,嵌入式存储器也需要测试静态故障和“实速”(at-speed)故障。由于存储器BIST通常在系统时钟下运行,因此也被称之为实速存储器BIST。然而,即使BIST控制逻辑利用系统时钟来设定测试序列,却需要数个时序周期去完成单独的读/写操作。因此,实速存储器BIST电路虽然采用系统时钟频率,其实并无法如同芯片在正常模式运作下那样,执行读写周期。运用流水线(pipelining)读写操作,则可产生较为有效的测试,称之为“全速”(full-speed) 存储器BIST(见图2)。简言之,便是在连续的时钟周期里,执行连续(back-to-back)的读写操作,如同在正常系统操作模式下的存储器一般。

对于大型存储器而言,测试那些与速度相关的故障时,全速存储器BIST其实是个不错的选择。但是对于小型或时序要求很高的存储器而言,同样的测试方法可能会有问题。宏测试工具要把每组功能性向量转换成扫描向量,所以每组向量的测试速度则必然变慢。不仅如此,有些嵌入式存储器完全同步,并使用与扫描链相同的时钟信号。当时钟信号触发其模块时,扫描单元上先前的设定值便会被新值所取代。如此一来,便无法传递模块输出端的期待值。因此,传统的宏测试方式无法适用于不具有门控时钟的同步存储器。

不过,同步宏测试可以解决这个问题。简言之,便是执行连续的全速测试,而不需要重复载入扫描链。同步宏测试会决定扫描单元上用来产生第一个宏向量的值,并载入扫描链。同时,也会决定用来产生第二个宏向量的值,并且在扫描单元的输入端以管道方式传输。当扫描链被载入时,不同的时钟信号即可以实速触发。如此一来,好几组的全速向量便被传送到模块。全速测试可以不受干扰地应用于设计中的几乎任一模块。不仅如此,全速测试只用到功能逻辑电路,而非测试逻辑电路,因此,可以执行更接近实际状况的全速测试。

结语

在实际测试中总是得面临测试工具的成本,测试开发时间,测试机台的时间,测试向量的调试时间,以及测试覆盖率之间的考量与抉择。宏测试是可以有效地对那些与日俱增的小型嵌入式模块进行静态与实速故障测试的工具。它甚至可以应用到较大的存储器,透过芯片的功能逻辑,自动执行全速测试。

参考文献

1 van der Goor, A.J. Testing Semiconductor Memories: Theory and Practice. John Wiley & Sons. 1991

2 Rajsuman, R. "Testing a System-On-a-Chip with Embedded Microprocessor. "Proceedings of the 1999 International Test Conference. pp. 449

08