- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR SDRAM在高速数据采集系统中的应用

在数据处理中为了更好地对被测对象进行处理和分析,研究人员们把重点更多的放在高速、高精度、高存储深度的数据采集系统的研究上

由于A/D芯片及高性能的FPGA的出现,已经可以实现高速高精度的数据处理,则进行大批量高存储深度的数据处理成为当前要解决的主要问题

l 常用存储器的比较

现在用于数据采集系统的存储器常见的有先进先出存储器(FIFO)、静态RAM和SDRAM等 FIFO由于容量和速度的限制,不是实现大容量存储的首选

FIFO由于容量和速度的限制,不是实现大容量存储的首选 目前,最为常见的存储器就是静态存储器(SRAM),静态存储器有控制简单、功耗低的优点

目前,最为常见的存储器就是静态存储器(SRAM),静态存储器有控制简单、功耗低的优点 当前大容量的SRAM可以达4 MB,存储时钟速率250 MHz

当前大容量的SRAM可以达4 MB,存储时钟速率250 MHz

如果要实现单通道32 M的存储深度和200 M的数据传输速度,就要由8×1片SRAM拼合起来才能实现 但由于每片SRAM都要有独立的地址对应存储的数据,这对设计者进行制版和布线都是一个极大的挑战

但由于每片SRAM都要有独立的地址对应存储的数据,这对设计者进行制版和布线都是一个极大的挑战 与静态存储器相比,单数据率动态存储器(SDR SDRAM)具有存储密度高、速度快等特点,数据线位宽可最大可以达到64 b,很适合于高速采样系统

与静态存储器相比,单数据率动态存储器(SDR SDRAM)具有存储密度高、速度快等特点,数据线位宽可最大可以达到64 b,很适合于高速采样系统 标准的SDR SDRAM可以达到的时钟频率达100 MHz以上,如果要满足系统存储速率的要求则至少需要有2×12 b的数据位宽,而目前并没有64 b或32 b的SDRSDRAM,则需要使用多片拼合

标准的SDR SDRAM可以达到的时钟频率达100 MHz以上,如果要满足系统存储速率的要求则至少需要有2×12 b的数据位宽,而目前并没有64 b或32 b的SDRSDRAM,则需要使用多片拼合 这样,对应于一个通道的存储就至少需要有2片12 b的动态存储器才能满足存储的需要,显然成本比较高

这样,对应于一个通道的存储就至少需要有2片12 b的动态存储器才能满足存储的需要,显然成本比较高

双速率同步动态随机访问存储器(DDR),是在SDRAM存储技术上发展而来的一种新型存储器件,在计算机行业得到了广泛的应用 其特点是采用了双倍速率结构实现高速操作,其在同一时间内传输的数据量是SDRSDRAM的2倍,最大传送数据的时钟速率可达400 MHz,而存储一个通道的数据只需要1片16 b的DDR,并且单位存储成本和SDR SDRAM相比并没有提高

其特点是采用了双倍速率结构实现高速操作,其在同一时间内传输的数据量是SDRSDRAM的2倍,最大传送数据的时钟速率可达400 MHz,而存储一个通道的数据只需要1片16 b的DDR,并且单位存储成本和SDR SDRAM相比并没有提高 因而,对于高速数据采集系统,无论从成本还是性能方面考虑,采用DDR作为系统的存储器件是合适的

因而,对于高速数据采集系统,无论从成本还是性能方面考虑,采用DDR作为系统的存储器件是合适的 但DDR却带来了相对复杂的控制工作,不仅需要与SDRSDRAM一样进行定时刷新,而且较SDRAM增加了新的控制信号和使用了新的电平标准

但DDR却带来了相对复杂的控制工作,不仅需要与SDRSDRAM一样进行定时刷新,而且较SDRAM增加了新的控制信号和使用了新的电平标准

2 DDR的基本工作原理

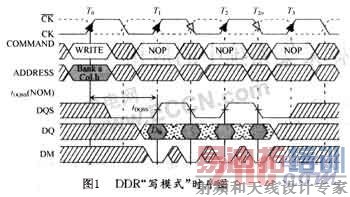

所谓DDR的双倍速率结构,即在数据随路时钟的上升沿和下升沿各发送一次数据,这样在一个时钟周期内可完成双倍速率的数据传输 由于DDR的控制逻辑比较复杂,这里只对其"写模式"下的工作原理进行介绍,如图1所示

由于DDR的控制逻辑比较复杂,这里只对其"写模式"下的工作原理进行介绍,如图1所示

|

其中根据DDR的时序要求在写模式下,写命令和随路时钟的第1个上升沿要有一个固定的时间间隔tDQSS

其中根据DDR的时序要求在写模式下,写命令和随路时钟的第1个上升沿要有一个固定的时间间隔tDQSS 为了在对DDR进行读写时能够正确地存储和读取数据,应该严格地按照厂家提供的芯片手册上的时序要求进行逻辑控制设计

为了在对DDR进行读写时能够正确地存储和读取数据,应该严格地按照厂家提供的芯片手册上的时序要求进行逻辑控制设计 下面对DDR的逻辑控制的设计和实现流程进行简单的介绍

下面对DDR的逻辑控制的设计和实现流程进行简单的介绍

3 DDR控制模块的设计

根据DDR芯片控制要求,在设计中将DDR主控制模块分为5个子模块,分别是初始化模块、外部刷新模块、主状态机模块、地址模块和命令输出模块 其具体组成如图2所示

其具体组成如图2所示

|

初始化模块在系统启动之后马上对DDR进行配置,使其达到正确的时序和配置要求

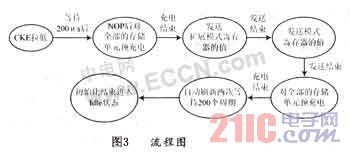

初始化模块在系统启动之后马上对DDR进行配置,使其达到正确的时序和配置要求 DDR初始化的流程图如图3所示

DDR初始化的流程图如图3所示

|

机的动作,通过翻译控制信号控制内部状态机产生控制DDR的正确时序信号,这一部分是主控制模块的关键和难点,能否正确控制DDR的操作完全集中在此模块

(2)外部刷新模块是辅助主状态机模块控制DDR处于空闲状态时的定时刷新

(3)地址发生模块的作用是根据所接收由主控状态机发送来的内部命令产生所对应的地址,然后将命令和对应的地址同步发送给命令发送模块

(4)命令发生模块是与DDR芯片的接口部分,其将从地址模块发送来的具体命令解释成DDR所需的命令信号和控制信号![]()

以及所需的地址信号

以及所需的地址信号![]() (AO~A12,BA0,BAl)

(AO~A12,BA0,BAl)

4 高速数据采集系统的结构设计

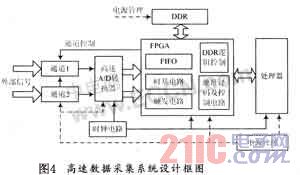

为了能更清楚地了解DDR在高速数据采集系统中的应用,这里将对基于CPCI总线的高速数据采集系统结构进行描述 高速数据采集系统的设计框图如图3所示

高速数据采集系统的设计框图如图3所示

|

外部信号首先经过模拟通道的调理达到A/D芯片的输入要求,再通过A/D芯片将模拟信号转换成数字信号送人FPGA处理 当处理器发出"写命令"时,把数字信号在FIFO内部进行缓存再送入DDR进行存储.如果A/D的采样速率为200 MSa/s,则可以使用133 MHz时钟速率的DDR芯片即可达到要求

当处理器发出"写命令"时,把数字信号在FIFO内部进行缓存再送入DDR进行存储.如果A/D的采样速率为200 MSa/s,则可以使用133 MHz时钟速率的DDR芯片即可达到要求 但是在内部进行缓存时存在一个问题,就是写入F1F()的时钟速率大于读取FIFO的时钟速率,这样就会导致从A/D采样过来的信号不能完整地存储

但是在内部进行缓存时存在一个问题,就是写入F1F()的时钟速率大于读取FIFO的时钟速率,这样就会导致从A/D采样过来的信号不能完整地存储

在这种情况下通常采用数据分流的方式进行解决,即把采人FPGA的200 MHz的数据流分成2路100 M的数据流,分别存入相应的FIFO内再以133 MHz的时钟速率读出送DDR进行存储,这样就可以对信号进行完整的存储 当然存储过程还要通过DDR的控制模块和FPGA内部自带的1P核的配合才能够完成

当然存储过程还要通过DDR的控制模块和FPGA内部自带的1P核的配合才能够完成 同理,当处理器发出"渎命令"时,在DDR控制模块的控制下将DDR内部数据读回FPGA内部,再次通过FIFO进行缓存

同理,当处理器发出"渎命令"时,在DDR控制模块的控制下将DDR内部数据读回FPGA内部,再次通过FIFO进行缓存 通常采用40 M的时钟速率将数据送回处理器处理,从DDR写回FPGA的数据流时钟速率为133 M,而从FIFO读}IJ数据的时钟速率为40 M;同样存在着写入FIFO的时钟速率大于读取的时钟速率的现象,但足这里不仔在数据丢火的问题,冈为前端的分流处理已经保证了数据的完整性

通常采用40 M的时钟速率将数据送回处理器处理,从DDR写回FPGA的数据流时钟速率为133 M,而从FIFO读}IJ数据的时钟速率为40 M;同样存在着写入FIFO的时钟速率大于读取的时钟速率的现象,但足这里不仔在数据丢火的问题,冈为前端的分流处理已经保证了数据的完整性 这里只需对FIFO及DDR进行控制,即对FIFO的使用率做一个控制,当FIFO的使用率大于某一值时,停止从DDR中读取数据;当小于这个值时,继续从DDR中读取数据

这里只需对FIFO及DDR进行控制,即对FIFO的使用率做一个控制,当FIFO的使用率大于某一值时,停止从DDR中读取数据;当小于这个值时,继续从DDR中读取数据 这样就有足够的数据可进行分析处理,从而重现信号特征

这样就有足够的数据可进行分析处理,从而重现信号特征

5 结 语

DDR在高速数据采集系统中的应用有很大的实际意义,他提高了系统的可靠性和数据的存储深度,在一定程度上有效地减小了电路设计的尺寸 DDR已经被应用于视频采集、内存设计等多个领域

DDR已经被应用于视频采集、内存设计等多个领域 其关键技术是DDR时序控制模块的设计

其关键技术是DDR时序控制模块的设计