- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PDMA在测试SDRAM控制器中的应用

录入:edatop.com 点击:

我们设计了一个PDMA(Programmable Direct Mem o ry Access)用于测试SDRAM控制器的性能。在SoC中,SDRAM控制器往往跟多个IP模块(图形处理单元,音频处理单元等)交换数据,采用多个PDMA通道同时访问Memory可以真实模拟SDRAM控制器在SoC环境中被多个IP随机访问的情形。

2 PDMA的结构及工作原理

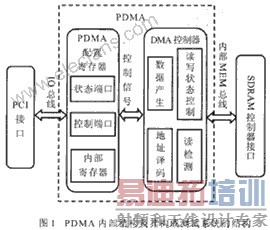

PDMA是可编程直接存储器存取的简称。图1 虚中框内是PDMA的内部模块结构,它主要由寄存器组和控制器两大部分构成,寄存器组用于保存配置参数和PDMA对SDRMA控制器访问后的状态信息及接收、启动、停止等控制信息。图2是 PDMA寄存器组的内部结构。

寄存器组模块里包含了一个同步模块、控制寄存器、状态寄存器和各通道的寄存器组。每一个子通道的寄存器组又包含访问基址寄存器、访问模式寄存器、周期计数器等三个寄存器。各寄存器的功能描述如表1所示。

PDMA的控制器主要由:产生写数据的状态机、地址译码模块、FIFO以及读数据校验模块四部分构成。各模块的功能由表2描述。

PDMA控制器的结构如图3所示,其核心逻辑是一个状态机,我们采用一个两层嵌套的状态机来实现控制功能,如图4所示。

3 测试系统的结构和工作原理

在本设计中,PDMA用于仿真多个IP核对SDRAM控制器进行读写访问以验证SDRAM控制器的设计是否高效合理,性能是否稳定等指标。

PDMA整个测试系统由PCI接口模块、PDMA 以及SDRAM控制器三大部分构成(见图1)。PCI接口模块与PDMA之间以内部IO总线相连接。 PDMA与SDRAM控制器之间以内部Memory总线连接。PCI接口模块连接外部PCI总线与内部的 PDMA,转换由外部发起的PCI IO访问对PDMA进行参数配置以及对命令、状态等寄存器进行读写。PDMA在得到了配置参数及启动访问的命令信息后启动对SDRAM控制器的访问(写然后读),并把测试的结果反映到PDMA的状态寄存里。

测试用PDMA的具体工作过程如下:

(1)PCI接口模块对PDMA各通道进行参数配置(如访问长度、访问基址、访问方式等);

(2)PCI接口模块写PDMA的控制寄存器,启动对SDRAM的读写;

(3)PCI接口模块读PDMA的状态寄存器,探测访问是否完成,如完成,则读取完成后的状态信息(如错误位,发生错误的地址)。

4 RTL仿真

完成RTL级的设计后,我们利用Cadence公司的仿真工具VerilogXL对设计进行了功能仿真。仿真的环境是基于PCI的,所以其仿真顺序如下:

(1)配置PCI配置空间的IO Base 及 Mem o ry Base寄存器;

(2)写PCI配置空间54H,58H等寄存器,配置SDRAM 控制器及SDRAM芯片的参数;

(3)写PCI配置空间的命令寄存器(offset==04h),使能该设备;

(4)访问PCI IO空间中的PDMA配置寄存器,设定各个PDMA通道的配置参数;

(5)写入相应的命令,启动PDMA访问内新路子SDRAM控制器;

(6)检测PDMA的状态寄存器,根据设定的条件(正常结束或者发生错误)退出仿真程序;

(7)打开波形文件,检查是否有错误发生。

图5是由PCI发起的一次写IO寄存器访问的仿真波形,PDMA的配置数据就是通过若干这样的操作完成的。

相对而言,我们更关注PDMA是如何访问Memory的。图6是由一个PDMA发起的写读模式下的访问时序。GROUP1的信号是由PDMA发起的内部Memory总线信号组,而GROUP2的信号是 Memory控制器和内存芯片间的符合jedec标准的总线协议。从图中我们可以清楚地看到总线协议的转换过程,及时发现是否有违反协议的情况发生。

5 上板测试的方法和过程

在完成功能仿真后,使用Synopsys综合工具 FPGA compiler对设计进行综合,并选用XILINX公司的VERTEX1600E系列为目标器件,生成相应的网表文件,下载到FPGA上进行测试。综合的结果如表3所示。测试平台是一台PC机,带有PCI标准接口的测试卡和PCI读写软件。上板测试过程如下:

(1)下载bit文件到FPGA中;

(2)配置SDRAM控制器;

(3)置PDMA寄存器;

(4)启动PDMA访问;

(5)读回PDMA的状态位。

测试时需要输入相应的测试向量,一个好的软件界面可以大大减轻硬件工程师编写、输入测试向量的工作量。表4是一个测试向量的内容和结果,像这样的测试要进行多次以提高故障覆盖率并统瞥鯥P的性能。

6 实验结论

经过不断调试和改进,PDMA能够按照功能寄存器的配置准确发起Memory访问,并能够及时报告SDRAM控制器的操作错误。该测试平台不仅适用于验证SDRAM控制器的设计,而且在经过很小的改动后可以配置成支持对性能更好的DDR存储控制器的测试验证。灵活的配置方式使之成为一个通用的测试平台,对不同的Memory控制器的测试只需用软件对相应的配置寄存器进行配置即可,硬件基本不用进行改动,大大节约了设计时间,提高了设计的成功率和效益。

2 PDMA的结构及工作原理

PDMA是可编程直接存储器存取的简称。图1 虚中框内是PDMA的内部模块结构,它主要由寄存器组和控制器两大部分构成,寄存器组用于保存配置参数和PDMA对SDRMA控制器访问后的状态信息及接收、启动、停止等控制信息。图2是 PDMA寄存器组的内部结构。

|

|

寄存器组模块里包含了一个同步模块、控制寄存器、状态寄存器和各通道的寄存器组。每一个子通道的寄存器组又包含访问基址寄存器、访问模式寄存器、周期计数器等三个寄存器。各寄存器的功能描述如表1所示。

|

PDMA的控制器主要由:产生写数据的状态机、地址译码模块、FIFO以及读数据校验模块四部分构成。各模块的功能由表2描述。

|

PDMA控制器的结构如图3所示,其核心逻辑是一个状态机,我们采用一个两层嵌套的状态机来实现控制功能,如图4所示。

|

|

3 测试系统的结构和工作原理

在本设计中,PDMA用于仿真多个IP核对SDRAM控制器进行读写访问以验证SDRAM控制器的设计是否高效合理,性能是否稳定等指标。

PDMA整个测试系统由PCI接口模块、PDMA 以及SDRAM控制器三大部分构成(见图1)。PCI接口模块与PDMA之间以内部IO总线相连接。 PDMA与SDRAM控制器之间以内部Memory总线连接。PCI接口模块连接外部PCI总线与内部的 PDMA,转换由外部发起的PCI IO访问对PDMA进行参数配置以及对命令、状态等寄存器进行读写。PDMA在得到了配置参数及启动访问的命令信息后启动对SDRAM控制器的访问(写然后读),并把测试的结果反映到PDMA的状态寄存里。

测试用PDMA的具体工作过程如下:

(1)PCI接口模块对PDMA各通道进行参数配置(如访问长度、访问基址、访问方式等);

(2)PCI接口模块写PDMA的控制寄存器,启动对SDRAM的读写;

(3)PCI接口模块读PDMA的状态寄存器,探测访问是否完成,如完成,则读取完成后的状态信息(如错误位,发生错误的地址)。

4 RTL仿真

完成RTL级的设计后,我们利用Cadence公司的仿真工具VerilogXL对设计进行了功能仿真。仿真的环境是基于PCI的,所以其仿真顺序如下:

(1)配置PCI配置空间的IO Base 及 Mem o ry Base寄存器;

(2)写PCI配置空间54H,58H等寄存器,配置SDRAM 控制器及SDRAM芯片的参数;

(3)写PCI配置空间的命令寄存器(offset==04h),使能该设备;

(4)访问PCI IO空间中的PDMA配置寄存器,设定各个PDMA通道的配置参数;

(5)写入相应的命令,启动PDMA访问内新路子SDRAM控制器;

(6)检测PDMA的状态寄存器,根据设定的条件(正常结束或者发生错误)退出仿真程序;

(7)打开波形文件,检查是否有错误发生。

图5是由PCI发起的一次写IO寄存器访问的仿真波形,PDMA的配置数据就是通过若干这样的操作完成的。

|

相对而言,我们更关注PDMA是如何访问Memory的。图6是由一个PDMA发起的写读模式下的访问时序。GROUP1的信号是由PDMA发起的内部Memory总线信号组,而GROUP2的信号是 Memory控制器和内存芯片间的符合jedec标准的总线协议。从图中我们可以清楚地看到总线协议的转换过程,及时发现是否有违反协议的情况发生。

|

5 上板测试的方法和过程

在完成功能仿真后,使用Synopsys综合工具 FPGA compiler对设计进行综合,并选用XILINX公司的VERTEX1600E系列为目标器件,生成相应的网表文件,下载到FPGA上进行测试。综合的结果如表3所示。测试平台是一台PC机,带有PCI标准接口的测试卡和PCI读写软件。上板测试过程如下:

|

(1)下载bit文件到FPGA中;

(2)配置SDRAM控制器;

(3)置PDMA寄存器;

(4)启动PDMA访问;

(5)读回PDMA的状态位。

测试时需要输入相应的测试向量,一个好的软件界面可以大大减轻硬件工程师编写、输入测试向量的工作量。表4是一个测试向量的内容和结果,像这样的测试要进行多次以提高故障覆盖率并统瞥鯥P的性能。

|

6 实验结论

经过不断调试和改进,PDMA能够按照功能寄存器的配置准确发起Memory访问,并能够及时报告SDRAM控制器的操作错误。该测试平台不仅适用于验证SDRAM控制器的设计,而且在经过很小的改动后可以配置成支持对性能更好的DDR存储控制器的测试验证。灵活的配置方式使之成为一个通用的测试平台,对不同的Memory控制器的测试只需用软件对相应的配置寄存器进行配置即可,硬件基本不用进行改动,大大节约了设计时间,提高了设计的成功率和效益。

上一篇:镜头焦距的计算公式

下一篇:便携式电子血压计连续动态监测的设计