- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA平均值原理相位差计的设计

摘 要:相位差的测量在研究网络特性中具有重要作用。设计一个测量快速、精确的相位差计已成为生产科研中重要课题,提出了基于平均值原理相位差计的设计方法,采用FPGA芯片实现了平均值相位差计,重点对相位差测量中的超前与滞后判断、输入信号处理、相位差计数器、锁存显示等几个数字环节进行VHDL语言编程,顶层用原理图方式构建了相位差测量系统。该系统电路结构简单,占用逻辑资源少,抗干扰能力强,可靠性高。

关键词:电子测量;相位差;平均值原理;EDA技术

相位差的测量在研究网络特性中具有重要作用,如何快速、精确地测量相位差已成为生产科研中的重要课题。测量相位差的方法很多,有集成电路设计的,也有采用数字信号处理(DSP)实现的,现在普遍采用电子计数式的方法。但传统的瞬时相位差计,需要用锁相环电路锁相跟踪被测信号,廉价的低端FPGA芯片无法完成,同时被测信号的频率范围也限制在低频内,为了解决上述问题,提出平均值相位差计的原理,并采用VHDL语言编程,FPGA芯片实现,巧妙地简化了锁相跟踪电路,扩展了被测信号的频率范围,提高相位差计的性能参数,也大大降低了成本,具有很高的性价比。

1 总体设计方案与基本原理

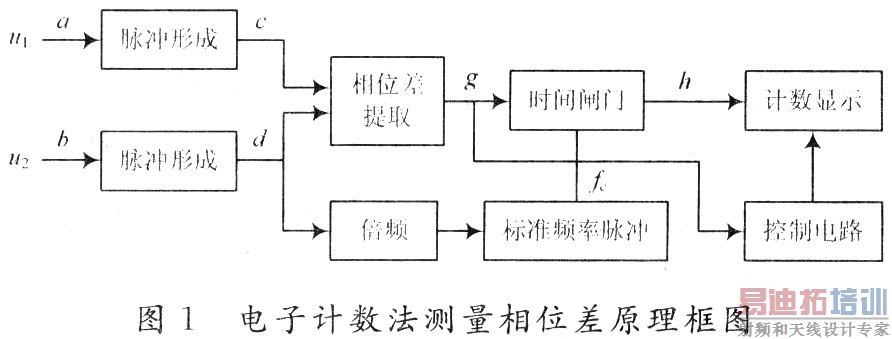

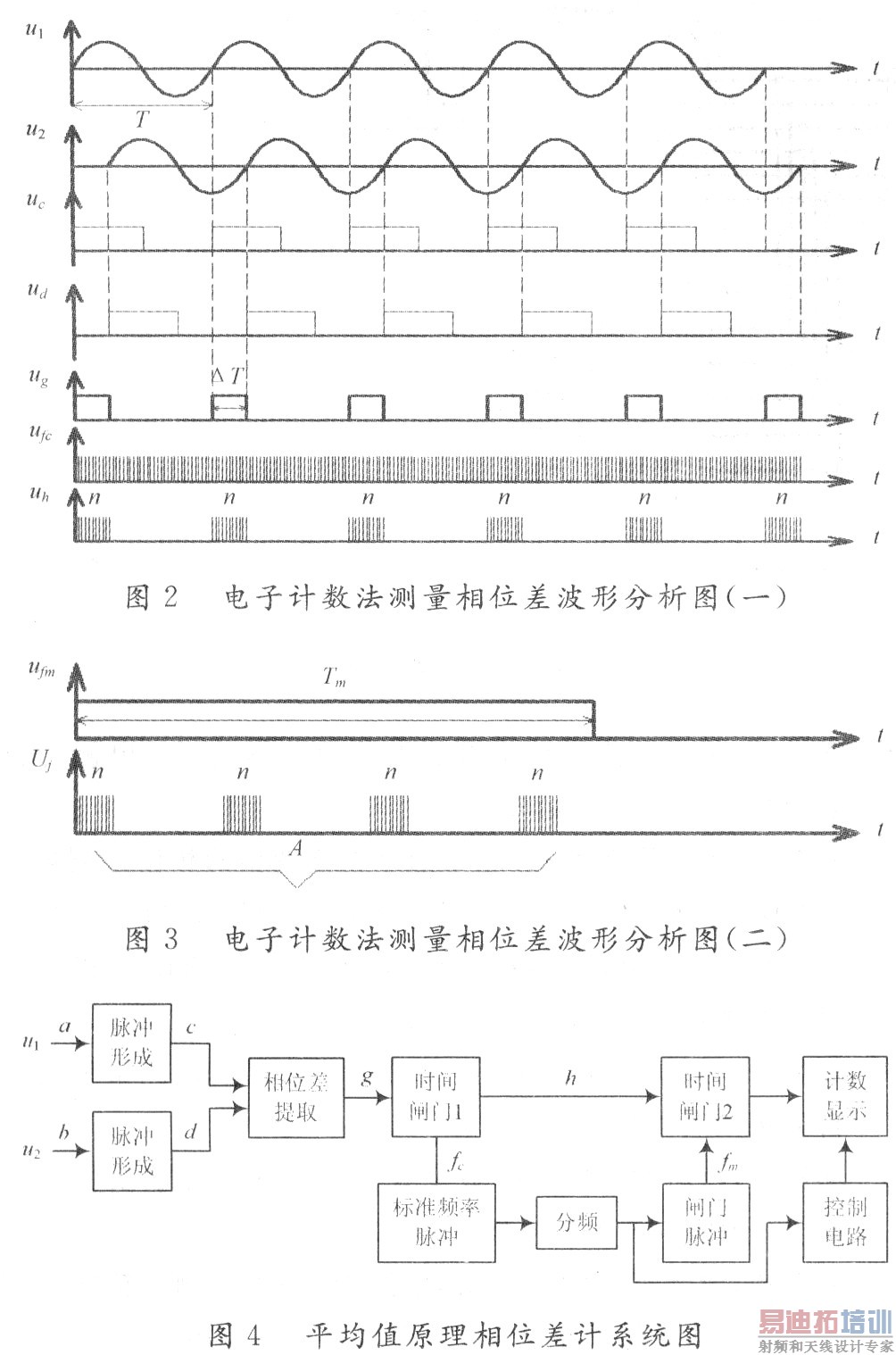

数字式相位计的基本原理如图1所示,两路同频率的信号U1,U2通过脉冲形成电路,产生两路过零脉冲信号U1,U2,再经过相位差提取电路得到宽度等于两信号相位差对应时间宽度的信号Ug,最后通过闸门、计数、显示就可以测量到相位差的数值。各点的波形分析如图2中的U1,U2,U3,Ud,Ug,Ufc及Uf。其中:U1,U2是同频率不同相位的两个信号;△T表示两个同频率正弦波过零点的时间差;Ufc为经过倍频的计数标准脉冲。设被测信号的频率为f,信号的周期为T,若倍频数为360×10k,则fc=360×10kf,假设在1个信号周期内能计到的Ufc脉冲数为N,在相位差所对应的时间△T内计到的Uk脉冲数为n,那么N=fcT=360×10kfT=360×10k,所以相位差ψ=360△T/T=360n/N=10-bn,即计数值n的数字就代表两信号中相位差的度数;6表示小数点的位置。

这种测量原理,必须保持fc与f的严格比例关系,因此必须用到锁相倍频电路,若用FPGA实现,就必须选用含锁相环的高端芯片,成本提高;同时,由于.fc=360×lOkf,若f=1 MHz,测量精度为±1°,则fc=3 600 MHz,系统的频率就相当高,目前的FPGA芯片几乎无法实现。

为了解决这两个问题,利用平均值相位差计的原理,对上述测量方法进行改进,原理如图4所示。各点的波形分析如图2和图3所示。可以看出,就是增加了一个时间闸门2,波形分析也就是多了2个Ufm和Uj。

闸门脉冲发生器由晶振分频器、闸门电路组成,它送出的波形如图3所示。Ufm波形所示宽度为Tm的门控信号Ufm;Tm远远大于被测信号的周期Tmax,一般取Tm=kT;k是为比例系数。

这一闸门信号使时间闸门2开启,在Tm内通过时间闸门1的标准频率脉冲有通过时间闸门2.得到的波形如图3所示。

设在时间Tm内计到的脉冲总数为A,对图3中的Ufm及Uj点波形分析可知,A=kn;考虑到k=Tm/T;n=fc△T;φ=360△T/t,所以A=(Tmfc/360)φ=aφ。式中:a=Tmfc/360,若选取适当分频数m=fc/fm=Tmfc的值,使a=10g,φ=A×10-g,则计数值A的数值就是被测信号相位差的度数;g表示小数点的位置。从上述原理分析可以看出,标准信号不必再跟踪被测信号,FPGA芯片就可以选用低端的,大大降低成本,同时被测信号的频率也可以提高到系统频率同一数量级,从而大大扩大了被测信号的频率范围。

2 误差分析

相位差的测量误差主要有标准频率误差和量化误差。标准频率由晶振产生,误差很小,在此主要讨论量化误差。因为φ=A×10-g,所以△φ=△A×10-g,A=kn。误差合成理论有△A=△kn+k△n=(±1×n)+k(±1)=±(k+n)=±(△Tfc+f/fm),△A=±[(φ/360)(fc/f)+(mf/fc)]。当被测信号的频率f很高,接近系统频率fc时,k很大,n很小,△A△±k=±mf/fc;当被测信号的频率f很低,接近脉冲闸门信号频率fm时,k很小,n很大,△A△±n=±(φ/360)(fc/f)。例如:信号频率若为f=10×103Hz,则系统频率为fc=10×105Hz,相位差为φ=90°,分频数m=360×103,带入误差公式计算得极限误差△A=610°,△φ=610。×10-3=O.61°。

3 硬件编程及FPGA实现

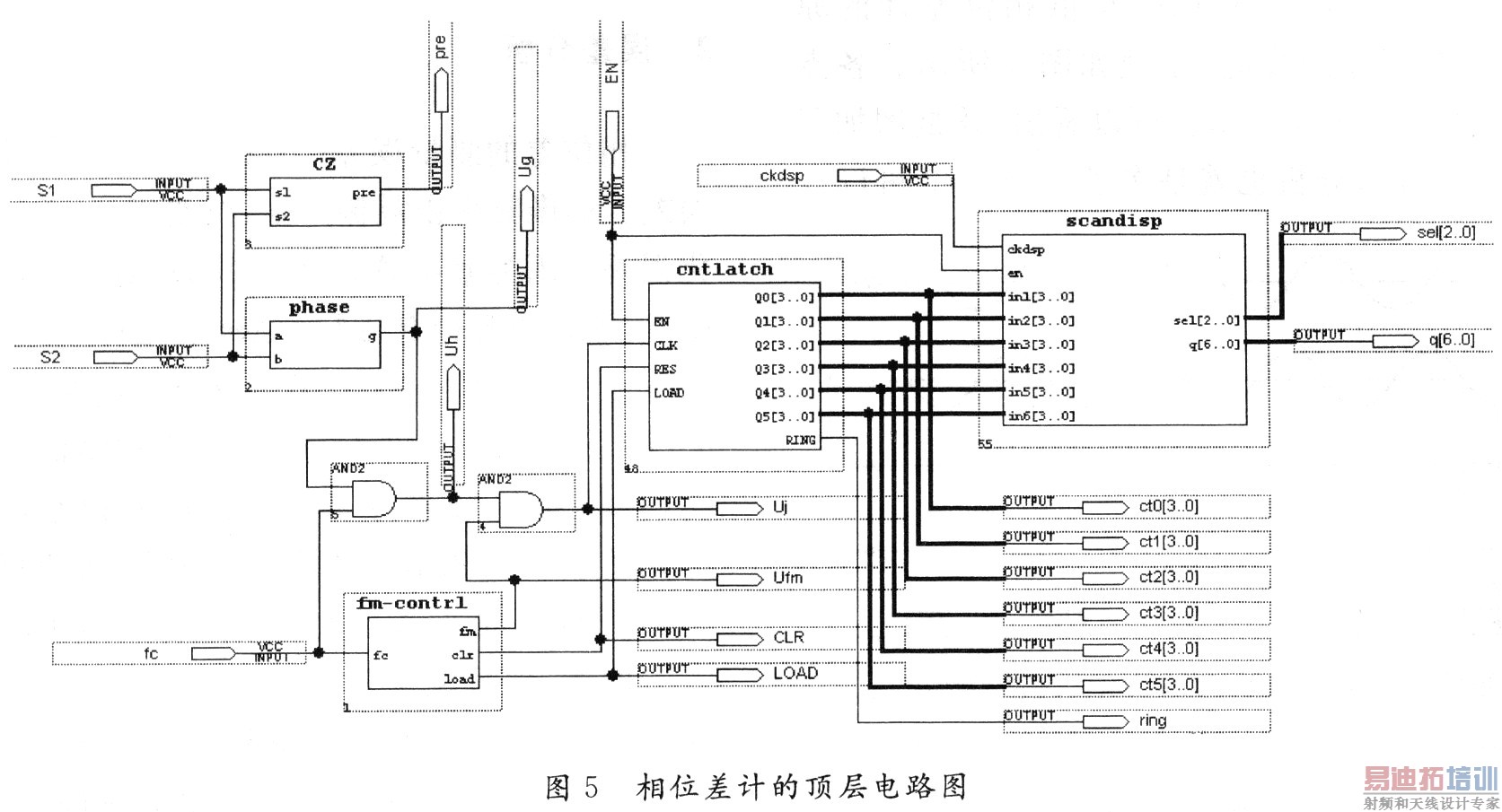

选用Atlera公司的ACEX系列的EPlK30QC208-3芯片,用VHDL进行编程,在QrutusⅡ6.O平台上设计的顶层电路图如图5所示。

顶层电路只画出了数字部分,脉冲形成等模拟环节都是标准电路,在此不讨论。数字电路部分主要包括相位超前滞后CZ模块、相位差信号提取phase模块、标准频率产生及控制电路fm-control模块、计数锁存cntlatch模块、动态扫描及译码显示scandisp模块等环节。其中输入端有2个同频率,具有相位差的信号输入端s1,s2、系统频率fc、使能信号EN、动态显示的扫描频率clkdisp。输出端口有七段显示数码q[6..O]、显示选择信号sel[2..O]、计数溢出响铃信号ring。为了方便观察分析,还设置了一些中间信号,如ct0[3..O]~ct5[3..0]是锁存住要显示的数字。

顶层系统电路的仿真设置如下:信号频率若为f=10×103Hz,系统频率为fc=10×106Hz,相位差为φ=90°,分频数m=360×103。,仿真结果如图6所示。

在图6中可以看出S1,S2是两个有相位差90°的矩形信号。

测量线所在的位置就是fm的下降沿,计数结束,开始锁存相位差数字ct0[3..0]~ct5[3..0],锁存信号结束,清零信号到来,清零信号结束,下个周期从新循环开始。

pre输出为高电平1,表明信号s1超前信号s2,锁存的相位差数字是90.360°,与设置的相位差完全吻合,误差也小于极限误差。仿真表明,设计是正确完善的,能够达到测量要求。

4 结 语

通过对平均值相位差计原理的分析和程序设计、仿真,用FPGA芯片实现了一个高精度、宽频率范围的相位差计。该测量方法的最大优点是系统电路简单,不需要锁相环,占用的逻辑资源少,选用低端FPGA芯片完全能满足要求,大大提高了被测信号的频率范围及测量精度,具有一定的应用价值。

上一篇:基于OBDⅡ汽车远程监测系统的研究

下一篇:双端可调的塞贝克系数测量仪