- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

多并行处理器接收机设计与实现

摘要:为满足对卫星信号处理越来越快的速.度及通用性的要求,设计并实现了一款高性能的卫星接收机。该接收机的设计在原理上采用多并行处理器的思想,因卫星接收机的中频处理数据量大,实时性高。这样,对芯片的选型提出了很高的要求,通过比较选择了两片目前业界处理能力强的DSP芯片TMS320C6416T核心计算单元,并结合使用了两片功耗低,成本低和大容量的FPGA芯片EP3C120完成卫星接收机中的数据处理,从而使接收机的处理速度和处理能力大大提高,满足了处理高实时性和大数据量卫星信号的要求。

关键词:DSP;FPGA;多并行处理器;卫星接收机

0 引 言

在航空、航天领域,扩频接收机对信号处理速度的要求不断提高。同时,鉴于当前单一处理器导航接收机结构给导航算法带来的约束及并行多处理器技术的日益成熟,为了避免专用卫星接收机的重复研制工作,降低研制的难度、成本和周期,提高可靠性,近几年这一领域中提出了多并行处理器通用接收机硬件平台的思想。基于这一思想,本文的接收机设计在文献[1]的基础上做了一些改进,采用了两片DSP芯片TMS3206416T(以下简称C6416)和两片FPGA芯片EP3C120的设计方案。这样,完成各种不同的信号处理任务可以采用完全统一的硬件平台,所不同的只是该硬件平台上运行的软件。这就增加了系统的灵活性和硬件平台的通用性,并解决了不同信号处理任务分配的问题。

1 接收机板的总体描述

接收机板的原理图框图如图1所示,板上资源及性能指标如表1所示。

板上有两片C6416T,它们在结构上完全对称,描述上称两片C6416T及其外围资源为C6416T模块。C6416T模块中对称的结构决定了两片C6416T既可以是串行流水方式的并行计算,也可以是并发操作方式的并行计算,具体的方式由接收机板完成的算法来决定。两片C6416T通过双端口存储器(DPRAM)以共享存储器的方式耦合在一起,来完成处理时两者之间的数据共享和通讯。双口存储器数据总线宽度为64 b,容量为9 Mb。另外,两片C6416T之间还可以通过多功能串口(McBSP)进行数据传输,而且每片C6416T外围配备有1 024 Mb的SDRAM和64 Mb的FLASH。其中,大容量的SDRAM可用来暂存大量的中间处理数据;大容量的FLASH可用来存储大量的程序和非易失性数据。这里设计的存储器最大存储容量比较大,主要是基于通用性的考虑,配备不同容量时可以满足不同的应用需求,这可根据实际的情况而定。除此之外,板上还有两片3C120及其外围资源,描述上将其称为3C120模块。3C120模块中两片3C120之间也通过9 Mb的DPRAM来完成两者之间的数据共享和通信,而且两片3C120之间还通过自定义I/O扩展总线接口来进行数据通信与传输。另外,每片3C120与各自平行对应的C6416T之间通过EMIFA总线和SPI进行数据传输,与所对应的两路10 b ADC相连,以完成对接收中频数据的采样。

2 模块的设计

接收机板中,C6416T和3C120是核心器件,其他器件都是外设,以下的描述将围绕C6416T和3C120两个模块展开。

C6416T模块中主要的外设都与EMIF相连接,所以外设接口的设计主要介绍EMIF的设计。C6416T有两个EMIF接口,EMIFA的外总线上连接了FPGA,SDRAM和DPRAM,它们的数据宽度都是64 b。出于信号完整性考虑,外总线通过匹配电阻来解决信号反射的问题。FPGA用同步时序访问,SDRAM和DPRAM都是同步器件,它们被直接连接到临近EMIFA口这一级总线上,这一级总线的访问速率高,称为高速总线。EMIFA的每个CE空间最大的存储管理能力是256 Mb,外接4片32 b数据宽度、512 Mb的SDRAM时,可以达到这个最大容量,本设计电路中每个C6416T用了两片32 b数据宽度、512 Mb的SDRAM,占用一个CE空间,共1 024 Mb。另外,所选DPRAM芯片数据宽度为72 b,为了能与EMIFA总线匹配,在电路设计中将DPRAM的数据线每取8 b就间隔1 b,这样就得到64 b的数据宽度。

EMIFB的外总线上连接了FLASH,它的数据宽度为16 b,存储容量为64 Mb。因为EMIFB对8 b的异步存储设备的管理能力只有1 Mb,所以接8 Mb的FLAsH需要做地址扩展,这个扩展功能在CPLD中完成。在该接收机板中EMIFB的BCE1空间所对应的16 Mb FLASH用来做8 b Bootloader,剩余的48 MbFLASH用来存储重要数据。每个C6416T的EMI-FA和EMIFB的存储空间分配如图2和图3所示。

对于3C120模块而言,它除了通过EMIFA接口和C6416T相通信外,还通过SPI来和C6416T相互传输数据,这样有利于数据的处理。同时,两片3C120为了能相互共享数据和存储数据,它们之间连接了一个9 Mb的DPRAM。

3 模块的通讯链路设计

接收机板中主要包括了三大通讯链路,主要介绍如下:

(1)C6416T模块中两片DSP(C6416TA和C6416TB)之间的通讯它们有两种通讯方式:DPRAM通讯、串口通讯。

两个C6416T分别与DPRAM的左、右口相连。C6416TA将要处理的数据从左口链路送入DPRAM,再通过DPRAM的右口中断管脚通知C6416TB,然后C6416TB从DPRAM的右口取走数据。C6416TB也可以用同样的方式给C6416TA传送数据。中断产生是通过写和读DPRAM的左右口邮箱来实现的,如图4所示。C6416TA写左口邮箱时,会在右口产生中断给C6416TB,然后C6416TB读左口邮箱可清除中断。左口中断的产生和清除方法也是一样。

两个C6416T通过串口1和串口2相互连接,可实现全双工通讯,同步串口的最高时钟速率可达l/4CPU时钟频率。

(2)3C120模块中两片FPGA(3C120A和3C120B)之间的通讯

它们也有两种通讯方式:DPRAM通讯、自定义I/O通讯。两片3C120通过DPRAM通讯的原理与两片C6416T相同。另外,两片3C120之间还互连了一些I/O口,在实际应用当中可以对这些I/O口进行定义,让其来完成两片3C120间的数据交换。

(3)3C120模块与C6416T模块之间的通讯它们包括两部分,两片3C120分别与所对应平行的C6416T之间的通讯。每片3C120与所对应的C6416T之间可通过EMIFA总线、SPI和中断来进行数据的交换和控制。

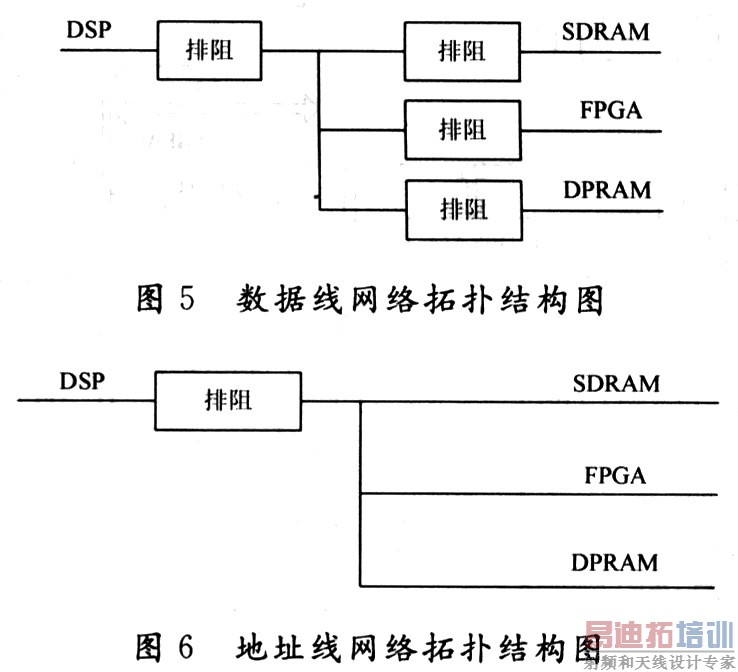

4 接收机板的SI仿真

信号完整性(Signal Integrity,SI)是指在信号线上的信号质量。在高速电路中来自接收端的反射信号很容易到达驱动端,如果反射信号很强,叠加的波形就有可能改变原来的逻辑状态,导致电路无法正常工作。该接收机板总线传输速率要求很高,所以在PCB布线之前,应预先进行调研,以形成规则或设计准则,从而确保设计结果不出现明显的信号完整性问题,这是SI仿真的前仿真。前仿真的过程是,首先将主要器件的IBIS仿真模型加到待布线的PCB中,定义输入参数和可能的拓扑范围,然后用Cadence运行每个可能的仿真组合,分析信号完整性的仿真结果,最后找到可以接受的数值范围,将其范围解释为PCB布线的约束条件,再进行PCB约束驱动布线。一般来说,前仿真也很难保证实际布线之后不出现信号完整性问题。所以在约束驱动布线后再次进行SI仿真,来检查是否符合信号完整性的要求,这是SI仿真的后仿真。在对该接收机板布线之前对地址线和数据线的拓扑结构进行了分析并做了前仿真,其拓扑结构分别如图5,图6所示。

从图5,图6中可以看出,地址线的网络拓扑结构在DSP的外设端未加匹配电阻,这样做的目的是为了减少PCB布线的繁琐性,但为了减少接收端反射信号对DSP端驱动信号的影响,这样做的前提首先应当保证符合信号完整性的要求。该设计中由于元器件布局的原因,DSP的地址线到其每个外设的距离相差不大,这样只需要在靠近DSP端加上匹配电阻就能符合SI的要求。当然,在DSP及其外设每端都加上匹配电阻的话,信号质量会更好,DSP数据线就采取了这种做法,由于它的数据线与其每个外设的距离不同,要保证信号完整性就不得不在靠近各器件这端的中部都加上匹配电阻。

为了检验实际布线后信号的完整性,在布线完成之后对数据线和地址线分别做了后仿真,这里只取数据线AED50和地址线AEA3的后仿真波形图,如图7,图8所示。

图7,图8中,U6为DSP,它作为驱动源,输出100 MHz的矩形波信号驱动它的外设;U7,U8为SDRAM,U10为DPRAM,U13为FPGA,它们作为DSP的外设,接收DSP发送来的信号。从这两幅图中可以看出,反射信号对数据线和地址线都有一定的影响,但都满足信号完整性的要求,同时也验证了在两种不同拓扑结构下所产生的信号质量不同。

5 测试结果

该接收机板已经设计实现。为了检测电路板的功能和性能,针对DSP和FPGA编制了所需的驱动程序,并通过各种测试程序对电路板做了大量的、长时间的各种测试。经过测试,可以确定电路板的功能已经按照设计的初衷实现,也符合接收机板要求的技术指标。另外,对电路板上各种资源访问性能的测试结果做了统计,如表2所示。

6 结 语

该接收机板的运算能力强,通用性强,存储容量大,可以通用于各种视频图像处理、雷达信号处理和卫星信号处理等领域,目前已应用在对处理速率和存储容量要求较高的卫星接收机技术方案中。

上一篇:数据采集系统中的DSP控制系统

下一篇:有机械耦合的电容式硅微陀螺敏感信号读取