- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

使JTAG边界扫描与功能测试相结合

录入:edatop.com 点击:

生产后的中度复杂的印刷电路板(PCB)传统上使用在线测试(ICT)和功能测试来进行检测。其它的测试方法,例如昂贵的光学和X光检查,经常是必须的,以来验证BGA被正确地放置。然而,JTAG边界扫描可以取代ICT,以作为功能测试的自然配对物,并且使光学与X光检查不再必要。

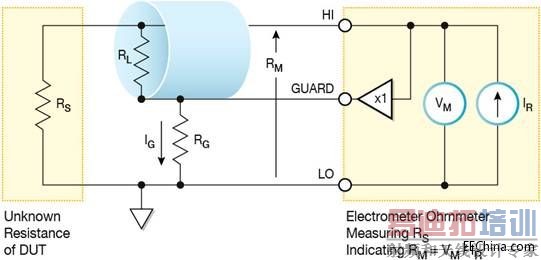

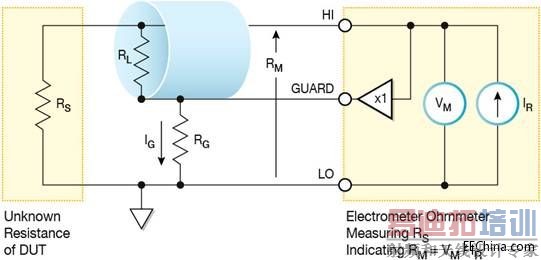

ICT是一个隔离测试每个部件或者连接的方法。其使用例如用于简单模拟部件的保护技术等技术。通过针床或者飞针对被测设备表面节点的访问,被用来验证与这些节点相连的已安装的部件的正确性。

图1.使用保护技术测量电阻

尽管这类测试验证了每个单一部件的正确性,它却不能够验证一个板卡,当通电时,是否能作为一个整体正常运行。想要做到这点就必须进行功能测试。

尽管新测试方法在繁衍,功能测试依然是认定电子系统和板卡正常运行的支柱。从概念上来讲,这类测试非常简单-它在于检测一个被测单元是否真正做到它所被设计的那样。一个针床装置也被融合进来以提供测试访问。这个测试方法的中心单独来讲是有些局限的,因为我们只能确认每个系统运行正常,而不是被隔离的单独部件

图2,一个典型的功能测试装置

功能测试的一个特征是它可能需要集成许多仪器到测试平台上。假设,例如,您需要测试一个被设计用来处理和无线通讯的板卡。为了执行功能测试,您需要使用其它与测试装置有关的仪器例如电源,数字和模拟I/O,RF分析仪器(频谱和矢量分析器,收发器,等等),与快速采集设备(示波器和数字转换器)来激发和读取单个信号。

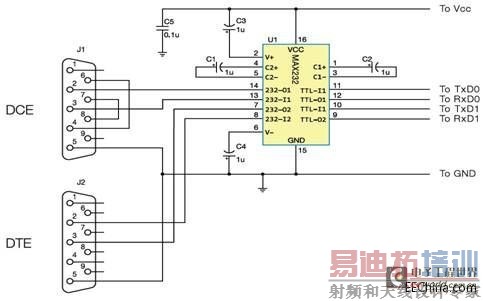

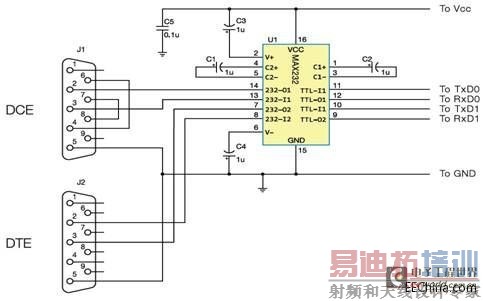

或许一个例子最能揭示ICT与功能测试的区别。考虑一个串联接口的MAX202驱动(见图3)。ICT可能与检查充电泵里电容的值有关,从而确认每个部件在隔离下运转正常,而功能测试则可能会检查发送和接收整个数据包。

图3.MAX232驱动典型的连接图

直到最近,ICT才允许在执行功能测试之前,容易地验证所有部件的正确安装。然而,近来可达到部件密度的增长意味着PCB设计会经常不允许布置足够数量的测试点。尤其是BGA部件的针脚在被焊接下后,完全不能被ICT访问。其结果是ICT性价比越来越差,越来越不可持续,并且增加产品交货期。这个问题最有革新的方案是边界扫描。

JTAG边界扫描

JTAG边界扫描是一个电子测试方法,被设计用来克服通常与复杂的、高密度板卡所相关的测试访问问题。边界扫描,按照IEEE 1149.x标准,提供了芯片中一个可以使综合数字测试协议在板卡层面就可适用的的电子线路。

这个线路把用在ICT中的物理探点用边界扫描单元来替代。它们存在于器件核心逻辑与外部针脚之间,可以在芯片上每个输入与输出处捕获或者驱入信号。

边界扫描单元可以在一个物理探头不能达到的地方提供虚拟探点,例如BGA下的焊点连接。一些细间距引线器件不能用物理探头可靠地检测,不过边界扫描再一次可以为这些针脚提供数字测试访问。

在器件的正常运作下,边界扫描单元如透明一般。它们可以捕获通过它们的数值,使可以观测数据流,而不改变通过它们的信号成为可能。当一序列正确的指令 被送到控制针脚(测试模式选择,TMS)上时,边界扫描单元还可以通过与它们相连的针脚驱动出数值,像一个物理探点或者探针一样激发电路。这允许工程师们, 用之前ICT测试同样的方式,来验证所有部件适当的互连(轨迹间短路的缺乏与连续性的验证),以及这些器件的正确行为。 [p]

ICT是一个隔离测试每个部件或者连接的方法。其使用例如用于简单模拟部件的保护技术等技术。通过针床或者飞针对被测设备表面节点的访问,被用来验证与这些节点相连的已安装的部件的正确性。

图1.使用保护技术测量电阻

尽管这类测试验证了每个单一部件的正确性,它却不能够验证一个板卡,当通电时,是否能作为一个整体正常运行。想要做到这点就必须进行功能测试。

尽管新测试方法在繁衍,功能测试依然是认定电子系统和板卡正常运行的支柱。从概念上来讲,这类测试非常简单-它在于检测一个被测单元是否真正做到它所被设计的那样。一个针床装置也被融合进来以提供测试访问。这个测试方法的中心单独来讲是有些局限的,因为我们只能确认每个系统运行正常,而不是被隔离的单独部件

图2,一个典型的功能测试装置

功能测试的一个特征是它可能需要集成许多仪器到测试平台上。假设,例如,您需要测试一个被设计用来处理和无线通讯的板卡。为了执行功能测试,您需要使用其它与测试装置有关的仪器例如电源,数字和模拟I/O,RF分析仪器(频谱和矢量分析器,收发器,等等),与快速采集设备(示波器和数字转换器)来激发和读取单个信号。

或许一个例子最能揭示ICT与功能测试的区别。考虑一个串联接口的MAX202驱动(见图3)。ICT可能与检查充电泵里电容的值有关,从而确认每个部件在隔离下运转正常,而功能测试则可能会检查发送和接收整个数据包。

图3.MAX232驱动典型的连接图

直到最近,ICT才允许在执行功能测试之前,容易地验证所有部件的正确安装。然而,近来可达到部件密度的增长意味着PCB设计会经常不允许布置足够数量的测试点。尤其是BGA部件的针脚在被焊接下后,完全不能被ICT访问。其结果是ICT性价比越来越差,越来越不可持续,并且增加产品交货期。这个问题最有革新的方案是边界扫描。

JTAG边界扫描

JTAG边界扫描是一个电子测试方法,被设计用来克服通常与复杂的、高密度板卡所相关的测试访问问题。边界扫描,按照IEEE 1149.x标准,提供了芯片中一个可以使综合数字测试协议在板卡层面就可适用的的电子线路。

这个线路把用在ICT中的物理探点用边界扫描单元来替代。它们存在于器件核心逻辑与外部针脚之间,可以在芯片上每个输入与输出处捕获或者驱入信号。

边界扫描单元可以在一个物理探头不能达到的地方提供虚拟探点,例如BGA下的焊点连接。一些细间距引线器件不能用物理探头可靠地检测,不过边界扫描再一次可以为这些针脚提供数字测试访问。

在器件的正常运作下,边界扫描单元如透明一般。它们可以捕获通过它们的数值,使可以观测数据流,而不改变通过它们的信号成为可能。当一序列正确的指令 被送到控制针脚(测试模式选择,TMS)上时,边界扫描单元还可以通过与它们相连的针脚驱动出数值,像一个物理探点或者探针一样激发电路。这允许工程师们, 用之前ICT测试同样的方式,来验证所有部件适当的互连(轨迹间短路的缺乏与连续性的验证),以及这些器件的正确行为。 [p]