- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

IIC总线测试总结

前一段时间在做板卡信号完整性测试。

信号完整性测试主要是对信号质量进行测试,观察信号电平是否满足门限,有无过冲、振荡、回沟,时序是否满足要求等。

由于在产品需求层面,是不会将信号质量作为一项需求提出,因此很多时候在归档的测试报告中只会存在功能测试报告,而是将信号完整性测试报告作为内部公开的一份参考资料,但这并不意味着我们可以减少对信号完整性测试的重视程度,因为信号完整性测试往往能够发现很多潜在的风险,比如自己在以前的测试中就遇到过低电平门限是0.8V,而测得的信号低电平也接近0.8V,虽然在功能上的验证是正常的,但这就是一项风险项,很有可能在量产上市后,随着长期运行或者环境改变,而导致故障,后来通过调整串阻阻值,降低了信号低电平,规避了风险;还有调整FPGA时序改善信号时序余量等很多由信号完整性测试发现解决的潜在风险项。

另外,信号完整性测试很多时候还能提前规避掉很多电磁干扰问题,减少后期整改的工作。比如过陡的边沿或过大的过冲,有时会是辐射发射的来源;

最后,通过信号完整性测试,将所有信号都控制在器件的要求范围内,这也提高了器件的工作可靠性,保障其工作寿命。

综上所述,不仅不能还应该更加重视对信号完整性的测试。

在有些公司,信号完整性测试又称之为单元测试,这是因为信号完整性测试需要覆盖板卡上的每一个元器件。

对于信号完整性测试的方案制定方法。个人的理解,应该关注每个器件的输入端口,主要又分为信号电平(一般需测试高电平电压、低电平电压、上冲和下冲)和信号时序(一般需测试建立时间和保持时间),具体根据器件手册制定,信号测试点也应该选择最靠近器件输入端口处的位置;而对于器件的输出端口,是不需要关注的,因为这是器件自身特性所决定的。

二、IIC总线操作过程说明

对于IIC总线,自己以前很少用到,只对某块板卡上一片预留的INTERSIL的IIC接口光传感器写过驱动进行功能调试。这次是第一次认真对IIC总线进行了信号完整性测试。

IIC总线由时钟线SCL和数据线SDA组成,设备连接到总线上的输出端为OD或OC输出,总线电平由外部上拉电阻决定。IIC总线速率分标准模式100Kbps,快速模式400Kbps和高速模式3.4Mbps。IIC总线上最多可以挂接400pf容性负载,挂接设备数量受此限制。IIC总线的运行由主机控制,被主机寻访的设备称为从机,每个接到IIC总线的设备都有一个唯一的地址,以便于主机寻访。

本次IIC信号完整性测试的其中一个器件为IIC接口的EEPROM,用作一个MCU的配置信息存储芯片,MCU每次上电后均会去读取配置,也可以执行对EEPROM的配置升级操作。对于EEPROM,读写过程都要测试。由于进度紧张,自己未经思考,首先在上电时,选择在MCU的IIC接口处测试EEPROM的读过程;然后再执行EEPROM配置升级命令,并在EEPROM的IIC接口处测试EEPROM的写过程。

但在测试过程中,却越来越感觉困惑,比如时序测试中有一项tSU:DAT参数,表示START信号的建立时间,但在测试写过程中,往往就很难捕捉到。随着测试的进行,困惑的地方越来越多,于是自己觉得该停一停,看看究竟测试方法有没有问题。

稍稍冷静下,读了下器件手册,很快便发现了问题所在,自己还停留在以前测试的惯性思维中,认为读就是数据读出,而写就是数据写入,没有对IIC总线操作过程作一思考。

对于IIC写过程,一般而言有如下几种情况:

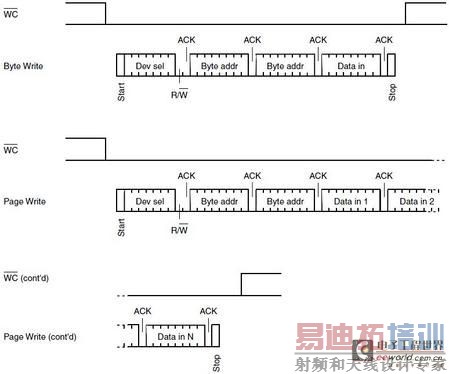

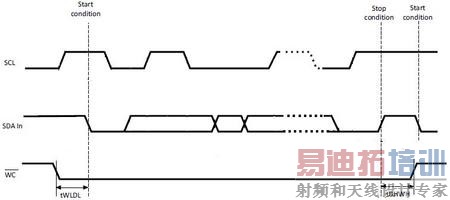

图1 IIC总线写操作过程

分为Byte Write和Page Write,Byte Write一次写入一个数据,Page Write一次可写入多个数据。在未进行写保护(WC为低时)才能进行写操作。

对于Byte Write,分为以下几个过程:

1、由主设备发出START信号;

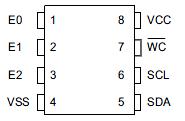

2、由主设备发出DEV SEL信号,DEV SEL为从设备的识别码,一般由7位组成,高四位为每类IIC设备特有,低三位通过从设备外部引脚配置得到,如图2所示的E2、E1、E0三个引脚;

图2 IIC设备引脚图

3、主设备在发出DEV SEL信号后,需继续发出一位“读/写控制位(R/W)”,以表示接下来执行的是何种操作。此时该位应置为低(写操作);

4、从设备进行ACK应答,为低电平;

5、主设备发出Byte addr信号,即要将数据写入到从设备的单元地址,图中所示为16位地址带宽,主设备每发出8位地址,从设备进行一次ACK应答;

6、主设备写入8位数据,从设备应答,之后主设备发出STOP信号,结束此次写操作。

对于Page Write,其过程与Byte Write基本一致,仅仅是其在写入多个数据后,才由主设备控制发出STOP信号,结束写操作。

对于IIC读过程,一般而言有如下几种情况:

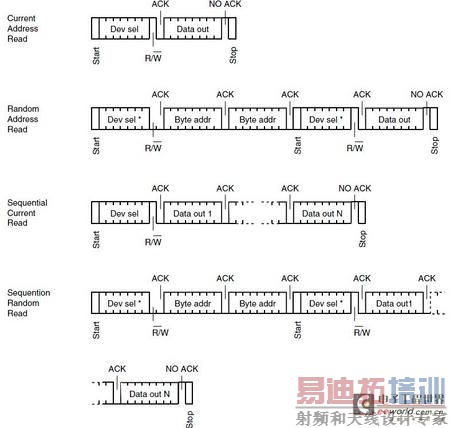

图3 IIC总线读操作过程

分为Current Address Read、Random Address Read、Sequential Current Read、Sequential Random Read。后两种读模式与前两种读模式的区别仅仅在于后两种是一次读出多个数据,因此不作累述。 [p]

对于Current Address Read,其操作过程为:

1、主设备发出START信号;

2、主设备发出DEV SEL信号,之后“R/W”位置1,表示接下来执行读操作;

3、从设备应答ACK;

4、从设备从当前指针所指单元发出数据;

5、主设备应答位,不应答从数据设备读入(NO ACK,高电平);

6、主设备发出STOP信号,结束此次读操作。

Sequential Current Read一次可读出多个数据,每8位数据读出后,主设备进行一次ACK应答,最后一个数据,主设备不进行应答,应答位置高,之后发出STOP信号结束操作。

对于Random Address Read,其操作过程为:

1、主设备发出START信号;

2、主设备发出DEV SEL信号,之后“R/W”位置0,表示接下来仍执行写操作;

3、从设备应答ACK;

4、主设备发出Byte addr信号,从设备对每8位Byte addr进行一次应答ACK;

5、主设备再次发出START信号;

6、主设备再次发出DEV SEL信号,之后“R/W”位置1,表示接下来执行读操作;

7、从设备应答ACK;

8、从设备从之前写入的Byte addr地址中读出数据;

9、主设备不进行应答,应答位置高(NO ACK);

10、主设备发出STOP信号,结束此次操作。

三、IIC总线测试项目

1、时钟SCL信号质量测试

包括高电平电压、低电平电压、上冲、下冲、上升时间、下降时间、时钟频率、高电平脉宽、低电平脉宽。

2、数据SDA信号质量测试

包括高电平电压、低电平电压、上冲、下冲、上升时间、下降时间。

3、写保护WC信号质量测试

包括高电平电压、低电平电压、上冲、下冲。

4、时序测试

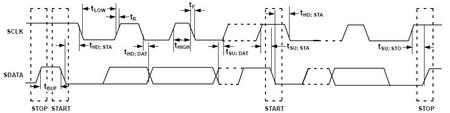

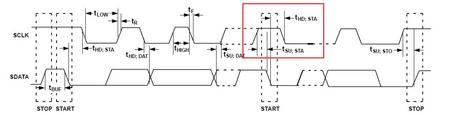

需要测试的时序如下图所示:

图4 IIC总线时序测试项目图

(1) tHD:STA:START信号保持时间。IIC总线是在SCL信号为高电平时,SDA下降沿作为START信号的。该参数是指SDA信号由高变低后,SCL还需要维持高电平的最短时间,以确保START信号成功采样;

(2) tHD:DAT:数据保持时间。IIC总线是在时钟SCL上升沿的时候对数据进行采样,SDA需在时钟上升沿来临前保持稳定;同时SDA需在时钟SCL为低电平时才能进行转换。该参数即是时钟SCL由高变低后,SDA还需要维持上一位数据电平的最短时间;

(3) tSU:DAT:数据建立时间。指在SCL上升沿来临之前,SDA此次采样数据电平需要提前维持的最短时间,以确保此次数据的采样成功;

(4) tSU:STA:START信号建立时间。指在SDA下降沿来临之前,SCL需要提前维持高电平的最短时间,以确保START信号的成功建立;

(5) tSU:STO:STOP信号建立时间。IIC总线是在SCL信号为高电平时,SDA上升沿作为STOP信号的。该参数是指在SDA上升沿来临之前,SCL需要提前维持高电平的最短时间,以确保STOP信号的成功建立;

(6) tBUF:总线释放最短时间。本次IIC操作结束和下次IIC操作开始需要对总线进行释放的最短时间;

(7) tWLDL(tSU:WC):WC信号建立时间。WC信号需要在START信号发出前便完成建立。该参数即在START信号SDA下降沿来临之前,WC信号需要提前维持低电平以确保成功建立的最短时间;

(8) tDHWH(tHD:WC):WC信号保持时间。WC信号需要在STOP信号发出后仍维持一段时间。该参数即在STOP信号SDA上升沿发出之后,WC信号仍需维持低电平以确保STOP操作成功完成的最短时间。

以上便是需要进行测试的项目。

四、IIC总线测试注意事项

自己之前在进行IIC总线测试时,由于急于完成,误认为读过程就是完全的数据读出。其实从IIC读操作过程就可以很明确的得知,读过程也包含着数据写入的阶段,比如START信号发出,DEV SEL信号发出和Byte addr信号的发出;

另一方面,由于START信号和STOP信号均是由主设备发出的,因此在测试IIC读操作时序的时候,仅需要测试tSU:DAT和tHD:DAT两项参数。而写操作才需要测试所有时序参数;

最后在测试过程中,尤其是在读操作过程中,由于前面先要执行设备识别、地址写入等写操作,之后才会出现数据的读出,如果要用示波器去抓整个读操作过程,然后再放大局部去读取时序参数,可能会由于时基过大,局部分辨率不够,导致读取的时序参数并不准确。

对于示波器,自己觉得比较重要的几个参数包括:带宽、采样速率和存储深度。

带宽主要针对的是示波器支持的输入波形频率范围;

采样速率主要是指示波器内部对波形的采样速率,根据香农采样定理,要想不失真地恢复模拟信号,采样频率应该不小于模拟信号频谱中最高频率的2倍。而实际上对于输入的波形,其最高频率取决于波形的边沿,可以用5~7倍信号频率来评估;

存储深度主要指示波器存储采样点的多少。之所以说在IIC读操作测试中,为了获取整个操作过程中的波形,将时基调大,然后再局部放大,受限于存储深度,局部的波形可能就会失真,读取出来的参数会有较大误差。

因此在读测试时,可以采用脉宽采样,由于我们的测试中,用到的是Random Address Read和Sequential Random Read两种模式,在读出数据前,主设备还要再发出一次DEV SEL信号,tSU:STA便是在此时测量,但此时的SCL信号脉宽也不同于之前,如下图红色框中的波形所示:

图5 tSU:STA测试时对应的SCL脉冲波形

可以先将时基调大,初步测出红色框中SCL脉宽长度,然后用脉宽采样,划定波形脉宽范围,然后采出波形,这样得到的读数据波形便有足够的采样点,读取的参数值也更有参考价值。

tSU:STA和tBUF也可按此方法采样测试。

通过这次测试,使自己更加明白,在做任何事情,不要急于着手,而是先想想看计划是怎样,采用什么样的方法,从总体上理清了头绪再着手,遇到细节问题再深究。

上一篇:最新DDR

信号分析方法

下一篇:添加vi或控件到

用户express中