- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

“虚拟”逻辑分析仪SignalTap II

Quartus II中集成的SignalTap II在一些高端应用中,尤其是逻辑资源(主要是余量)充足的应用中是非常不错的调试手段。而对于一些逻辑资源或者存储资源余量不多的应用中,这种调试方法则显得毫无意义。话说“鱼和熊掌不可兼得”,在Quartus II中所能够支持的在线调试手段中,例如In-system Sources and Probes、Logic Analyzer和SignalTap II,乃至Virtual JTAG,唯有SignalTap II的性能是最好的,对于高速应用的调试是最有帮助的。但与此对应的是,使用SignalTap II需要FPGA器件本身付出比较高的资源消耗。

尽管如此,SignalTap II还是很受高端FPGA应用群体的亲睐。虽然特权同学项目应用中使用的多是中低端的器件,但最近的项目上采集的一组控制信号受限与单机示波器的带宽和存储深度,很难准确的摸透信号的脾性。因此只能借助于某个现成的FPGA模块,在Quartus II中搭建一个SignalTap II可访问工程,并将待采集的信号连接到采集模块的可用IO管脚上,在这个简单的“逻辑分析仪”中,一定要连接上采集和被采集模块的地线。

关于SignalTap II的使用方法,不是本文谈论的焦点,建议大家去消化《Quartus II Handbook.pdf》的Chapter 15: Design Debugging Using the SignalTap II Embedded Logic Analyzer。

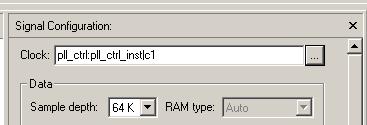

通常示波器都有一个采样频率,说白了就是示波器根据这个采样时钟每隔固定时间去读取当前接口信号的电平。这个采样频率越高,那么相对而言就能够更准确的还原信号的真实波形。那么对于SignalTap II这个“虚拟”逻辑分析仪而言,它的采样时钟是谁?如何设置呢?很简单,如图1所示,设置好这个Clock就可以了。这个Clock可以是FPGA外部输入时钟,也可以是经过PLL分频或倍频后的时钟。有了PLL的帮助,这个采样频率就可以被设置的“游刃有余”了。

图1

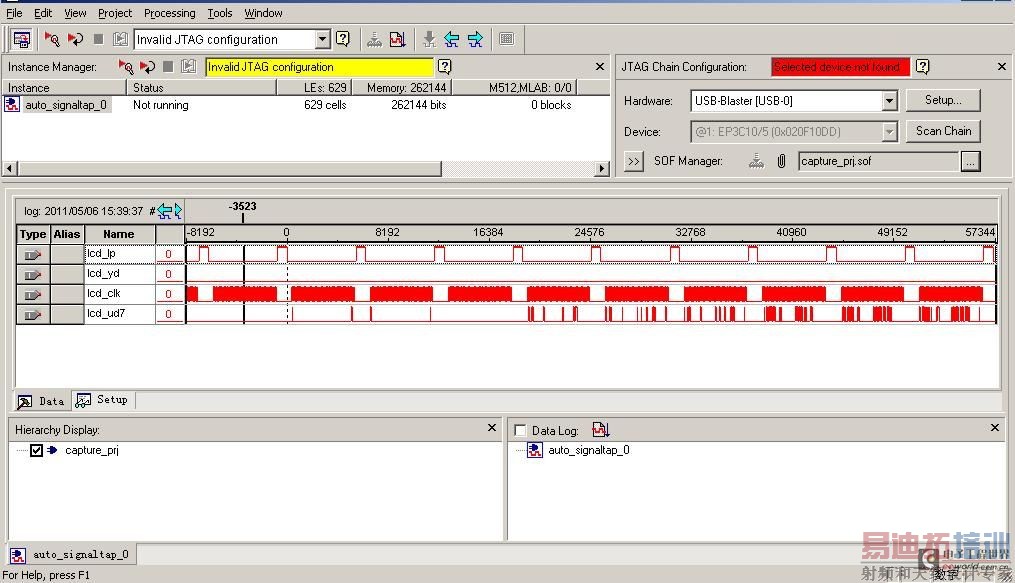

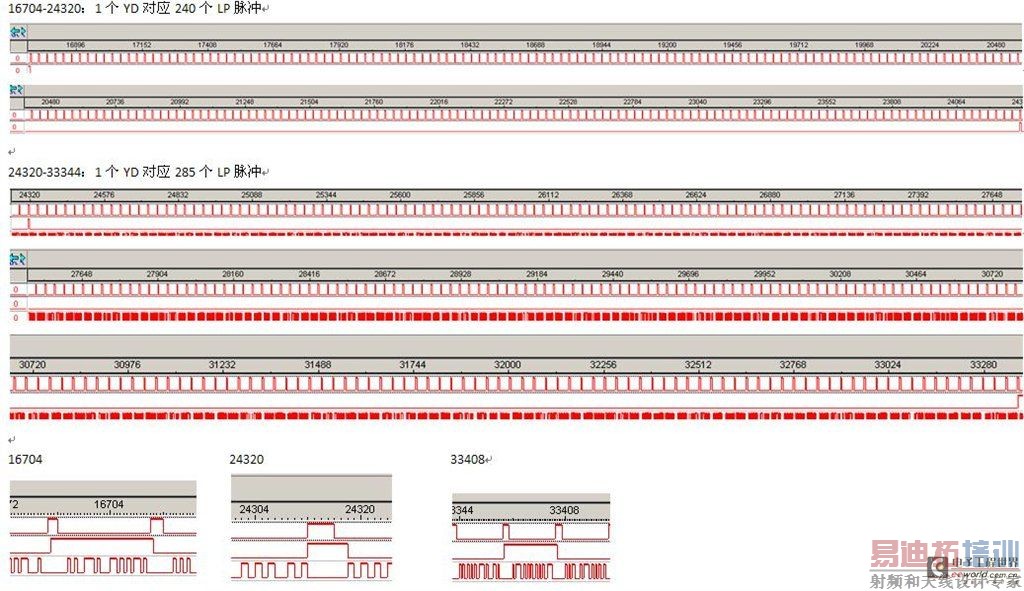

关于存储深度,图1的Data选项中也可以进行设置。触发条件、触发模式等等设置SignalTap II中都有很灵活的支持。用户可以根据自己的需要灵活的调整。具体的使用方法都可以在软件的handbook中找到。图2和图3是特权同学的一个“虚拟”逻辑分析仪应用和采集信号的分析,发现这个“虚拟”逻辑分析仪还是蛮实用的,至少能够在没有先进调试设备和更好调试手段的情况下帮助信号的分析。

图2

图3

FPGA器件在嵌入式开发中真的是非常实用,哪怕你不用它去做项目做产品,只要掌握了它的设计精髓,也许它一不小心就能够成为你的开发设计过程中的一个“小助手”,大大加速产品问题定位和开发进度。

上一篇:什么是纹波和谐波

如何测量纹波和谐波

下一篇:大范围测量电感及电容方法