任意波发生器是越来越重要、应用越来越广的一种

信号源。拿到一个高性能任意波发生器的技术手册,很多工程师会发现,越来越难看懂和理解任意波发生器的相关技术指标和功能特点,比如:什么是真任意波(True arb)?什么叫插值DAC(interpolating DAC)?什么叫去毛刺DAC(Deglitching DAC)和分布式重采样(Distributed Resampling)?什么是Doublet Mode?什么是数字上变频?什么是动态序列(Dynamic Sequencing)?什么是流盘播放(Streaming)

等等。为此,这篇文章基于“Agilent Fundamentals of Arbitrary Waveform-A High Performance AWG Primer”参考手册,介绍现代任意波发生器所涉及的相关的基础知识。

1 AWG采样理论

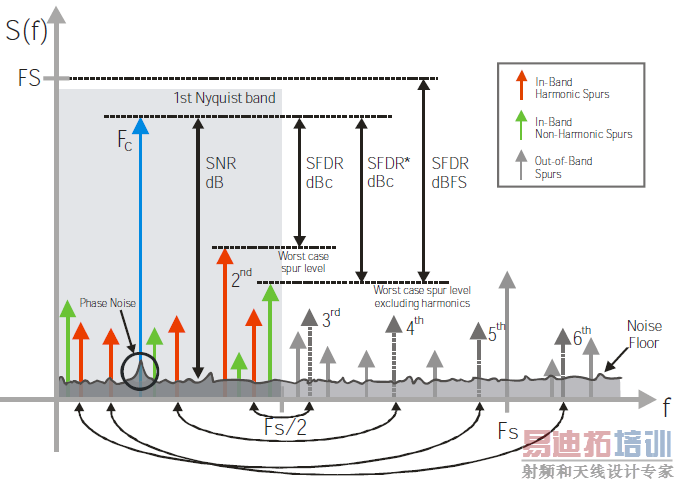

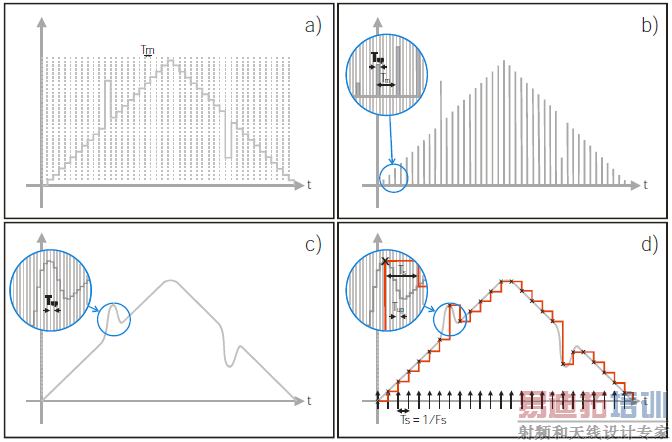

图1 奈奎斯特采样理论

DAC和ADC一样,也需要满足奈奎斯特采样定理,即转换速率(采样速率)需要满足:

Fs>2 x Fmax

Fs是转换速率/采样速率;

Fmax是产生目标信号的最高频率分量。

如果不能满足奈奎斯特定理,会导致频率混叠,会丢失想产生信号的高频信息。

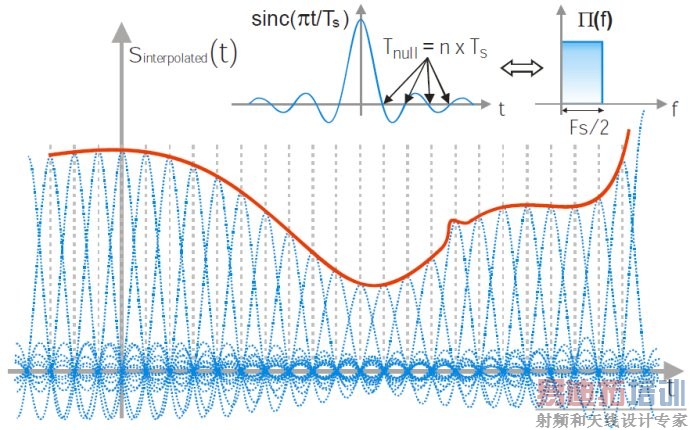

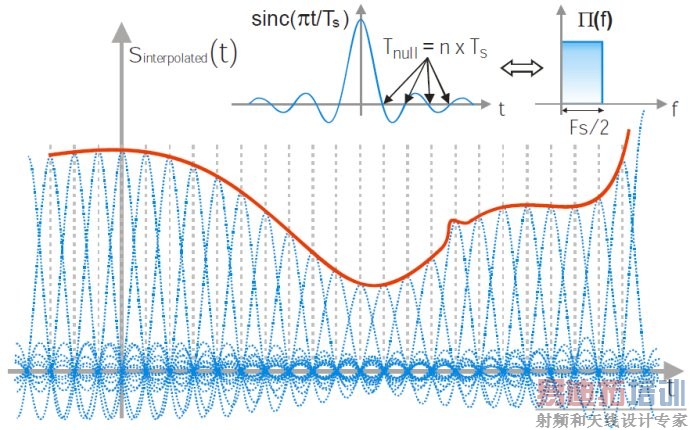

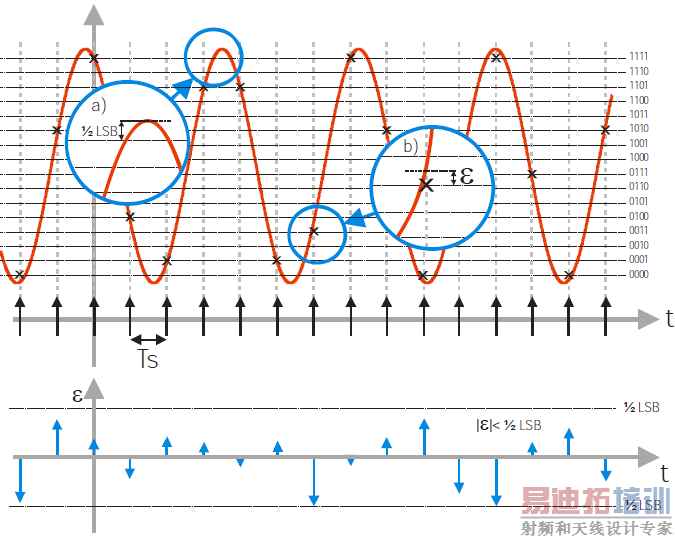

图2 带限信号的波形重建

用一个理想的奈奎斯特滤波器进行滤波,可完整重建数字形式域的信号波形,相当于在实际采样点之间进行插值,插值后的信号经过DAC转换后,可完整重建模拟信号。理想奈奎斯特滤波器的频域特性是带宽为Fs/2的砖墙低通滤波器;时域特性是Sinc函数。

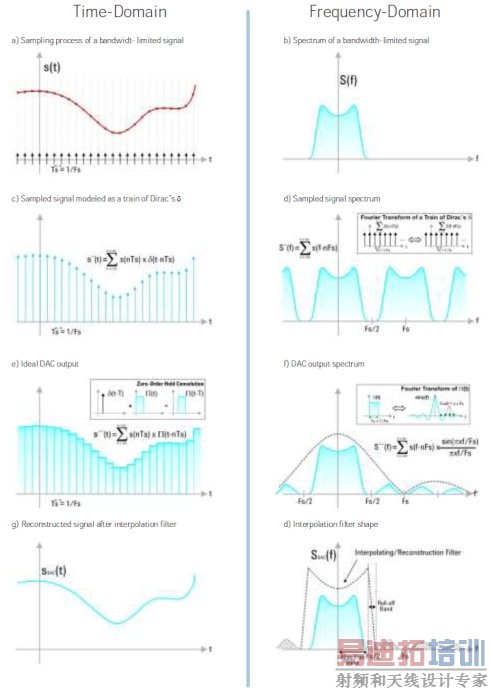

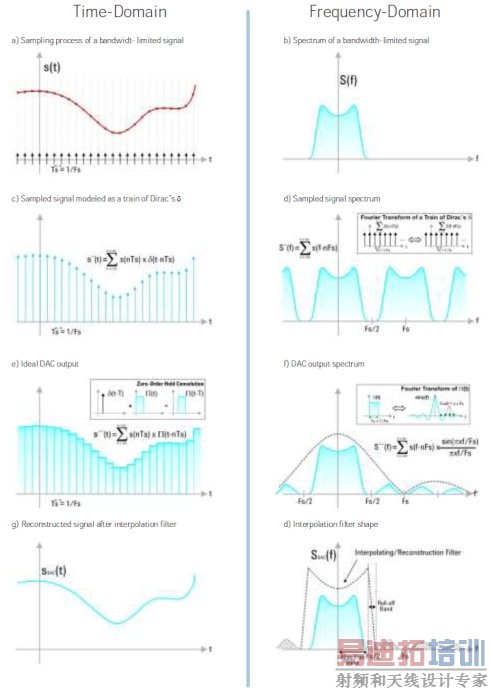

图3 理想任意波发生器的信号处理过程(时域和频域对应)

上面这些图从时域和频域角度展示了DAC转换前后波形的特征。对于一个带限信号,纯数字化的信号的频谱是周期拓展的,但是理想DAC实际输出的波形的频谱却不是周期拓展的。因为数字化的信号相当于与一脉宽为1/Fs的脉冲进行了时域卷积,在频域中相当于与一个Sinc函数进行了乘积运算,所以会有许多旁瓣产生。可以采用内插的方式在数字域里滤除拓展的频谱,也可以采用比较好的模拟滤波器在模拟域里滤除拓展的频谱,或者采用组合的方式进行滤除。刚好满足奈奎斯特采样定理的波形重建实际上是比较困难的。

2 AWG架构

下面分析常见的几种AWG架构。

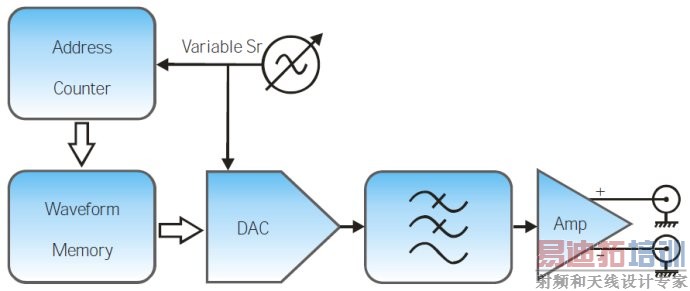

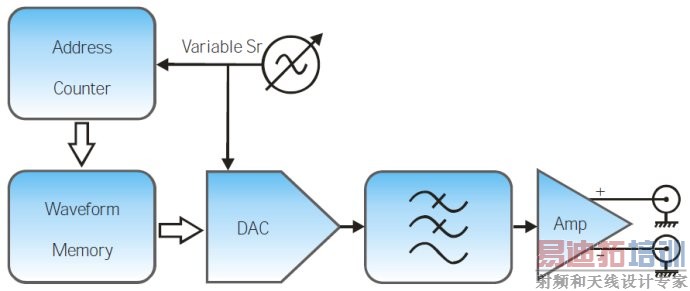

图4 真任意波(true-arb)架构AWG框图

真任意波架构如上图所示,样本被一个接着一个从内存中读取,DAC把它们转换成模拟信号,使用使用者设置的固定采样速率。内存的数据读取速度由采样率决定,内存的数据被顺序地读取。

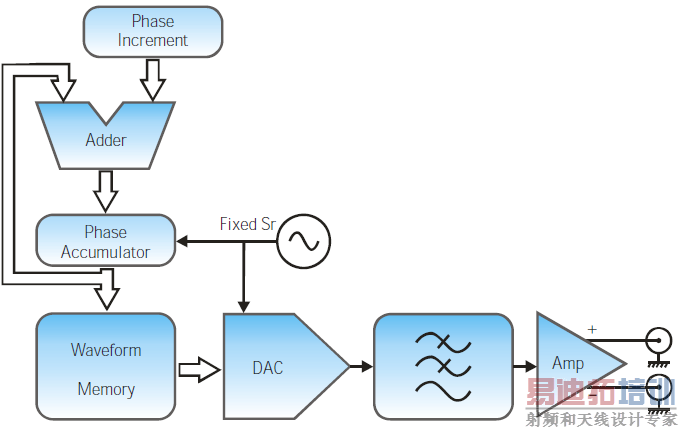

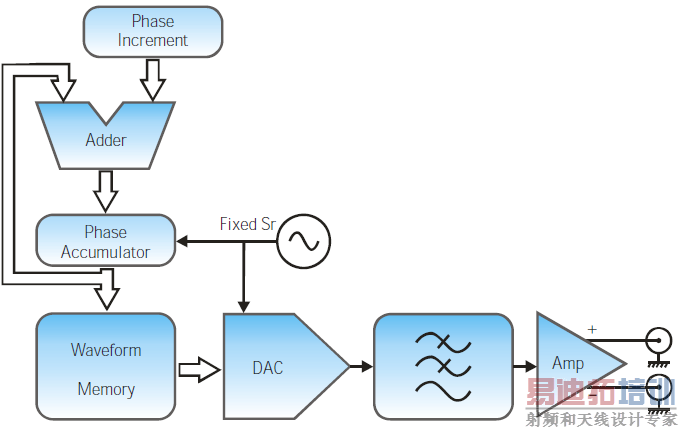

图5 直接数字合成(DDS)架构AWG框图

直接数字合成即DDS架构如上图所示,这里DAC工作在固定的采样速率,使用者控制存储在内存里的波形的重复速率。对于每个DAC的时钟周期,通过改变相位累加器的相位值,去确定内存的接入地址。内存数据不需要顺序读出。这种架构允许无缝改变存储在内存中波形的重复频率,允许直接频率扫描或PM/FM调制信号的产生。因为这个原因,DDS成为流行的函数发生器和低端任意波发生器的常用架构。

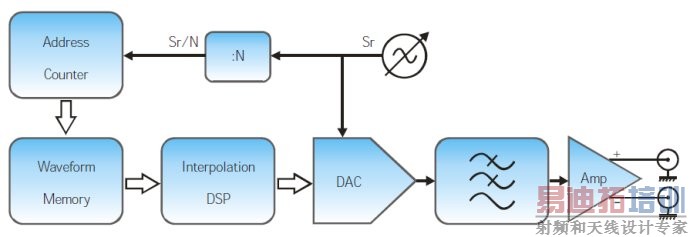

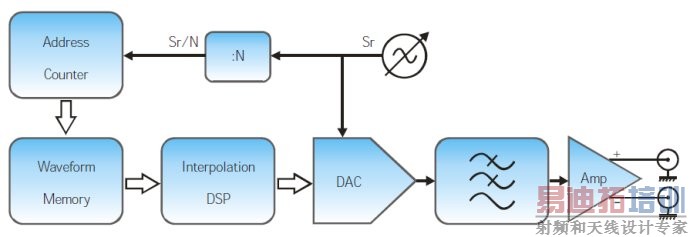

图6 内插DAC(Interpolating DAC)架构AWG框图

内存DAC的架构要求DAC的采样率很高,高于内存的读取速率。内插DAC架构是在波形读取器件和DAC器件之间增加一个内插DSP处理器,内插函数可以是线性内插,或FIR低通滤波器内插。这种架构的益处是不需要太快的内存接入速度,可以达到高品质信号质量。但是最大频率分量仍然受限于内存接入速度,而不是DAC采样速率。

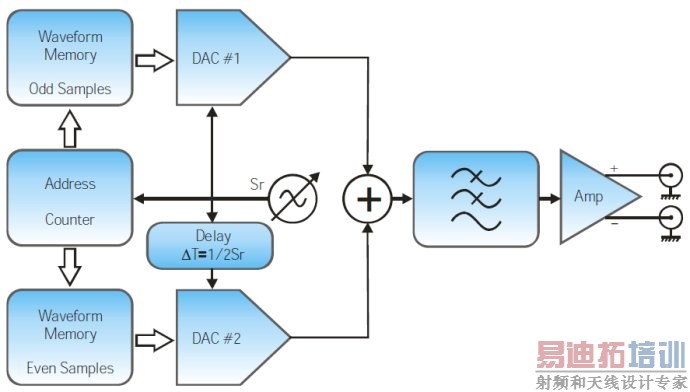

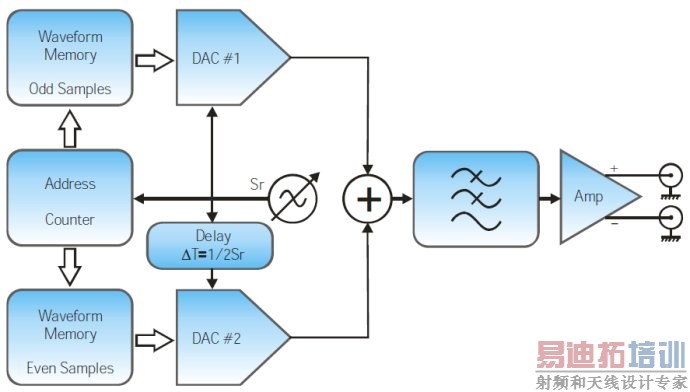

图7 伪内插DAC(pseudo-interleaving DAC)架构AWG框图

伪内存AWG架构通过组合两通道AWG或2个DAC,实现等效采样率加倍的目的。两通道间的时差必须是采样周期的一半;样点分成奇数点和偶数点,分别存在各个通道中。这种技术有效地扩展了可用的频率范围,也能够提升每个DAC的信噪比(由于两个通道的DAC的噪声是不相参的),但是信号品质对时序精度和通道频响失配都非常敏感。

3DDS和True Arb对比

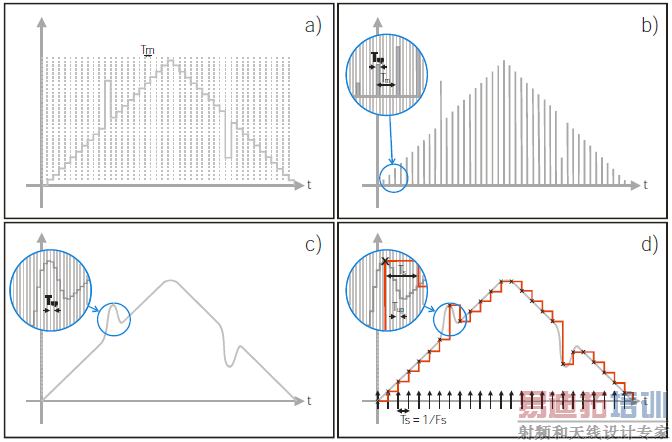

图8 DDS架构AWG,两种不同的存储设置,产生一个三角波

上图是用两种不同波形内存设置来产生一个三角波。a的时间分辨率低于b。时间间隔误差TIE图表明较高分辨率波形具有较低的失真,虽然输出的采样速率是一样的。

图9 True Arb的快信号处理过程

上图是真任意波AWG的信号处理过程。存储在内存里的原始信号是较高采样率的,内插低通滤波器增加点的密度(也可以直接存储更高采样率的波形),DAC输出的波形产生带快信号的模拟信号。

4DAC量化噪声

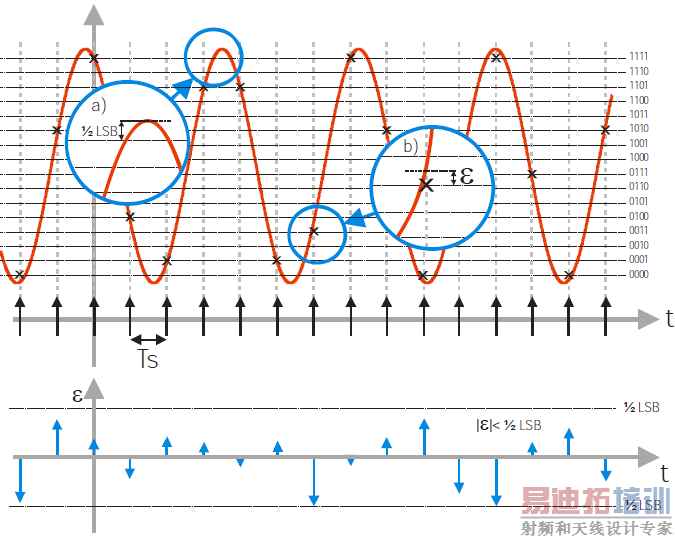

图10 在被采样的波形上分析量化噪声

量化噪声能够作为采样波形自身进行分析。量化噪声波形的上下边界是+-1/2LSB,时间上与波形一致。输人波形的幅度可能超越1/2 LSB(a),仍然保持边界错误条件(b)。

只考虑量化噪声的信噪比SNR或SQNR(信号到量化噪声比)公式:

SNR(dB)=6.02N+1.76dB+10log10(Fs/2B)

B是带宽。

过采样DAC能够提升信号到量化噪声比。理论上的分辨率提升(以位数表示)可由下面公式得到:

提升位数=10log10(过采样因子)/6.02

这意味着,对于非内插DAC,采样率增加到4倍,等效于提升1位分辨率。

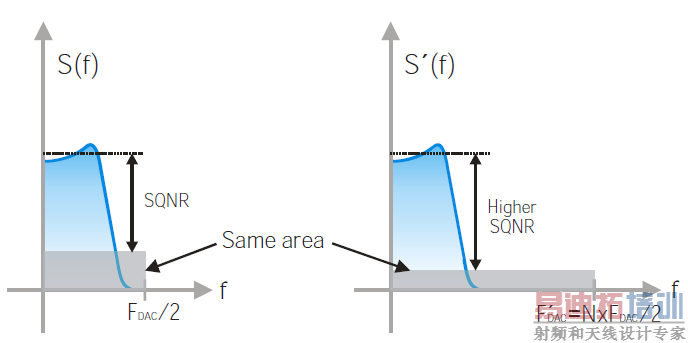

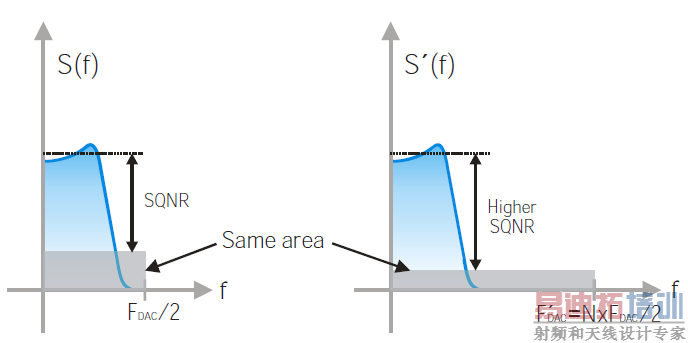

图11 量化噪声在完整奈奎斯特带宽上的拓展

量化噪声拓展到完整的奈奎斯特带宽。对于一个带限信号,通过增加采样率可以减少噪声功率谱密度,由于同样的功率被分配到更大的带宽上。这种效果可被内插DAC架构的AWG利用。 [p]

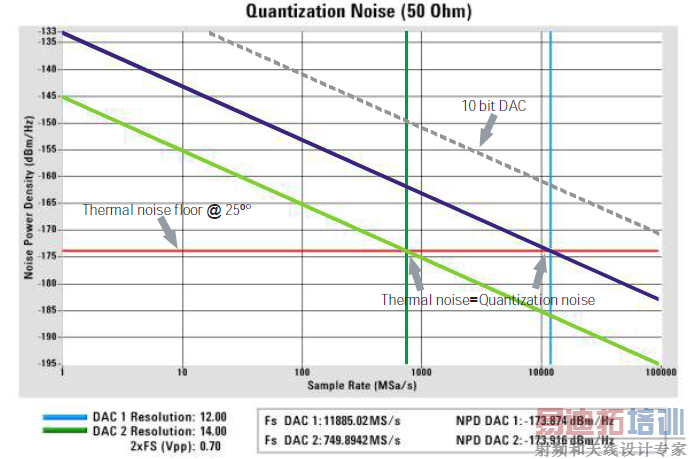

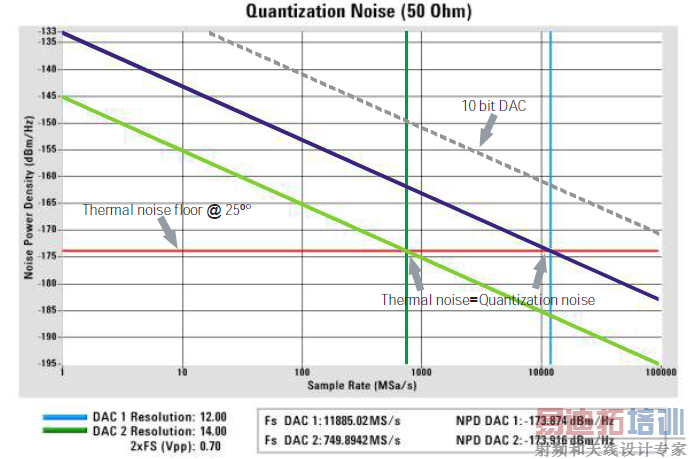

图12 12位和14位DAC的采样率和噪声功率密度的对应关系

上图是理想的12位ADC和14位ADC在0.7Vpp输出范围时的采样率和量化噪声功率谱密度对应图。红色的水平线代表自然界热噪声的功率谱密度(-174dBm/Hz)。量化噪声和热噪声在750MSa/s(14位ADC),12GSa/s(12位ADC)处相等。(这是M8190A的指标。)

5 AWG非线性

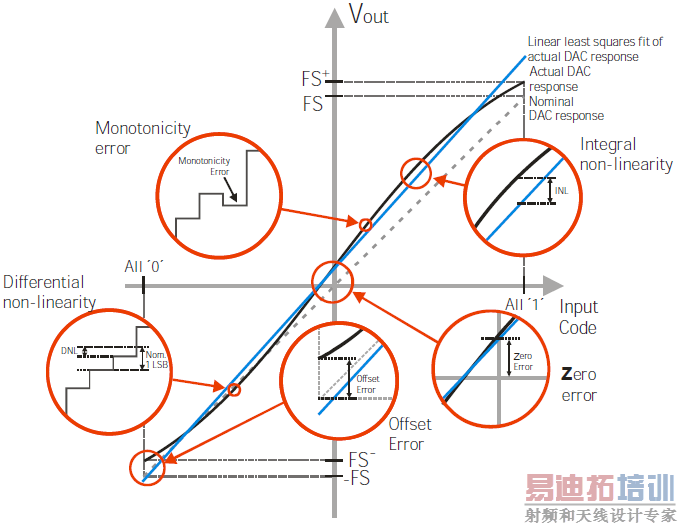

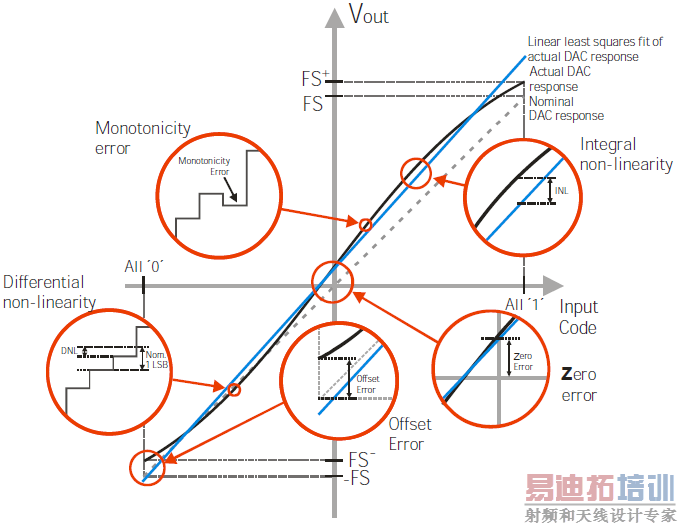

图13 DAC(AWG)非线性的静态表征

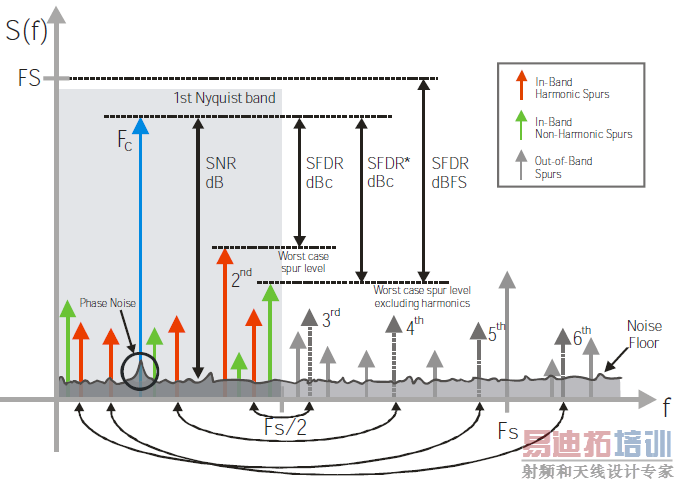

图14 DAC(AWG)非线性的动态表征

图15 高速DAC内部的两种电流源结构

6 高速DAC架构

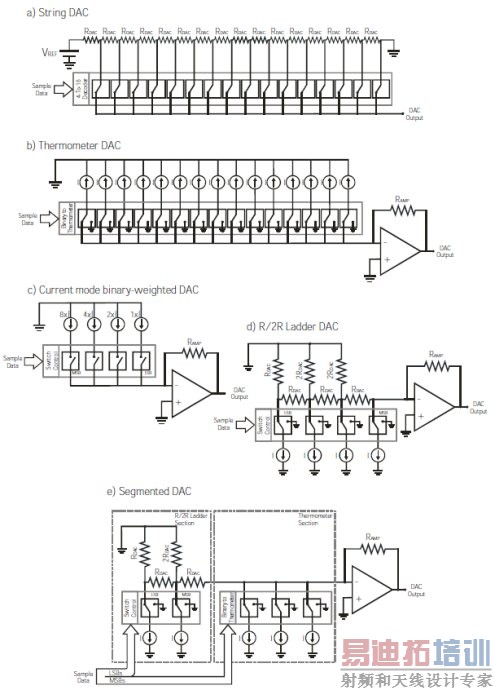

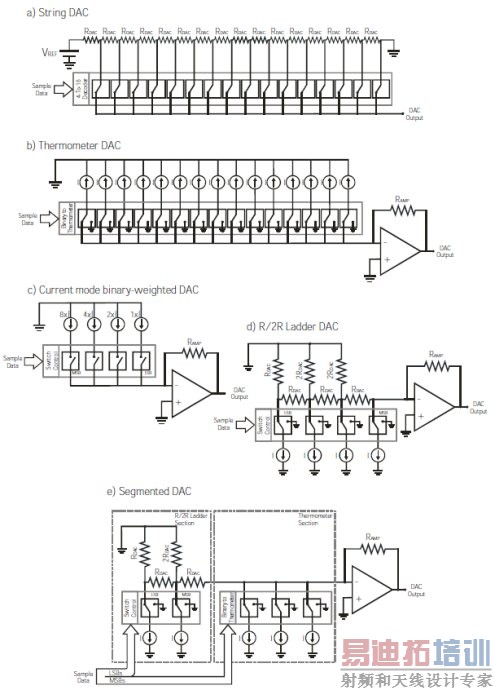

图16 当前最流行的几种高速DAC架构(以4位DAC为例)

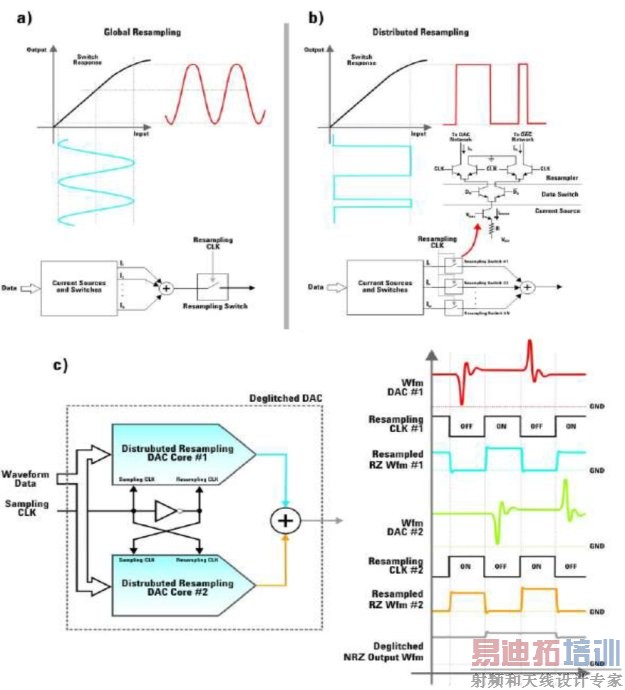

7 去毛刺DAC和分布式重采样

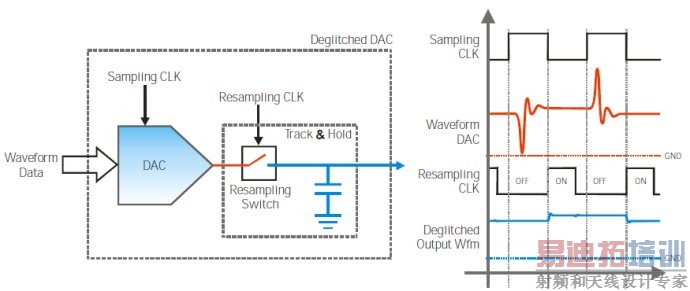

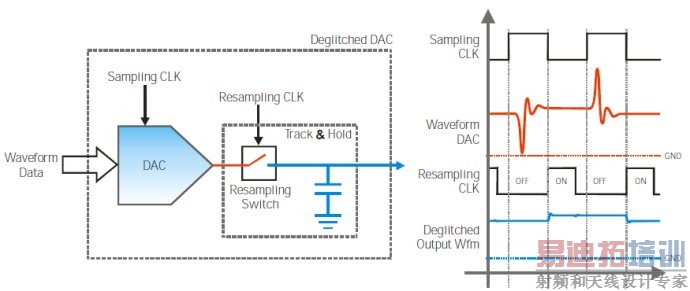

图17 去毛刺DAC设计框图和工作原理图示

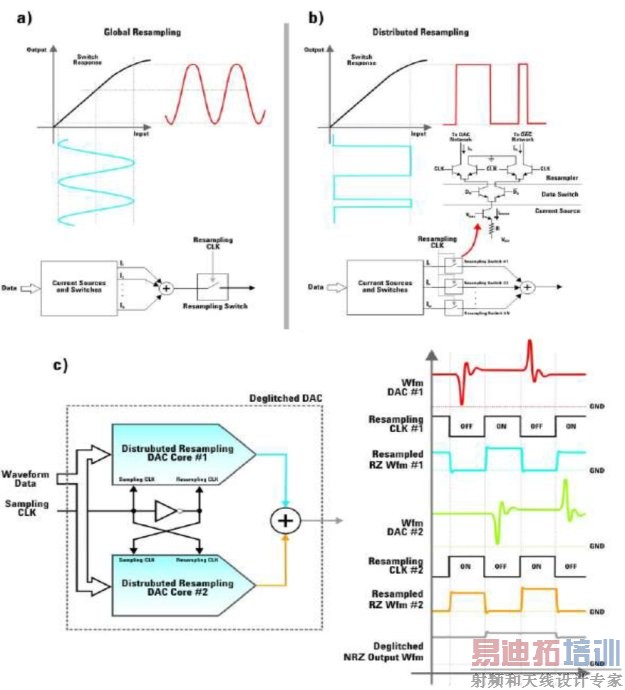

图18 分布式重采样架构及其工作原理图示

图18 分布式重采样架构及其工作原理图示

8 双核DAC架构

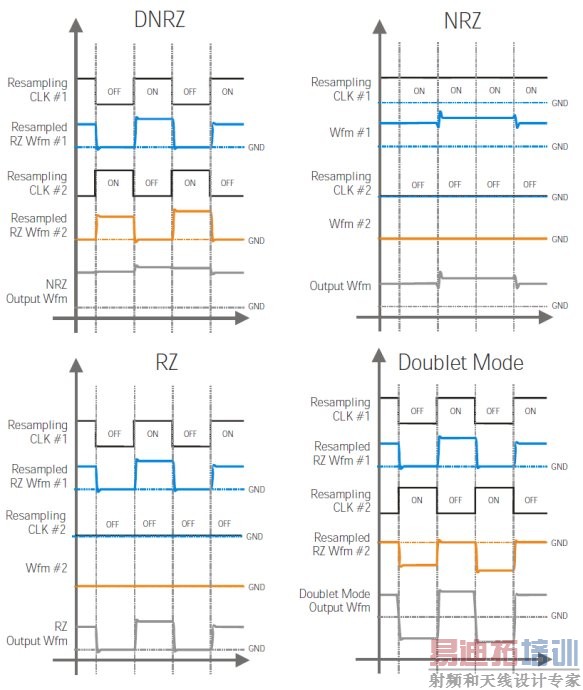

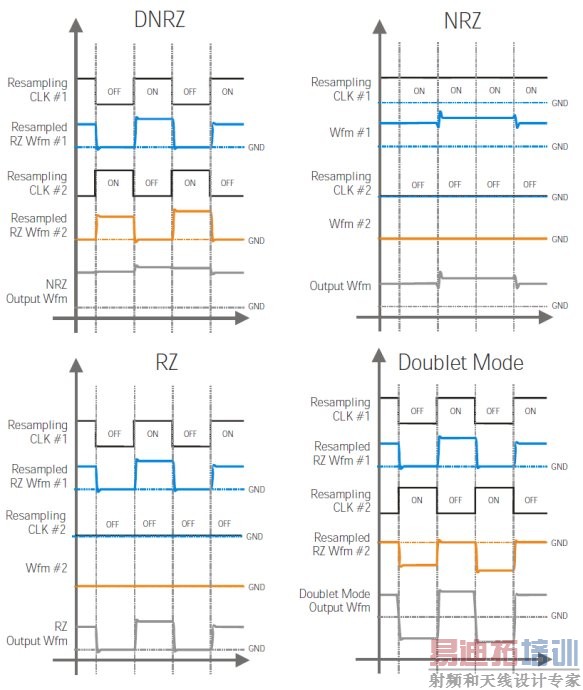

图19 双核DAC的几种不同工作模式

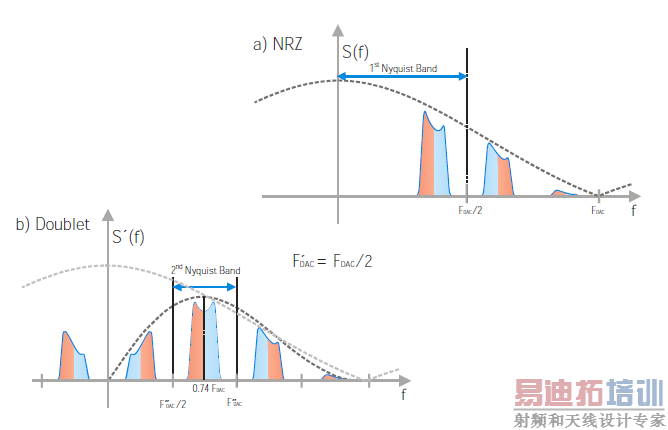

9 Doublet Mode

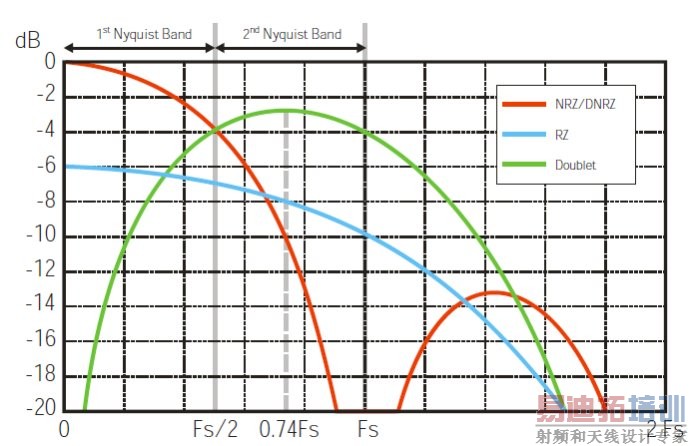

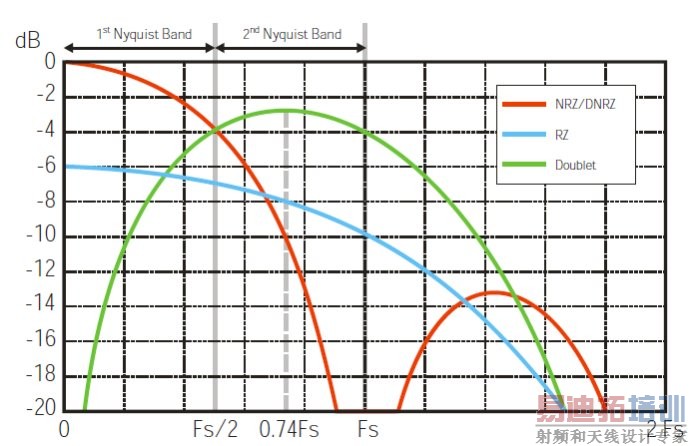

图20 双核DAC的几种工作模式的频响特征

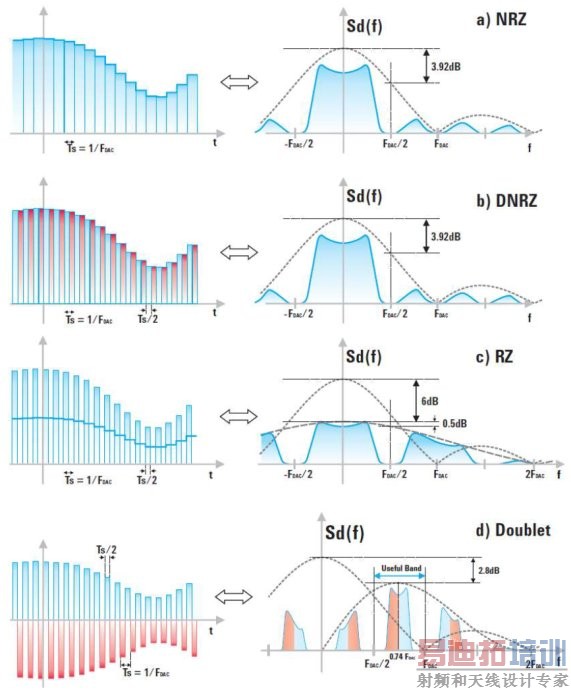

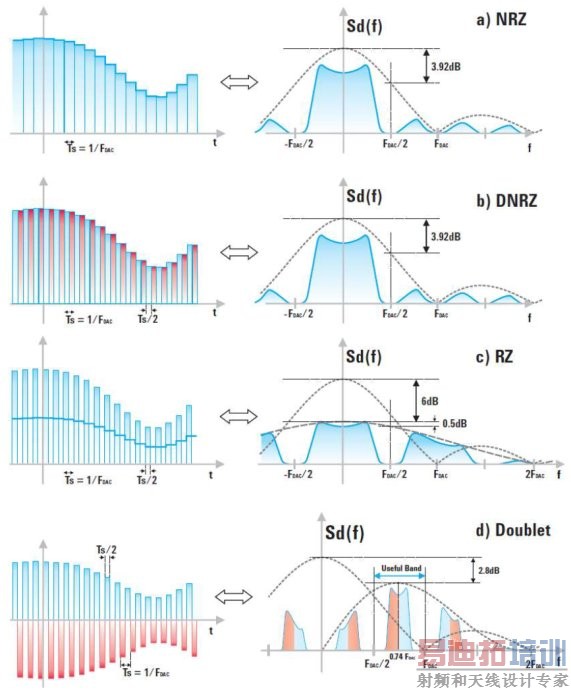

图21 双核DAC不同工作模式的信号产生特征

图21 双核DAC不同工作模式的信号产生特征

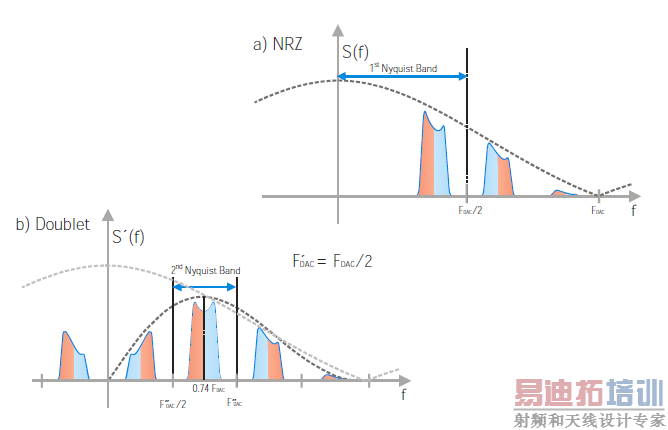

图22 Doublet Mode在带限信号产生上的应用

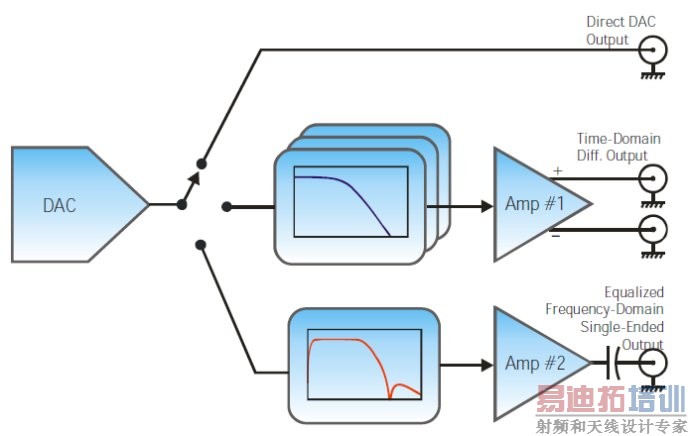

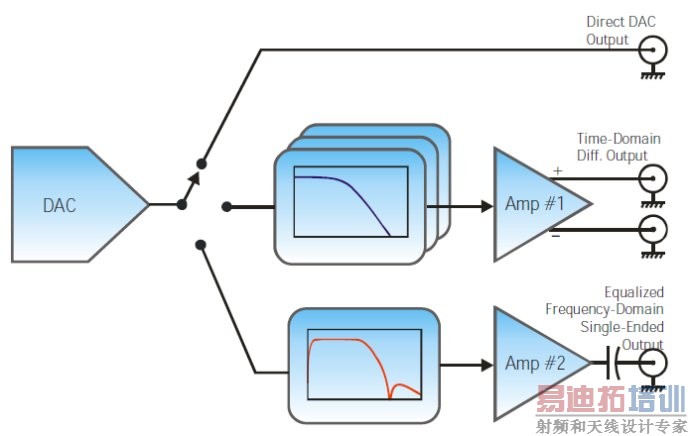

图23 AWG的不同信号输出路径

图23 AWG的不同信号输出路径

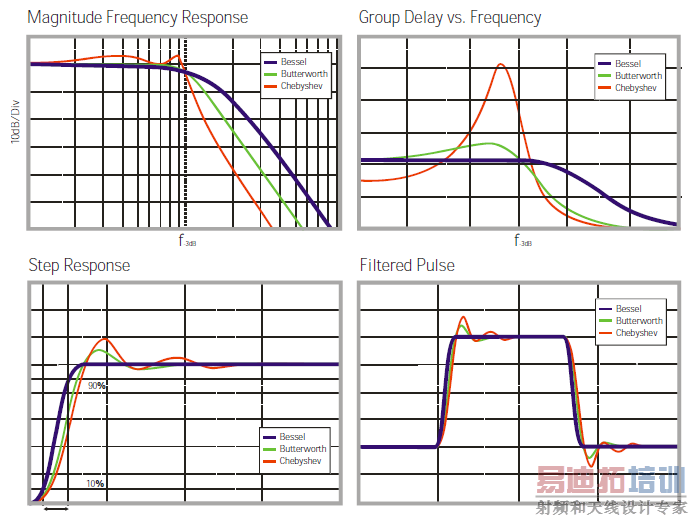

10 重建滤波器

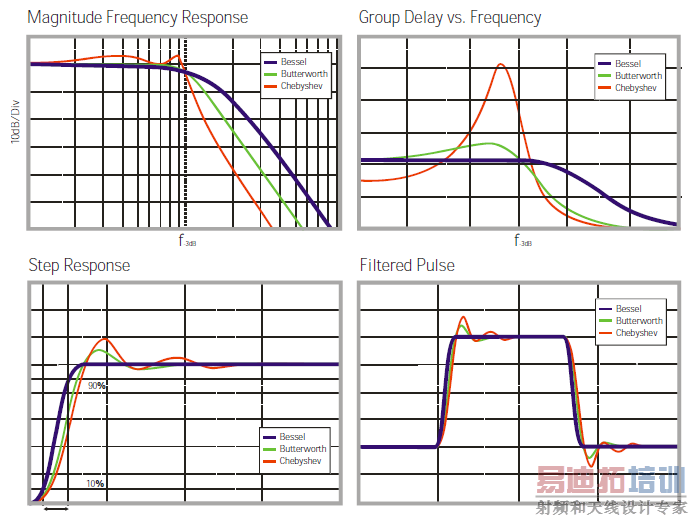

图24 AWG中常用的贝塞尔(汤姆森)滤波器,用于时域信号优化

图18

图18

图21

图21

图23

图23