- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用高速数字分析仪和专用内存软件调试更高速率 DDR 信号

录入:edatop.com 点击:

内存广泛应用于各种设备的单板。而随着电子产品对数据吞吐量的不断提高,内存也在更新换 代,进一步提升了速率,如新一代内存 DDR4,数据信号速率达到了 3.2Gbps。更高速率的内存信号,不仅 JEDEC 规范规定了更严格的测试要求和更多的测试项目,如对于 DDR4 还要求测试固有抖动 Dj,以及信号 的眼图模板测试等,而且对传统的内存测试软件中所使用的 DDR 内存信号读写分离方法,也构成了新的挑 战。本文将分析和介绍更高速率的 DDR 内存信号测试所面临的挑战以及力科的应对方案。

一、传统分析软件针对 DDR 信号的读写分离原理

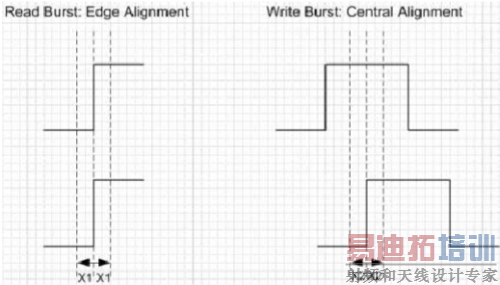

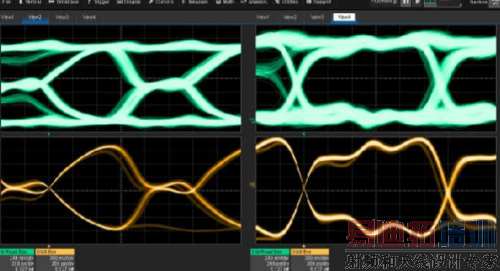

常用的 DDR 内存分析软件一般是通过 DDR 内存的 DQ 数据信号与 DQS 选通信号边沿 之间的时序关系来判别读与写的,即读突发时 DQ 信号和 DQS 信号边沿对齐,写突发时 DQ 信号和 DQS 信号中间对齐,如下图 1 所示,只要 DQ 信号和 DQS 信号之间的时序在[-X1, X1]范围内即认为是读突发,如果在[0.25*UI-X2,0.25*UI+X2]范围内,即为写突发,示波 器软件会进行优化设定 X1 和 X2 的值以尽可能准确的分离出读、写信号,不同示波器厂家 的软件也可能会有所区别。

图 1 常用的 DDR 内存分析软件所使用的读写分离方法

该方法对于速率较低的 DDR 内存信号来说会工作得很好,因为信号速率低,数据位间 隔 UI 就会比较大,也即读突发时的 DQ 和 DQS 的相对边沿位置数值与写突发时 DQ 和 DQS 的相对边沿位置数值相差比较大(相差 1/4 个 DQS 选通信号周期)。而当 DDR 信号速率越 来越高后,UI 将越来越小,此时即使是读突发周期,DQ 与 DQS 信号的边沿产生的偏移也 极有可能会被误识别为写突发,反之,写突发一样也可能会被错误的判别为读突发。

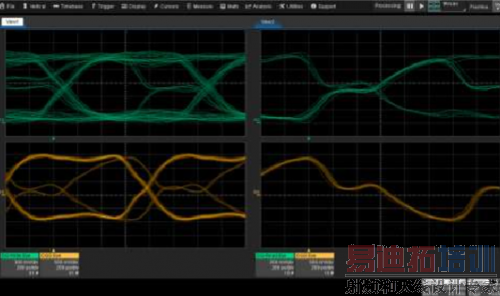

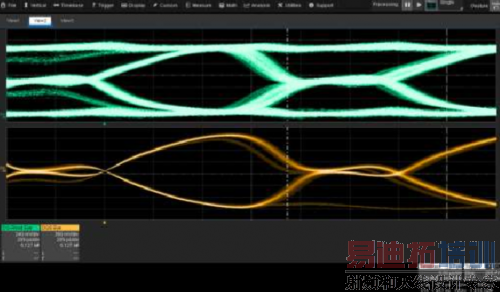

此外,由于电路板上的电子元器件的密集程度越来越高,而且内存类的芯片又都是 BGA 封装的,所以很多情况下难以在信号走线的最末端进行测试,从而导致测量到的信号出现反 射的现象,如下图 2 所示为一个 DDR3 信号的测试图示,左上和左下分别为写突发的 DQ 信号和 DQS 信号的眼图,右上和右下分别为读突发的 DQ 信号和 DQS 信号的眼图。从图中 可看出,写突发时 DQ 和 DQS 信号的眼图中也夹杂了读突发时 DQ 和 DQS 信号的眼图,原因正是读突发时 DQ 和 DQS 信号在接近电平 50%的位置有明显的台阶,此时 DQ 和 DQS 之间的时延将难以被准确测量和确定,也就是说使用传统的通过“读边沿对齐和写中间对齐” 的方法将难以精确的分离该情况时的 DQ 和 DQS 的读写信号。

图 2 某 DDR3 信号的读写信号眼图

二、基于高速数字分析仪及专用 DDR调试分析软件的内存测试方案

1、使用高速数字分析仪基于命令总线进行读写分离

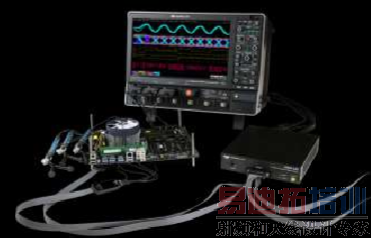

内存 DDR 接口都拥有并行控制总线信号,这些控制总线信号可以清楚的指明 DQ 和 DQS 信号是处于读突发状态还是写突发状态,以及这些信号来自于哪个芯片。所以可以通 过同时测试这些控制信号来对 DQ 和 DQS 信号进行读写分离。但一个明显的困难是,除了要测试 DQ 和 DQS 信号外,还需要额外再测试 4 个控制信号,若都使用模拟通道进行测试,则示波器的通道将不够用,而测试控制信号的目的是为了协助分离读写,所以完全可以使用数字探头来测试这些控制信号,然而新一代更高速率的 DDR,如 DDR4,速率比较高,达到了 3.2Gbps,传统的低速 MSO 将难以满足要求。为了应对这样的需求和挑战,力科推出了采样率高达 12.5GS/s 的高速数字分析仪及高带宽易于连接的数字探头。下图 3 所示为力科的高速数字分析仪 HDA125 与力科的 SDA820Zi-B 串行数据分析仪进行 DDR 信号测试验证的连接示意图。

图 3 力科的高速数字分析仪 HDA125

HDA125 具有 12.5GS/s 的采样率,存储深度大小取决于所连接的示波器,最多可配置16 条数字链路,探头的数字引线具有 3GHz 带宽,可采集 6Gbps 的信号,集成 9 英寸柔性“飞线”来连接难以抵达的连接点,且具有非常优异的负载特性(110k 输入阻抗和 0.12pF 的输入电容)非常适合于测试高速 DDR 内存信号。

2、DDR 内存专用调试工具包DDR

内存专用调试工具包是除了一致性测试工具包之外力科开发的另外一款专用于DDR 内存调试的工具,该工具更加注重于调试和分析,不是完全包括 JEDEC 规范要求的所有测试项目或者说只是 JEDEC 测试规范要求测试项目的一个子集。DDR 内存专用调试工具包具有如下功能和特点:只需按一个按钮即可实现 DQ 和 DQS 信号的读写分离(基于力科的 Qualify 一致性软件的读写分离原理);对 DQ 和 DQS 信号进行眼图和模板测量;对 DQ和 DQS 信号进行抖动测量和分解;包含一系列针对 DDR 信号的特定测量参数。下图 4 至图 7 所示为力科 DDR 内存专用调试工具包的界面:

三、使用高速数字分析仪与 DDR 专用调试工具包对 DDR 内存信号进行调试

下图 8 所示为一个 DDR3-800 的单板,读突发的 DQ 和 DQS 信号有一些反射问题,信号形状见上面图 2 所示。该单板上连接有 2 个模拟差分探头和 5 条数字通道,模拟探头采集了 DQ,DQS 信号连接到力科示波器 SDA 820Zi-B 的 C1 和 C2 上,数字探头采集了 CS,WE,RAS,CAS,CLK 信号通过力科的高速数字分析仪 HDA125 也连接到力科示波器 SDA820Zi-B 上。模拟探头和数字探头在测试之前做了时序上的校准。

图 8 某 DDR3-800 的 DDR 内存信号测试连接图

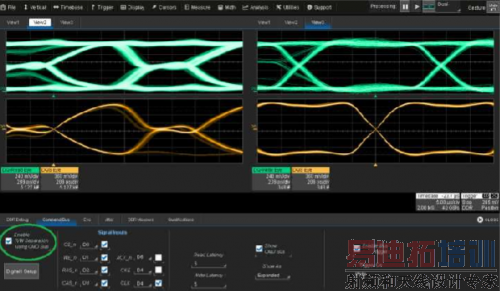

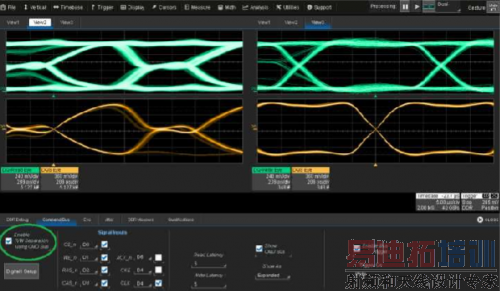

采集到的信号在示波器屏幕上的显示如下图 9 所示。同时在 DDR 调试工具包中输入对 应的命令总线,如下图 9 下方所示,此时读、写突发被分离出来并清晰的标注在波形上,类 似于力科的解码软件,DDR 的读写解码信息也以类似于表格的形式显示于波形窗口的下方, 每条解码信息与当前所显示的波形相对应,时间上同步,故也非常适合于查找和定位特定时 刻或位置的读写突发波形信息。

图 9 基于 HDA125 和 DDR 专用内存调试分析软件实现内存信号的读写分离

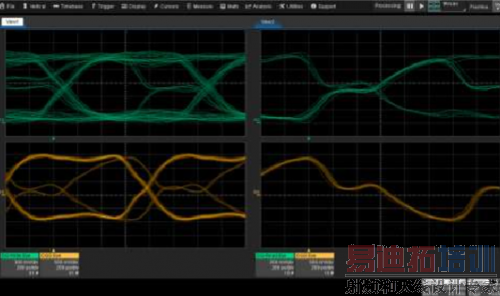

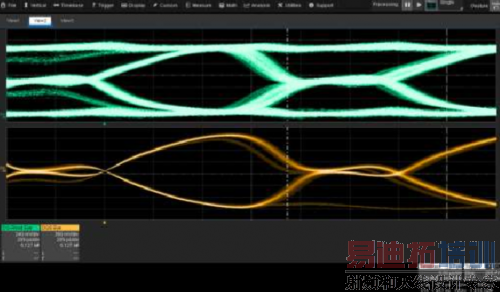

此时,读突发和写突发的眼图被准确的分离,如下图 10 所示:

图 10 DDR3 内存的 DQ 和 DQS 的读突发和写突发的眼图

四、利用虚拟探测工具应对 DDR 内存信号中的反射问题

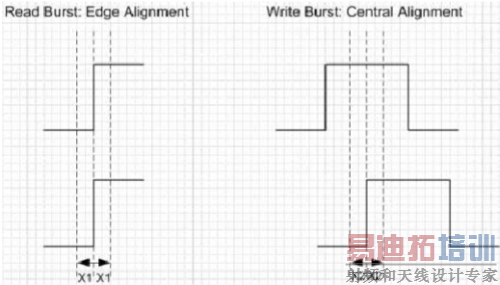

在上面的 DDR 调试示例中,读突发因反射问题导致信号出现明显的台阶,这将给读突 发时的时序测试带来错误的结果。而反射问题通常是因为测试点没有位于信号链路的最末端 所导致的。力科公司的虚拟探测软件 VisualProbe 能够用于解决此类问题。 VisualProbe 虚拟探测软件需要几个参数:测试点到末端(反射点)的传输延时、末端 的 RLC 参数以及特征阻抗。传输延时可以根据信号的反射位置测量得到,如下图 11 所示, 反射信号的往返时间约为 680ps,所以传输延时约为 340ps。RLC 参数可以从芯片手册中的 管脚参数得到,特征阻抗为 PCB 设计时所设定,通常为 50 欧姆。

图 11 DDR3 内存读突发时 DQ 和 DQS 信号上的反射信号传输延时测量

将相关参数输入到虚拟探测软件中:

图 12 虚拟探测软件 VisualProbe 参数设置界面

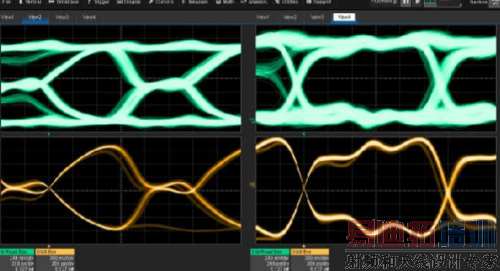

虚拟探测前、后的读突发 DQ 和 DQS 信号波形眼图如下图 13 所示,左边为原来的波形,右 边为虚拟探测后的波形。基于虚拟探测后的 DQ 和 DQS 波形可以顺利完成时序的测量。

图 13 读突发时虚拟探测前、后的 DQ 和 DQS 眼图比较

上一篇:日本最大的测试测量公司——安立(Anritsu)

下一篇:信号发生器里的信号源