- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

测量从触发开始

这一点对于示波器供应商来说同样重要。许多供应商提供100多个预定义的触发来帮助用户将常见和不常见的信号条件快速分开。这一方面提高了灵活性,但是另一方面,选择正确的触发本身要比实际捕获信号更加困难,因为触发具有多种多样的类型、速度、带宽、延时和软件等,而且每一个触发都需要在灵活性与死区时间之间进行权衡。 理解每种类型的触发以及相应的权衡可以帮助用户找出理想的触发方法来提高成功触发事件的几率。

两方面因素决定了示波器的触发性能:

- 触发灵活性描述了定义触发阈值或条件来适应各种被测信号条件状态以提高效率的简单程度。 大多数示波器提供了供应商定义的各种触发功能,包括参数最低值设定,比如电平或宽度等,但是没有提供一种方法来自定义这些参数。

- 触发死区时间是指示波器在相邻两次采集之间无法检测到触发的时间长度。这意味着如果感兴趣事件发生在死区时间内,那么它将错过触发条件。触发死区时间是所有触发架构的固有特性,但是我们可以采用一些方法和技术来最小化这个时间。 许多示波器供应商提供了基于软件的触发器来增强灵活性,但是由于需要后处理,这类触发需要较长的死区时间,因此不适合小概率和不频繁发生事件的检测。

1. 传统触发

边沿触发(逻辑信号从高电平变成低电平或从低电平变成高电平时开始采集数据)是目前最常见的示波器触发模式。大部分简单的调试和测试功能都是通过边沿触发进行处理,但是有时候需要一些更复杂的触发来隔离特定形状的信号或连续隔离多个形状的信号。示波器也包含了一些更高级的触发选项,提供了更高灵活性来捕获例如I2C或SPI等串行协议以及高级事件和信号特性,比如毛刺、矮脉冲、宽度、转换速率、超时等。

图1.这是一个基于数字信号处理的示波器框图。 采集内存和信号处理单元决定了示波器的采集更新速率和死区时间。

许多触发条件在硬件中执行,但是更为复杂的触发选项和信号认证通常在类似于图1中的软件中执行。软件触发提供了最佳的灵活性,但是也增加了必要的数据传输和处理时间,在这个时间段内示波器无法检测到新的触发,如图2所示。系统无法检测触发的时间段称为死区时间,这个时间往往比实际采集数据记录时间更长—换句话说,示波器触发系统的死区时间可能占据超过95%。这使得检测小概率或低频率事件变得更为困难,而且导致测试时间更长。 更糟糕的是,用户可能错误地假设预期事件没有发生,因为预期事件发生的概率太低以至于其在测量过程中没有被检测到。

[+] 放大图片

图2.该图显示了传统示波器的数据采集和分析过程,其中波形捕获(上)和连续处理(下)之间存在死区时间。

如果示波器的可用触发或信号分析能力无法满足任务的需求,那么用户的唯一选择就是采集较长的波形片段,并将这些片段的原始数据下载到电脑上进行后期处理来找到特定事件。但是这增加了整个系统设计过程的复杂度,同时由于数据传输延时和数据处理所需的时间,整个测试的时间变长了。

至页首

2. 生成触发,无需权衡

虽然大部分基于软件或智能触发选项可以满足电子电路的设计和测试需要,但是如果不将小概率事件迅速隔离或纠正,这些事件往往会使得产品开发时间拉长。由于示波器触发功能的局限性,用户只能使用供应商所提供的功能。

如果用户可以在示波器内自行开发自己的算法,那么就可以针对特定任务自定义仪器的功能,从而不受限于供应商提供的功能。比如,用户可以针对特定应用自行定义触发条件来专门捕获某个信号条件,这样就无需在PC上进行后续处理,从而大大减少测试时间,如图3所示。

为示波器提供在线数据处理以及重新编程算法的灵活性的关键技术是FPGA,FPGA从本质上来说是可编程芯片,它可以通过真正的并行机制高速执行自定义信号处理和控制算法。 FPGA的灵活性让用户可以修改或者增加特定的触发算法,同时高吞吐量的数据处理可在采集过程中实时地分析数据样本,而不是之后再进行处理。这可以避免死区时间、防止触发遗漏并帮助用户更快地检测小概率事件。

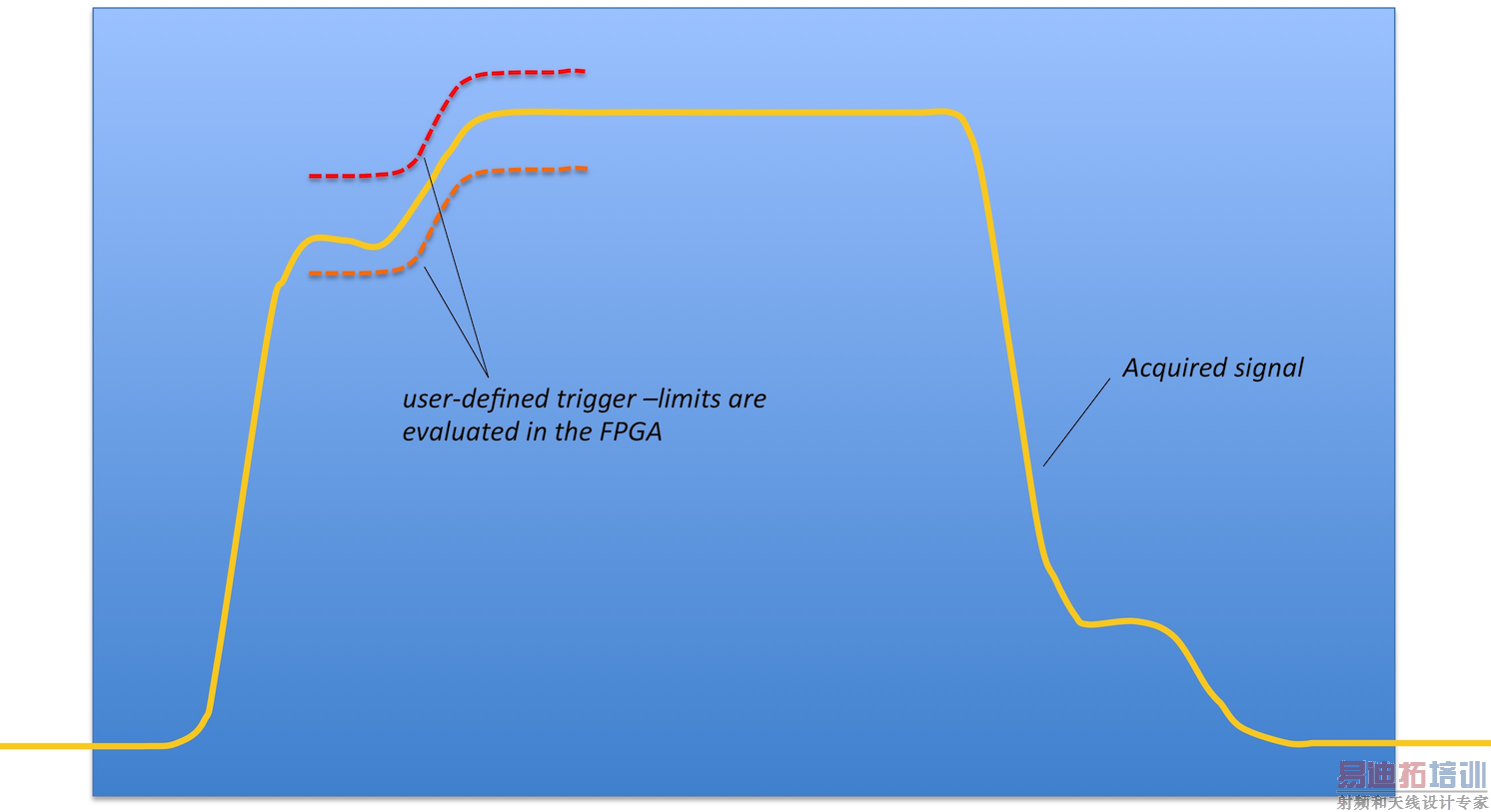

用户定义触发的一个例子是检测不符合标准触发定义的信号波形或电平跃迁,如图3中所示的信号。这种数字信号展示了一种非单调边沿,其原因可能是信号反射或被测电路的电源故障。标准边沿或宽度触发无法检测这种不期望的信号,而且使用常规手段进行检测基本不可能。我们需要研究一种新的触发精确并连续地捕获这个事件。为了解决这一问题,我们需要开发一个软件触发器;然而这种方法存在较大的触发死区时间,无法快速检测小概率事件。或者,可以采用用户可编程的FPGA来提供多个窗触发,当所有窗触发同时检测到有效触发条件时,就会将采集的样本与掩模进行对比,从而产生一个组合触发来采集信号。

由于FPGA可连续实时地评估信号,因此示波器既可以捕获单个信号,也可以采集连续信号,而且在两次采集之间不会存在死区时间。

图3.使用用户定义触发捕获特定信号跃迁;该功能在可重配置示波器的FPGA内实现。

至页首

3. 可重配置示波器

多年来,测试工程师们使用LabVIEW等软件工具来代替传统台式仪器内的固定软件,实现了系统测试以及测量结果分析和显示的自动化,从而节省了测试成本。 这种方法提供了灵活性并且利用了最新的PC和CPU技术。 然而,用户的需求往往不仅限于此,他们通常需要修改仪器的测量方式来更好地满足应用的需求。

传统的现成仪器由供应商定义并仅提供固定的功能;而NI率先采用FPGA技术提供更加开放、灵活的仪器。 于是,获得了兼具这两种特性的硬件: 固定、高质量的测量技术;最新的数字总线集成;用户可定制的高度并行逻辑,这种逻辑提供了低延时并直接与I/O关联以便进行在线处理。

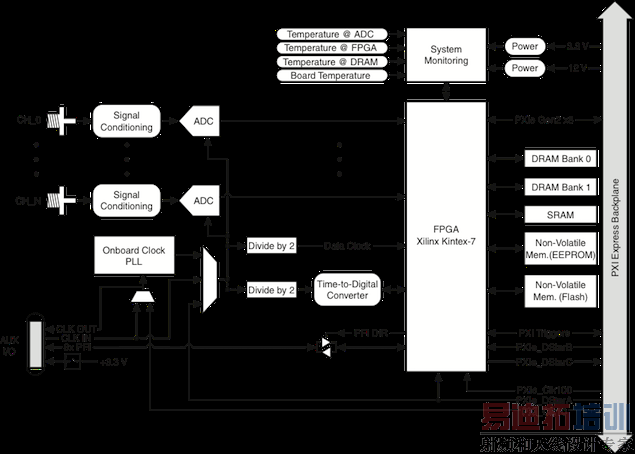

图4.可重配置示波器NI PXIe-5171R的功能框图。

借助FPGA内供应商提供的开放软件,用户可以扩展仪器的功能,比如自定义触发或额外定时或控制信号。 用户也可以在通过软件设计的仪器的FPGA中实现他们自己的算法,重新定义硬件功能来完成完全不同的任务。 比如,示波器可以变成一个实时频谱分析仪、瞬态记录仪、协议分析仪、射频接收器或者其它仪器。

设备成本是测试系统的一项主要成本,由于需要购买和维护的仪器数目更少,可重配置设备可以帮助用户节约设备成本。这一点对于需要长期(超过10年)使用的测试和仪器功能来说尤其有用,比如军用或者航天测试系统,它们常常需要再现已被淘汰(生命周期结束)的旧仪器的功能。

可重配置仪器非常适用于这一应用,因为通过重新编程可以模拟旧仪器的功能。测试系统软件只需少量的重新编程和重新认证就可与新仪器配合工作,因此能帮助用户节省成本。

此类仪器的一个例子是NI PXIe-5171R reconfigurable oscilloscope,它使用Xilinx Kintex-7 FPGA实时处理来自8个输入通道的采样。 图4展示了用户可编程的FPGA如何集成到数据路径中并提供对仪器的控制信号和定时信号的访问。

至页首

4. 结论

由于缺乏灵活性和实时分析能力,传统的示波器触发方法在捕获小概率和复杂事件上面临挑战。 新方法利用了FPGA技术来自定义触发功能,以满足复杂的触发条件以及实时信号处理和分析需求。

观看演示视频,了解如何通过自定义触发来避免死区时间。