- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的监测数字示波器设计

摘要:在核监测中,常将各种传感器输出的信号通过A/D转换器转换为数字信号,然后利用数字信号处理技术对各种核信号进行数字处理。为了准确测量核信号数字波形的各种参数,对基于FPGA双口RAM的数字示波器进行了设计和测试分析。实验表明,该数字示波器能准确获取核信号的数字渡形及各种参数的值,可对核信号的波形进行录制、回放和精确分析,为核监测及其仪器准确设计提供有力的保证。

福岛核事故促进了核监测仪器的飞速发展。在核爆监测中,需对核辐射的各种信号如光辐射、放射线沾染、冲击波、电磁辐射等进行测量,通过测量这些信号的时间、幅度和信号波形信息,判断核爆炸的时间、位置、方式和当量等。为了将信号存储、分析及各种数学处理,需要将核信号转换为数字信号。基于FPGA的数字存储示波器可以实现核信号的采集、存储及各种处理,获取核信号的各种参数,输出报警信息,再将获取的信号通过GPRS、北斗1和数传电台等多种方式传送至指挥中心,为核监测决策提供数据支持。下面就基于FPGA双口RAM的数字存储示波器进行设计研究。

1 FPGA简介

现场可编程门阵列(FPGA)是在专用集成电路(ASIC)的基础上发展起来的一种新型逻辑器件,是当今数字系统设计的主要硬件平台。其主要特点就是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。在修改和升级时,不需额外地改变PCB电路板,只要在PC机上修改更新程序,使硬件设计工作成为软件开发工作。

通过编程可以立刻把一个通用的FPGA芯片配置成用户需要的硬件数字电路,因而大大加快电子产品的研发周期,降低研发成本,缩短产品上市时间。FPGA具有高密度(一个器件内部可用逻辑门可达数百万门),运行速度快(管脚间的延时小,仅几个纳秒)的特点。用FPGA设计数字电路可以简化系统设计,缩小数据规模,提高系统的稳定性。FPGA不仅可以解决电子系统小型化、低功耗、高可靠性等问题,而且开发软件投入少、芯片价格不断降低,这使得FPGA占有越来越多的市场,特别是对小批量、多品种的产品需求,使FPGA成为首选。同时FPGA的Inte llectual Property(IP)越来越被高度重视,带有IP内核的功能块在ASIC设计平台上的应用日益广泛。尤其是FPGA很方便设计各模块并行处理,极大地提高信号处理速度。由于FPGA的上述优点,基于FPGA的各种仪器设计技术得到了越来越广泛的应用。

2 基于双口RAM的数字示波器设计

2.1 基于双口RAM的数字示波器的设计原理

核辐射探测传感器将核辐射的各种信号转换为电信号,该电信号为模拟信号,然后放大、成形等电路对模拟信号进行适当的调理,高速A/D转换器将模拟信号转换为数字信号,FPGA对该数字信号进行数字滤波、存储等处理。基于双口RAM的数字示波器原理图如图1所示。

2.2 模/数转换电路

要对核信号进行精确的数字分析处理,就需要对核信号进行精确的数字取样,取样频率越高,取样结果越准确。AD9244是Analog Devi ce公司生产的14位高速高精度模/数转换器,具有750 MHz输入带宽,采用流水线技术,每个脉冲可进行一次A/D变换,最高允许抽样速率达到65 MHz。它专门应用于峰峰值小于2 V的小信号模/数转换系统,其最大的特点是体积小、功耗低、精度高。输入模拟量在-1~1 V之间时,溢出位为0,输入模拟电压为-1 V时,输出14位数字量为00000000000000;输入模拟电源为0 V时,输出数字量为10000000000000;输入模拟量为1 V时,输出数字量为11111111111111。输入模拟量低于-1 V时,溢出位为1,输出数字量为00000000000000;输入模拟量高于1 V时,溢出位为1,输出数字量为11111111111111。A/D取样示意图如图2所示。NaI(T1)闪烁体探测器核脉冲信号经放大整形后输出近高斯波形模拟信号,再经8138转换为差分模拟信号进入AD9244,FPGA输出50 MHz时钟信号ADC_CLK到AD9244作为ADC的时钟源,AD9244则输出50 MHz 14位数字信号及1位溢出位信号到FPGA,完成模拟核脉冲信号的高速采样。每个ADC_CLK脉冲,ADC完成一次模/数变换。

2.3 双口RAM IP核定制

存储核监测数字信号既可以使用FPGA内部的FIFO存储器,也可使用内部RAM存储器。FIFO存储器控制简单,使用方便,但要访问存储数据的中间数值不很方便;RAM存储器使用更灵活,可以利用地址来处理RAM中的任何一个数据。在FPGA内部,RAM有两种类型,分别是BlockRAM和Distribute RAM。其中Block RAM为硬件RAM,集中分布在FPGA内的一个区域,利用Block RAM存储数据时,不占用其他逻辑资源。Distribu te RAM是由FPGA内的逻辑元件综合成的存储单元,广泛分布在FPGA的各个区域,离逻辑单元电路较近,用于存储各逻辑电路处理的信号。数字示波器存储的波形数据量较大,所以在双口RAM采用Block RAM实现。

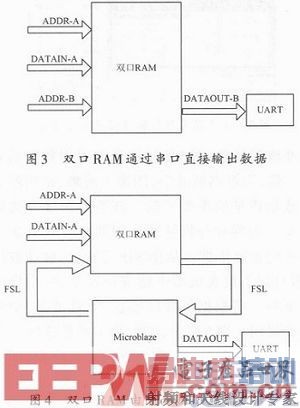

AD9244输出的数字信号为14位,所以RAM的数据宽度设置为16位,双口RAM数据读、写可采用相同的时钟控制;波形存储深度设定为1 024,即双口RAM存储1 024个采样点数据,所以双口RAM存储器共占用16 Kb RAM空间。由于核仪器工作在高辐射污染区,人员一般不能进入,通信一般采用无线通信方式,所以数据常采用串口通信方式。双口RAM数据直接经串口输出的原理图如图3所示。双口RAM数据经FSL总线由Microblaze处理器输出原理图如图4所示。A口用于RAM信号存储,数据宽度16位,深度1 024。B口用于RAM数据输出,若用ISE编写串口程序,B口数据宽度为8位,深度2 048;若采用PLB或FSL总线IP核方式,B口数据宽度定制为16位(16位RAM数据加载到32位总线的低16位上,总线高16位补零),深度为1 024。

[p]2.4 数字波形数据存储及波形输出

FPGA双口RAM(Dual RAM)数据输出控制可采用多种模式:存满输出模式、定时输出模式和波形参数触发模式,可用串口指令控制各模式间切换。存储满模式工作原理为Dual RAM存储1 024点数据和串口输出数据交替工作,每存储满一次数据就通过串口输出数据,串口输出完数据后重新采集和存储数据;定时输出为Dual RAM存储1 024采样点数据,存储满后待定时信号,设定每几秒输出一次波形数据;脉冲波形参数触发模式类似于通用数字存储示波器的输出触发模式,在波形数据写入RAM前对波形参数(如脉冲幅值、脉冲形状、脉冲宽度等)数据进行提取,当波形参数在需要的范围时,FPGA输出数字波形,该模式可以采集并输出指定参数的脉冲信号,可以对核爆炸的光辐射、电磁脉冲、冲击波、放射线沾染等各种效应信号波形进行录制、回放和精确分析,从而实现核爆的自动监测和识别。

3 对核脉冲信号进行测试分析

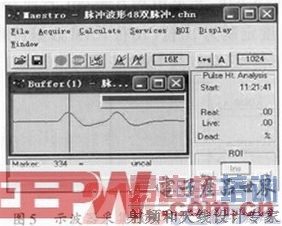

利用示波器可对核爆炸γ射线、光辐射、冲击波等传感器信号进行波形存储,通过存储信号特征参数判断核爆炸方式。示波器采集的NaI(T1)探测器经成形后的近高斯核脉冲信号如图5所示。将脉冲数字波形用OREC谱分析软件进行分析,由于输出的值是数字多道工作的实际值,比用通用示波器更准确,可进行更准确的分析。

脉冲波形形状:图5所示波形和通用数字示波器输出波形一致,为近高斯波形,图像更清晰,是判断成形电路信号成形质量的重要依据。该波形测量方法是在强辐射环境下观察和分析脉冲堆积的很有效方法及堆积判弃处理的重要依据。从图5还可看出,脉冲波形下冲偏大,需对探头放大成形电路进行调节,减小高斯成形电路的下冲。可根据脉冲的形状(混叠情况)初步判断放射源的强弱。图5所示,波形为示波器连续采得两个核脉冲信号。波形图中若测得脉冲波形密集,或出现脉冲重叠,则说明源较强;若脉冲稀疏,则源较弱。

基线值测量:该数值是探头放大成形电路调节和数字多道基线扣除的重要依据。图5中可读出基线均值为1 072,基线值的范围是1 069~1 074,波动大小为5,本次测量波形基线值偏大,需要对探头进行调节或在数字多道中对基线值进行扣除。

脉冲宽度测量:该值是抗干扰设计和基于脉宽测量反堆积的重要依据。可读出正脉冲(高于基线均值的取样点)共约125左右个取样点,脉宽为2.5μs,可以计算出核脉冲成形的宽度。如果脉冲宽度过小,则可能是干扰信号;过大可能是脉冲堆积信号。

脉冲幅值测量:该值是数字多道脉冲幅度分析器设计最重要的数据。可读出两个脉冲数字波形的最大值分别为1 384和1 381,扣除基线值后幅值为312和309;最大值左、右两个采样点的值与峰值差值也小于基线波动值,说明在该采样频率下,用逐点比较冒泡法提取幅度值是可靠的。脉冲幅度大小可基本看出射线的能量,从测量看出,幅值为312,对应为312道,通过数字多道能谱分析,其能量约660 keV,和波形测试用的放射源一致。所以从波形的幅度规律,可大致看出放射源主要是什么核素。

脉冲幅值时间测量:可读出在脉冲到来后的第66个采样点获取最大值。

噪声测量及抗噪处理:从图5波形还可看出,信号中存在一定的噪声,所以在数字多道处理时,可用DSPIP核对脉冲波形进行数字平滑处理,同时可通过设定一定的噪声容限,幅值低于噪声容限的都看作噪声,高于噪声容限的信号才可能是有效信号,对数字多道进行抗干扰处理。

脉冲波形和幅度谱比较分析:由图5信号源高斯波形代替核脉冲信号,可用该示波器的波形图和幅度谱图对比,比较脉冲幅度和幅度谱数据,可以对数字多道能谱仪的准确性进行测试验证。

4 结语

总之,利用基于FPGA的数字示波器,能很好地显示、存储和分析核信号,是核仪器的重要技术之一,有较大的使用价值。该设计利用VHDL对FPGA进行编程,并在编程中广泛采用并行和流水线技术,实现了信号高速处理;利用Block RAM定制双口RAM存储波形数据,大大节约了逻辑资源的使用。