- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

选择合适的转换器:JESD204B与LVDS对比

1 为不同应用提供不同选择

对于数据转换器 的高速串行传输,不同的应用有不同的选择。十多年来,数据转换器

的高速串行传输,不同的应用有不同的选择。十多年来,数据转换器 制造商一直选择LVDS作为主要差分信号技术。尽管有些LVDS应用可使用更高的数据速率,但目前该市场上的转换器

制造商一直选择LVDS作为主要差分信号技术。尽管有些LVDS应用可使用更高的数据速率,但目前该市场上的转换器 厂商可提供的最大LVDS数据速率仍然为0.8至1 Gbps。LVDS技术一直难以满足转换器

厂商可提供的最大LVDS数据速率仍然为0.8至1 Gbps。LVDS技术一直难以满足转换器 的带宽要求。LVDS受TIA/EIA 644A规范控制,这是一项LVDS核心制造商的行业标准。该规范可作为设计人员的最佳实践指南,提高不同厂商的LVDS发送器及接收器兼容性。同样,没有完全遵守LVDS规范的设计人员构建的产品将不符合规范,并会因兼容性问题在市场上遇到更大的挑战。

的带宽要求。LVDS受TIA/EIA 644A规范控制,这是一项LVDS核心制造商的行业标准。该规范可作为设计人员的最佳实践指南,提高不同厂商的LVDS发送器及接收器兼容性。同样,没有完全遵守LVDS规范的设计人员构建的产品将不符合规范,并会因兼容性问题在市场上遇到更大的挑战。

像LVDS一样,JESD204B归属Jedec标准组织,其可针对不同制造商之间的互操作性提供电气及物理需求指导。JESD204B的最大数据速率定义为12.5 Gbps,可实现比实际LVDS吞吐量高出10倍以上的优势。该性能不仅可为数据转换器 系统降低I/O需求及封装尺寸,而且还可通过降低静态功耗显著节省系统成本。

系统降低I/O需求及封装尺寸,而且还可通过降低静态功耗显著节省系统成本。

JESD204B规范支持AC耦合,可实现与使用不同供电级的不同技术节点的兼容。例如,28nm及更小的FPGA处理节点是典型的前沿制造工艺技术。转换器 晶体管节点由于需要自定义模拟设计,一般会落后于业界最佳FPGA几代。相反,LVDS通常采用DC耦合策略,其会提高转换器

晶体管节点由于需要自定义模拟设计,一般会落后于业界最佳FPGA几代。相反,LVDS通常采用DC耦合策略,其会提高转换器 与更低功耗电源FPGA的连接难度。共模电压的不匹配度越大,静态电流消耗就越高,不会受数据速率影响。为此,JESD204B现已成为高分辨率及高速数据转换器

与更低功耗电源FPGA的连接难度。共模电压的不匹配度越大,静态电流消耗就越高,不会受数据速率影响。为此,JESD204B现已成为高分辨率及高速数据转换器 制造商极具诱惑力的差分信号技术。

制造商极具诱惑力的差分信号技术。

除了电气规范以外,JESD204B还具有针对三种物理层的相关眼图性能要求。性能指标包括定义的眼图和总体抖动预算。光互联网络论坛(OIF)具有成熟的物理层(PHY)规范和眼图标准,JESD204B接口可利用其实现相同的串行数据速率。JESD204B链路可使用OIF低电压11 Gbit短距离规范(LV-OIF-11G-SR)允许的总体抖动最大值,即单位间隔(UI)的30%。图1是12.5 Gbps下原始JESD204B眼图及模板的示图。模板可在水平轴及垂直轴上提供确定的裕量总数。值得注意的是,12.5Gbps眼图符合LV-OIF-11G-SR规范,该规范建立在11.1 Gbps的速度基础之上,比其他的12.5 Gbps数据速率下的规范要求更严格。

2 三种PHY模式

JESD204B支持针对串行数据传输的三种PHY模式,其由LV-OIF规范定义并根据最大JESD204B通道速率分类。定义三种物理层的速率为3.125 Gbps、6.375Gbps以及12.5 Gbps,如下所示:

• 基于LV-OIF-SxI5的运行:312.5 Mbps至3.125 Gbps;

• 基于LV-OIF-6G-SR的运行:312.5 Mbps至6.375 Gbps;

• 基于LV-OIF-11G-SR的运行:312.5 Mbps至12.5 Gbps。

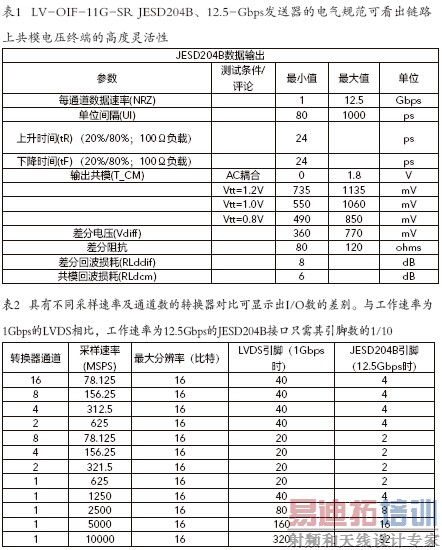

每个类别的最大及最小电气规范略有不同,以适应因所支持的广泛数据速率而导致的必要差别。表1是LV-OIF-11G-SR物理层变量的电气规范参数,其可用于12.5 Gbps的最大JESD204B数据速率。

该规范的一个优势是:与DC耦合使用案例相比,其可在链路上支持更宽泛的共模电压。这可降低有关JESD204B发送器及接收器(它们可能来自不同的厂商)的系统设计要求,因为它可根据需要提供电平移动。AC耦合数据通道的第二个优势是:可在发送器和接收器之间对共模噪声进行去耦,从而有助于缓解系统设计人员关于信号质量的顾虑。DC耦合更容易受到耦合在数据线路中的共模噪声影响。AC耦合的第三个优势是:其可降低来自多个厂商的不同发送器(Vtt)及接收器最终电压需求,从而可使接收器工作在其最佳共模电压下。这有助于JESD204B发送器与接收器在需要高度的电源电压灵活性的系统设计中以不同的最终电压运行。

此外,JESD204B接口还可针对单个链路上的多个转换器 进行数据分区。随着链路速率提升至12.5 Gbps,更多的转换器

进行数据分区。随着链路速率提升至12.5 Gbps,更多的转换器 可部署在相同的链路(对应不同变量的数据,请参见表2)上。这特别适合在单个封装中提供2个、4个、8个以及16个转换器

可部署在相同的链路(对应不同变量的数据,请参见表2)上。这特别适合在单个封装中提供2个、4个、8个以及16个转换器 的器件,同时这也是与LVDS接口相比的一大独特优势。

的器件,同时这也是与LVDS接口相比的一大独特优势。

JESD204B所提供的明确规范既支持从相同pin脚上串行发送多个转换器 综合数据。

综合数据。

LVDS可作为一个I/O结构,将一个单通道转换器 做为终点/起点进行直接输入输出,但是不能明确定义一个方法来整合整个I/O中多个转换器

做为终点/起点进行直接输入输出,但是不能明确定义一个方法来整合整个I/O中多个转换器 的数据。有了JESD204B,就有了实现从多个转换器

的数据。有了JESD204B,就有了实现从多个转换器 在相同的pin上串行发送综合数据的明确规范。每块器件数据的来源甚至不需要是真实的固定硬件转换器

在相同的pin上串行发送综合数据的明确规范。每块器件数据的来源甚至不需要是真实的固定硬件转换器 。它可来自一个“虚拟转换器

。它可来自一个“虚拟转换器 ”滤波器,该滤波器作为真实转换器

”滤波器,该滤波器作为真实转换器 的数字处理的一部分,输出一分为二,包括实数路径和复数路径。针对90度相移的IQ通信系统就可充分利用虚拟转换器

的数字处理的一部分,输出一分为二,包括实数路径和复数路径。针对90度相移的IQ通信系统就可充分利用虚拟转换器 的特性。

的特性。