- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

数字荧光示波器中随机采样技术的设计与实现

实时采样技术是普通电子测量仪器中常用的信号采集手段,其对信号数据获取的能力受到仪器中A/D模块的最高采样率的限制。为了弥补这个限制,我们采用随机采样技术,这样对于器件的选用有很大的余地,可大幅度降低制造成本。

随机采样的原理

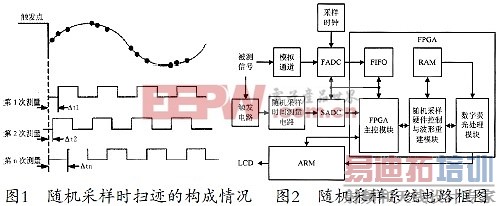

根据Nyquist采样定理,当信号的频率远远大于A/D的采样频率时,信号波形是无法重新构建的。所以对高速的信号可以采用随机采样。随机采样是通过测量每次A/D采样序列的起点和固定基准点(信号触发点)的时间差Δt,由于Δt具有随机性,所以通过对信号的n次采样,如果n足够大,通过随机采样序列的叠加就可以将信号波形恢复出来。其原理如图1所示。

由于每轮采样时,Δt是一个随机值,如果将取样周期T等分为M段,每段分别对应0~M-1间的一个值。经过若干轮采样后,就可以取遍一个采样周期T内所有的M值。在周期性输入信号的前提下,就可以用多轮采样数据序列重建出原信号波形。在图1中,M=4,需要进行四轮采样。

随机采样系统的总体设计方案

系统电路设计方案

图2为随机采样系统电路框图。被测信号经模拟通道进行衰减、放大后,由快速模数转换器(FADC)进行采样和量化,将采样后的数据送至FPGA并缓存在FIFO中。同时被测信号经触发电路后产生触发信号,经随机采样时间测量电路产生触发点与其后第一个采样脉冲之间的时间差Δt。慢速模数转换器SADC把Δt变为数字量,送至FPGA。

FPGA是系统的控制核心,通过SPI串行总线接收ARM发送的各种控制命令,对系统工作实行控制,并完成波形数据的数字荧光处理。

随机采样时,FPGA内部的控制模块根据ARM发来的控制命令对外部随机采样时间测量电路的工作进行控制,波形重建模块根据读取的值计算出对应的0~M-1间某个组数值I,并根据I值进行各组采样数据的排序,计算出对应的RAM存储地址,并将FIFO中缓存的各组采样数据按相应的地址存入RAM中。

当组数值I遍布0~M-1间所有值时,则一个完整的波形已经被重建好,波形重建模块将RAM中组好的数据送至数字荧光处理模块转换为显示波形的图像数据,数字荧光处理模块会定时将波形图像数据送至ARM显示。

整个随机采样时间测量电路的关键是对Δt的精确测量和波形数据的重组。