- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCIE3.0的发射机物理层测试

一、PCIE 3.0与 PCIE 2.0

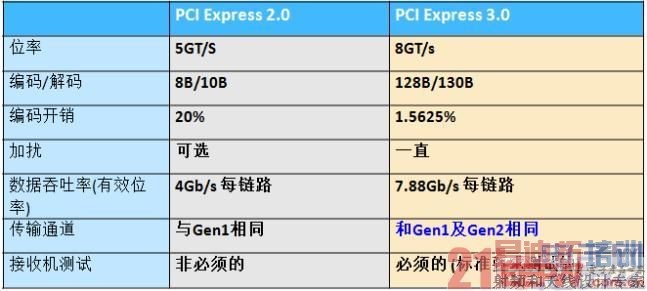

PCIE 3.0相对于它的前一代PCIE 2.0的最主要的一个区别是速率由5GT/s提升到了8GT/s。为了保证数据传输密度和直流平衡以及时钟恢复,PCIE 2.0中使用了8B/10B编码,即将每8位有效数据编码为10位数据进行传输,这样链路中将会有20%信息量是无效的,即使得链路的最大传输容量打了20%的折扣。而速率提升的目的是为了更快的传输数据,编码方式也不可或缺,因此在PCIE 3.0中还通过使用128B/130B的编码方式(无效信息量减低为1.5625%),同时使用加扰的方式(即数据流先和一个多项式异或得到一个更加随机性的数据,到接收端使用同样的多项式将其恢复出来)来实现数据传输密度和直流平衡以及时钟恢复的实现。另外一个区别是,PCIE 3.0规范已经要求接收机测试为必测项目,而PCIE 2.0是选测项目。下表所示为PCI Express 2.0与PCI Express 3.0的主要不同点的对比。

二、PCIE 3.0发射机物理层测试

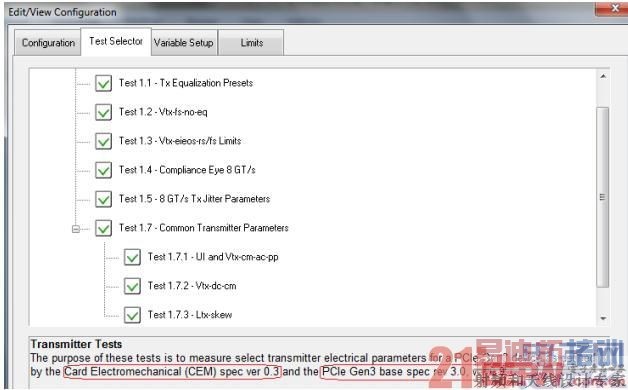

PCIE 3.0发射机测试项目,如下图(力科的一致性测试软件中包含的测试项目)所示为PCIE 3.0的CEM规范(Ver0.3)以及PCIE 3.0的基本规范(Rev3.0,Ver0.9)中规定的发射机测试项目。

1.TxEQ Preset测试(Test 1.1)

由于PCIE 3.0的速率已经达到8Gb/s,而且传输的通道往往需要经历主板至板卡,整个链路会比较长,这样就会导致高速信号比较大的损耗。为了补偿通道的损耗,确保接收端信号眼图能够张开,通过使用相应的加重(去加重或者预加重)及均衡技术是非常有必要的。因此PCIE 3.0在发送端使用了施加去加重(de-emphasis)和前冲(preshoot)功能。

由于不同的设计或者不同的产品中PCIE 3.0信号传输通道的长度是不等的,为了应对更多复杂的情况,PCIE 3.0规范中规定了发送端可实现11种等级的去加重(de-emphasis)和前冲(preshoot)功能。

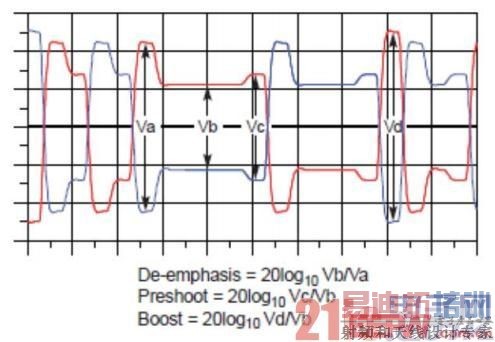

PCIE 3.0规范中对这11种等级的去加重(de-emphasis)和前冲(preshoot)功能做了规定,因此PCIE 3.0发射机测试中需要对这11种预加重和均衡进行测试,即验证发送端芯片的de-emphasis及preshoot的能力,以确保其能够满足规范的要求。如下图所示为De-emphasis Preshoot以及Boost的定义和计算方法。

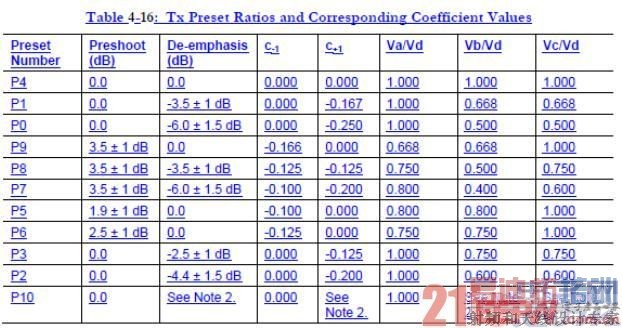

下表4-16所示为摘自PCIE 3.0规范的Preset 0到Preset 10的系数及去加重和前冲等级。 [p]

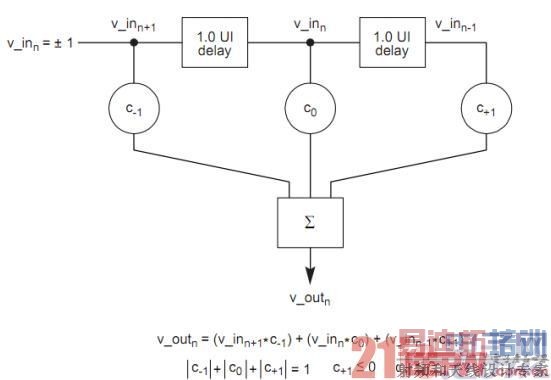

实际上,PCIE 3.0的去加重(de-emphasis)和前冲(preshoot)功能是通过一个三阶FIR滤波器实现的。

由于C-1和C+1均是小于0的,也就意味着de-emphasis和preshoot分别是作用于切换位的:及de-emphasis只有在信号的码型的当前位与前一位相比发生0电平到1电平或者1电平到0电平切换时起作用;preshoot只有在信号的码型的当前位与后一位相比发生0电平到1电平或者1电平到0电平切换时起作用;比如说,如果C-1为零,那么应该只有De-emphasis起作用;如果C+1为零,那么应该只有Preshoot起作用;如果两者同时起作用,那么将产生Boost,也即产生0电平、1电平、0电平的同时切换。

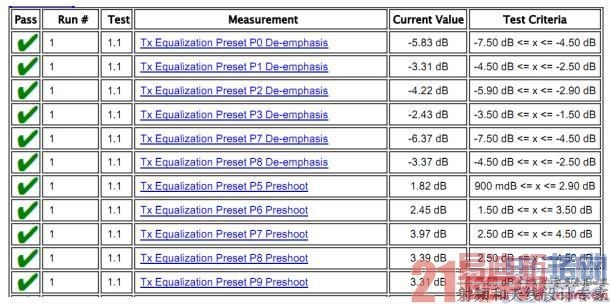

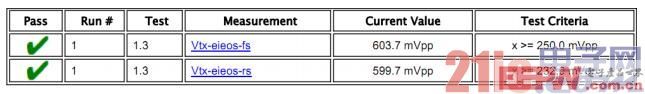

下图所示为基于力科(LeCroy)示波器及其QPHY-PCIE 3.0自动化测试软件完成的PCIE3.0的TxEQ的Preset测试结果:图中各列清晰的标出了是否通过,测试项目,当前测量值,以及规范要求值。

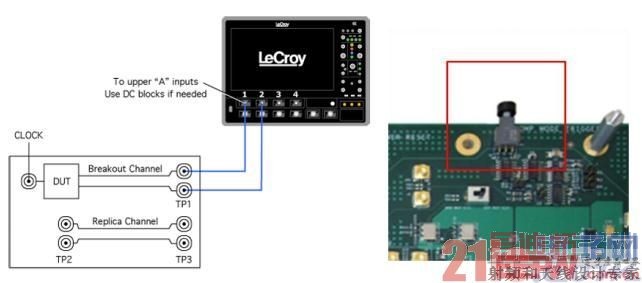

PCIE 3.0 的TxEQ的Preset测试的测试点选择在TP1,即Breakout Channel之后的转接头上,夹具上有一个按钮可用于切换Preset0-Preset10,测试时根据Qualify自动化软件的提示切换夹具上的按钮使其输出示波器测试所需要的对应信号码型,如下图所示:

PCIE 3.0的TxEQ的Preset测试的测试码型选择PCIE 3.0一致性测试码型中的第一个模块的码型,即64个连续1电平和64个连续0电平码型,并选择1电平的57-62UI区间等效1电平以及0电平的57-62UI区间等效0电平。

2、没有均衡时的发送端电压摆幅(Vtx-fs-no-eq,Test 1.2)

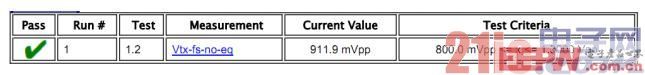

使用Preset4(de-emphasis=0,preshoot=0)时的波形进行测试,测试连接图、测试点、测试码型选择同TxEQ的Preset测试。下图为力科(LeCroy)及自动化测试软件QPHY-PCIE3.0的Vtx-fs-no-eq测试结果:

3、EIEOS序列码型的全电压摆幅和减小的电压摆幅(Vtx-eieos-rs/fs limits,Test 1.3)

EIEOS(Electrical Idle Exit Ordered Set)是用于指明电气空闲的退出(Electrical Idle Exit),具体的码型为K28.5码,为8个连1电平和8个连0电平交替重复,码型总长度为128位。 [p]

EIEOS序列的全幅电压测试(Vtx-eieos-fs)需要将Preset设为10,即最强的均衡增强(boost)情形,测试电压的摆幅。

EIEOS序列的减小的电压摆幅测试(Vtx-eieos-rs)需要将Preset设为1,即较弱的均衡设置,以验证幅度较小的EIEOS码型也同样能够被识别到。

EIEOS的测试是在Tx的管脚处测量的,因此需要考虑Breakout通道带来的衰减,即要通过去嵌的方法将Breakout通道的影响消除掉,需要事先提供Breakout的S参数。下图为力科(LeCroy)及自动化测试软件QPHY-PCIE3.0的Vtx-eieos-rs/fs limits的测试结果:

4、8GT/s一致性眼图测试(Compliance Eye 8GT/s,Test 1.4)

该项测试的目的是验证被测系统的信号眼图的眼高和眼宽等是否满足CEM规范的要求。使用的码型为128B/130B编码格式的一致性测试码型(compliance pattern)。由于Tx发送端波形有11种preset,CEM规范要求只要有一种preset码型(可选择一种最好的码型)通过即可,可以任意选择preset等于1或者7或者8的码型进行测试,如果三种preset所对应的码型都不能够通过,那么则需要继续测量余下的其它preset对应的码型,直到有通过为止,否则需要将所有的preset对应的码型都测完以确定眼图测试是否通过。规范要求示波器一次至少采集约1.5M个UIs(比特位)进行测试,如果示波器采样率设置为40GS/s,则需要采集约8M个数据点进行测试。

测试点选择在TP1,测试要求使用接收端的均衡设置,即需要打开CTLE和DFE,在力科示波器中可使用眼图医生EyedoctorII来实现CTLE和DFE均衡以及串行数据分析软件SDAIII来做眼图测试。

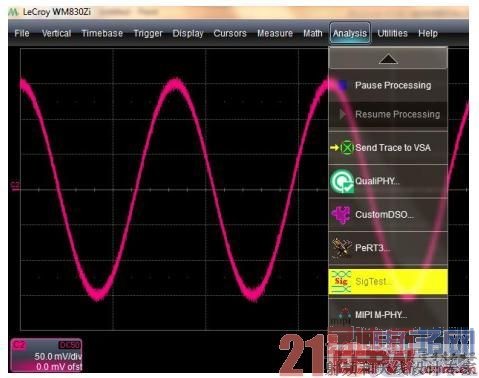

由于规范也建议使用Intel的Sigtest软件来实现CTLE、DFE以及眼图测试功能,在力科示波器已经集成了Intel的Sigtest软件,可和力科的Qualify软件一起实现所有项目的自动化测试并自动出多种格式的报告。

5、8GT/s抖动参数测试(8GT/s Tx Jitter Parameters,Test 1.5)

抖动测试是高速串行信号的必测项目。该项测试就是测量PCIE GEN3在8Gb/s时的抖动。测试码型选择最优化后的128B/130B编码格式的一致性测试码型(compliance pattern)。测试点选择在TP1,Breakout通道的影响需要消除掉(De-embedding);测试时需要所有通道都有输出;对Breakout通道进行去嵌时,需要设置截止带宽在8GHz-12GHz范围内(或者限制最大的boost值),因为去嵌可能会放大噪声。

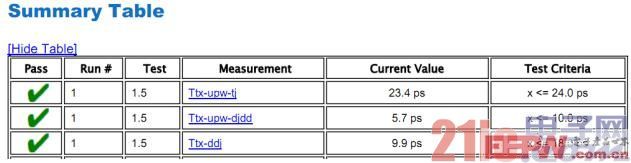

PCIE GEN3需要测试抖动参数有:

Ttx-ddj:最大数据相关性抖动减去最小数据相关性抖动的绝对值,DDJ(max)-DDJ(min);Ttx-utj:数据不相关的总体抖动,基于Q-Scale曲线定义得到。

Ttx-udjdd:数据不相关的固有抖动,基于Q-Scale曲线定义得到。

Ttx-upw-tj:数据不相关的总体脉冲宽度抖动。

Ttx-upw-djdd:数据不相关的固有脉冲宽度抖动。

上述抖动参数的详细定义可参考:PCI_Express_Base_r3.0的4.3.3.10.5-4.3.3.10.7.如下图为力科示波器测得结果:

6、8GT/s发送端信号通用参数测试(UI,Vtx-cm-ac-pp,Vtx-dc-cm,Ltx-Skew,Test 1.7)

该项目测试为发送端信号的通用参数测试,一个是UI即位率测试,该项测试需要将SSC关闭;另外两个分别是Vtx-cm-ac-pp,即两个差分信号之和的一半的峰峰值, Vtx-dc-cm,即直流共模电压,这两个参数需要测试数据量至少1M个UI,测试位置选择在Tx端芯片管脚上,可通过在TP1位置测试,对Breakout通道进行去嵌达到;Ltx-Skew为一个link中的两个链路之间的时间偏移。如下图为力科示波器测试结果。

上一篇:涡轮流量计特点及结构分类

下一篇:超声波流量计的七大优点