- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR测试--SDRAM时钟分析案例

前个周末接到了一个朋友的电话,询问我如果内存有问题,需要测试哪些项目?对于这个很常见的问题,我习惯性的回答他先测量内存时钟和读写时序看看,然后结束了通话。没过一会,我那朋友又打过来,告诉我他遇到一个怪事,他用探头点测内存时钟时,系统的程序不卡了,可以顺利启动并运行。听到这个描述,我顿时感兴趣了,开始仔细询问待测试的电路和测试仪器。

待测试的电路板的内存控制器为A公司的ARM架构的MCU,内存为Micron的SDRAM,内存时钟频率为100MHz,测试仪器为某200M带宽示波器,探头为示波器标配的无源探头。在以往的探头培训中,我曾多次给客户讲探头的重要性,在我的幻灯片中有以下几句话:

在把探头连接到电路上时,可能会发生下面三种情况:

1. 您可以把实际波形形状传送到示波器屏幕上。

2. 探头可能会改变波形形状,您会在示波器上观察到不同形状的信号。

3. 您可能会改变被测设备的运行(良好的设备可能会开始不能正确运行,或反之)

显然,今天我这位朋友遇到的情况正好满足第三种的最后三个字,即探头使运行异常的设备变正常了。如果这样的情况能经常发生,想必每位加班debug电路的工程师都可以不再苦恼,只需一个合适的探头就可以找到问题原因并解决问题了。

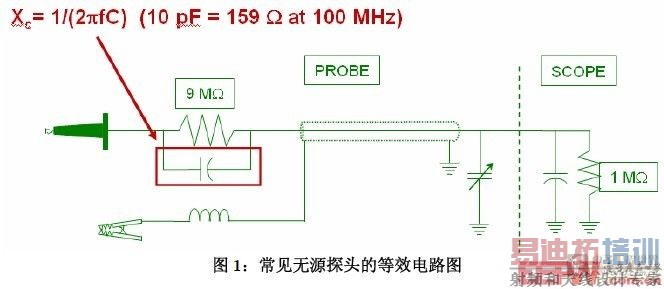

从无源探头的原理来看,如图1所示为常见的无源探头的简化电路图,通常示波器标配的无源探头的直流输入电阻为10兆欧(探头的9兆欧与示波器前端1兆欧串联),输入电容为10pf左右,与9兆欧电阻并联。当待测试信号的频率较高时,容抗随着频率升高而减小,所以无源探头整体的输入阻抗变小,当频率为100MHz时,输入阻抗为159欧。

回到和朋友的对话,既然无源探头在100MHz时等效于100多欧的电阻,于是我建议他找个100欧的电阻并联端接到内存芯片的时钟上,即时钟信号接100欧电阻到地。十多分钟后,朋友告诉我并联100欧电阻后系统正常工作了,可以结束加班了。不过从示波器仅有的200MHz带宽来看,是根本无法准确测量100MHz的时钟信号的,所以,我们约定几天后把电路板带到力科深圳的实验室用更高带宽的示波器进行测量,这样可以准确分析端接电阻前后的时钟波形。 [p]

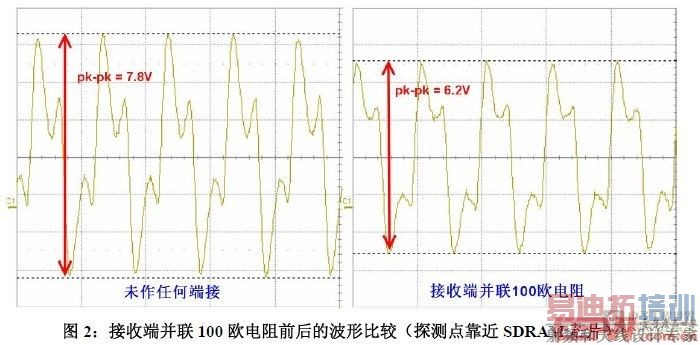

几天后,我们在实验室重新测试了该系统的时钟,测试仪器为SDA816Zi(带宽16G,采样率40G),探头为ZS1500(带宽1.5GHz)。由于待测试信号频率仅为100MHz,所以通常1G以上示波器和探头足以满足需求(注:对于某些上升时间很快的时钟,比如PCIExpress的100MHz时钟,1GHz的带宽是不够的,需要更高带宽的示波器)。下图2左图为未作端接时在SDRAM芯片端测量时钟波形,右图为靠近SDRAM颗粒并联100欧电阻后的波形,两者相比,前者的过冲高达7.8V,电路板不能正常工作;而后者过冲较小,电路板可以正常工作。

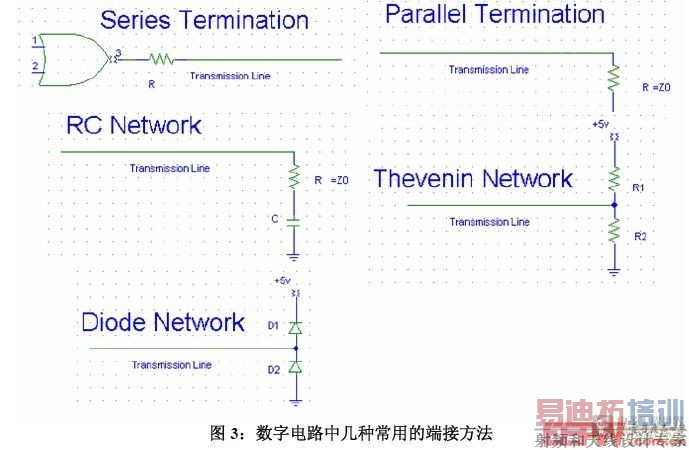

尽管并联了100欧电阻后电路板能正常工作了,但是接收端测量到的峰峰值高达6.2V,对于SDRAM芯片3.3V的工作电压来讲还是比较大的,长期工作可能会导致内存芯片出问题,所以,我们还需改进端接策略。在信号完整性书籍中,通常有串联匹配、并联匹配、RC网络、戴维南网络等端接方法,如下图3所示。相比并联匹配,串联匹配不用提供DC电流到地或者电源,不会对输出的高低电平产生影响,能减小过冲和EMI,所以我们接着尝试串联匹配下的信号质量。

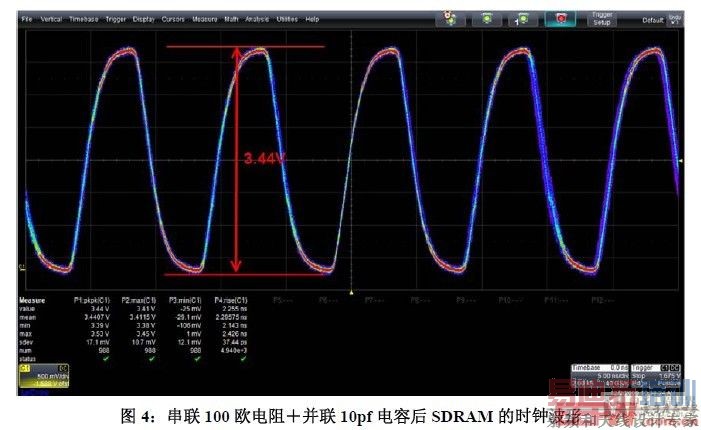

由于电路中ARM的MCU输出的一路100MHz时钟要驱动两个SDRAM芯片,布线上MCU出来的时钟刚出来就分成两路后连向两个SDRAM的时钟引脚,所以我们采用了在两路时钟分支上同时串联100欧电阻加并联10pf电容的端接方法。在PCB上割线,焊上电阻和电容后测量的结果如下图4所示,改进后的时钟峰峰值为3.44V,波形无过冲,信号质量良好。电路板系统运行正常。 [p]

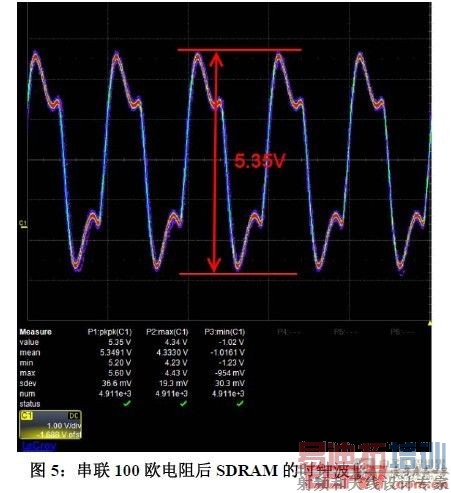

下图5所示为只串联100欧电阻时测量到的波形,信号有过冲,峰峰值为5.35V,偏大,对比图4的端接方法,串联电阻加上并联电容是较好的解决方法。

总结:在这个案例中,我们得到的以下经验:

1、串联匹配是较好的SDRAM的时钟端接策略,在原理图设计中,需要加上串联的电阻和并联的电容,如果MCU输出的时钟驱动能力弱,可以不使用并联的电容或者换用较小的电阻。

2、准确的测量内存时钟需要足够带宽的示波器和探头,无源探头在高频时阻抗太小,不能准确的测量波形,需要使用高带宽的有源探头。