- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速互联链路中参考时钟的抖动分析与测量

高速互联链路介绍

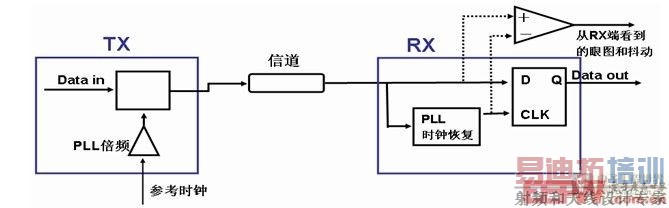

任何一个通信链路都包含三个部分:发送器(TX)、媒质(信道)、接收器(RX)。对于高速的串行互联链路也包含这三个部分,如下图1所示为一个典型的高速互联链路的结构图。其中发送器包括了:并行转换串行、编码(比如8b10b编码)、发送信号优化(如预加重)、发送驱动等功能。接收器包括了:时钟恢复、数据恢复、接收信号优化(如均衡)、串行转化并行、解码等功能。传输通道则由印刷电路板的走线、过孔、连接器、插卡的金手指、电缆、光纤等组成。

从整个链路的组成来看,发送器参考时钟的抖动在串并转换时就引入到整个链路中,影响着TX端发送出的数据的抖动,而接收器要从这些数据中恢复出时钟来进行后续的处理。可以看出发送器参考时钟的性能对整个链路的性能起到很关键的作用。本文从时钟抖动的相关概念、测试实例、测试注意事项、测试难点几方面对时钟抖动测试进行分析和探讨。

图1:串行互联链路的结构示意图

三种时钟抖动的定义,峰峰值与有效值

时钟抖动通常分为时间间隔误差(Time Interval Error,简称TIE),周期抖动(Period Jitter)和相邻周期抖动(cycle to cycle jitter)三种抖动。

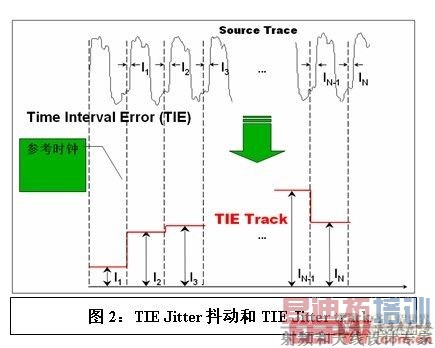

TIE又称为phase jitter,是信号在电平转换时,其边沿与理想时间位置的偏移量。理想时间位置可以从待测试时钟中恢复,或来自于其他参考时钟。如图2所示TIE抖动的示意图,I1、I2、I3、In-1、In是时钟第一个到第n个上升沿与理想时间位置的偏差,将I1、I2到In进行数理统计,在所有样本的找出最大值和最小值,两者相减可以得到TIE抖动的峰峰值,即:

![]()

假设N为测量的样本总数,抖动的平均值可表示为:

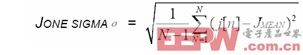

抖动的有效值(即RMS值)为所有样本的1个Sigma值,即:

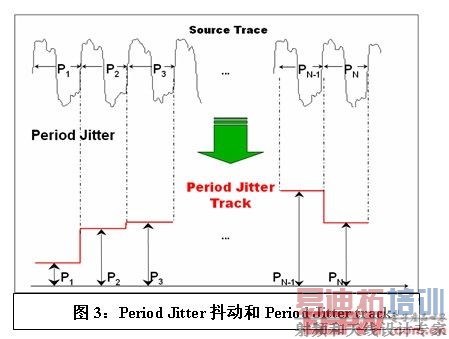

周期抖动(Period Jitter)是多个周期内对时钟周期的变化进行统计与测量的结果。如图3所示的P1、P2、Pn-1、Pn为多个周期内时钟的周期数值,对这些数值进行数理统计,同理,与TIE抖动的峰峰值和有效值计算方法相同,把P1到Pn中的最大值减去最小值,得到周期抖动的峰峰值,把P1到Pn进行1个Sigma运算,得到周期抖动的RMS值。 [p]

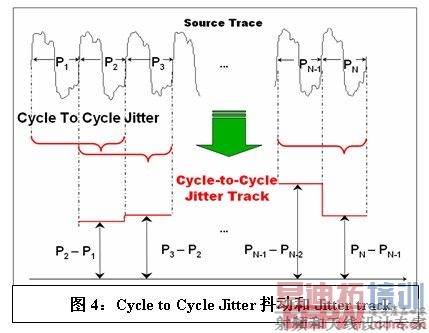

相邻周期抖动(Cycle to cycle jitter)是时钟相邻周期的周期差值进行统计与测量的结果。如图4所示,后一时钟周期减去前一时钟后作为统计的样本,C1=P2-P1, C2=P3-P2, Cn-1 = Pn - Pn-1,把C1到Cn-1进行数理统计,同理,可以计算出Cycle to cycle jitter的峰峰值和RMS值。

在上述三种常见的时钟抖动中,对于串行总线,通常是测量TIE抖动,比如高速收发器TX端的参考时钟。对于并行电路,通常是测量其时钟的周期抖动和相邻周期抖动,比如DDR SDRAM、PC主板上的FSB等等。

在图2、图3、图4中的红色曲线横轴是时间,纵轴是对应周期的抖动数值,该曲线反映了抖动随时间变化的趋势,称为抖动跟踪(Jitter track);将每个周期的抖动值(比如TIE抖动的I1、I2…In)作统计直方图,可以得到抖动直方图(Jitter Histogram);将抖动跟踪做快速傅立叶变换(FFT)计算可以得到抖动频谱(Jitter Spectrum)。

抖动跟踪是抖动在时域的表现形式,抖动频谱是抖动在频域的表现形式,抖动直方图是抖动在统计域的表现形式。各种测试仪器和分析软件对于抖动的测量和分析都是在这三个域中实现的。

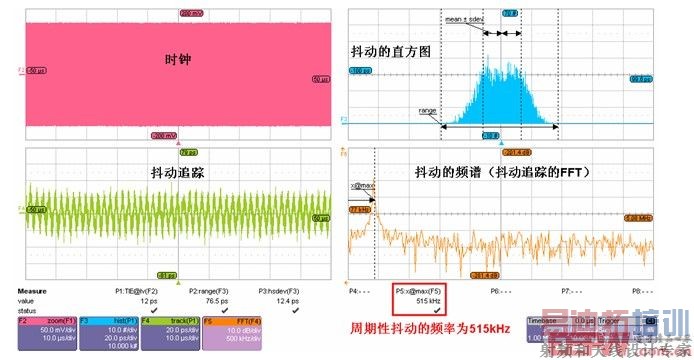

如下图5为某100MHz时钟在时域、频域、统计域分析其TIE抖动的示意图。左上角的F2为某100MHz时钟,P1是时钟的TIE参数测量;右上角的F3是TIE抖动的直方图,直方图不是高斯分布,可见时钟存在固有抖动。 [p]

图5:时钟抖动在时域、频谱、统计域的分析

左下角的F4为TIE track(即TIE抖动随时间变化的趋势),从TIE Track中可以看到周期性的变化趋势;右下角的F5是F4的FFT运算,即抖动的频谱,频谱的峰值频率为515kHz,说明该时钟的周期性抖动(PJ)的主要来源为515kHz,找到频点后,可以查找电路板上主频或谐波为该频率的芯片和PCB走线,进一步调试与分析。 [p]

时钟抖动的分解

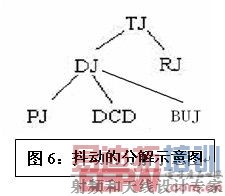

时钟抖动的峰峰值和RMS值仅反映了抖动在统计上的数值,并没有分析抖动的来源。对于时钟抖动分解,业内通常把抖动分解为:总体抖动 (TJ)、确定性抖动(DJ)、随机抖动(RJ)、周期性抖动(PJ)、占空比失真(DCD)等等。如下图6所示为各种抖动的关系图。

TJ及其各种成分,都是针对TIE的。如前文所说,TIE反映了被测时钟与理想时钟的偏差。TIE抖动的峰峰值为随着测试样本数的增加不断增大(随机抖动因素引起的),TJ是和误码率联系起来的,通常误码率为10E-12,即通常所说的TJ是10的12次方个样本的TIE抖动的峰峰值。TJ包括了RJ和DJ,而DJ包括了PJ、DCD、BUJ(其它有界的数据不相关性抖动)。对于单边沿来同步与定时的时钟,DCD不算做抖动(当然,绝大多数时钟都只用其上升沿)。

RJ会随着样本数的增多不断增大,其直方图满足高斯分布,通常用其统计后的1个Sigma或RMS值来表示,在抖动测试仪器中得到的RJ通常为RMS值。随机抖动的来源为热噪声、Shot Noise和Flick Noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL工艺的PLL比TTL和CMOS工艺的PLL有更小的随机抖动。

DJ是有边界的、确定性的抖动,来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB布局和布线。

在抖动频谱中,RJ是频谱的基底部分,而DJ是抖动频谱中的尖峰部分。很多测试仪器都是从抖动频谱来分解抖动的。

时钟抖动测试注意事项

在时钟抖动测试中,有以下要点:

选择合适带宽:为了准确测量到时钟的边沿,通常,示波器的带宽在时钟频率的5倍以上,对于某些边沿很快的时钟,甚至需要仪器带宽大于10倍时钟主频。

选择合适测试点:由于时钟链路可能使用了各种端接策略或者星形拓扑结构,在发送端探测时钟可能没有太大的参考意义,通常是在时钟链路的靠近接收端处探测和分析。

保证地线尽量短:探头的地线较长时,引入的寄生电感可能导致测量到的波形失真,较长的地线构成的信号环路也更容易受到电磁干扰。

信号幅度尽量占满整个屏幕:示波器的ADC只有8个比特的分辨率,必须让信号幅度尽量占满示波器的整个屏幕才可以保证足够的测试精度。

固定到合适的采样率:使用合适的采样率,保证在时钟的边沿采集到足够的采样点。

抓取足够的时钟周期:对于有较低频率的PJ的时钟,需要捕获足够长的时间才能找到该时钟的抖动来源。

时钟抖动评估中的难点

在目前通信设备的时钟的测试分析中,存在的问题为:芯片、设备、测试仪器厂商对时钟抖动指标的含义定义不一致。比如有的芯片厂商直接给出抖动的pk-pk值,而没有指明是那种抖动要求。芯片厂商给出的名称与测试仪器厂商的名称一致,但实际描述的含义却不一致。

有的芯片厂商对时钟抖动指标要求不严谨;有的芯片厂商给出的时钟抖动的指标要求比较随意,指标的给出没有相应的根据。这些原因在于近十年来电子产品的运行速度和时钟频率不断增加,而抖动的知识也在不断完善与理论化,而某些芯片厂商的文档对于抖动的定义不规范,给时钟性能的评估带来一定的困难,这些需要各自的积累来进行评估。

结语

高速链路是各电子设备以后重要的组成部分,其设计、性能分析和评估都是热门的话题。本文仅对时钟抖动的基本概念和测试进行相关的探讨,而抖动各成分的分离技术、时钟抖动在时域和频域表现及他们的关系、抖动的来源、抖动的改善、抖动在不同应用场景下对系统的影响都是电路设计与测试工程师需要深入研究的内容。

参考文献

《jitter slides》----力科

《Jitter, Noise, and Signal Integrity at High-Speed》---Mike Peng Li

上一篇:最新的高速信号虚拟探测和均衡技术

下一篇:虚拟雷达信号分析仪设计方法研究