- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

SPI总线测试和分析

1、SPI总线简介

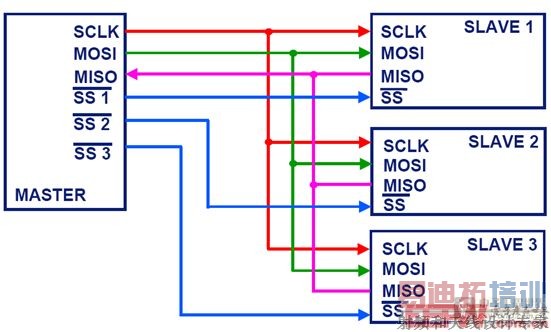

SPI(Serial Peripheral Interface--串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息,20世纪80年代由Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCLK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。其主要特点包括:可以同时发出和接受串行数据;可以作为主机或丛机工作;发送结束中断标志;写冲突保护;总线竞争保护。图1是 SPI总线架构示意图。

图1 SPI 总线架构

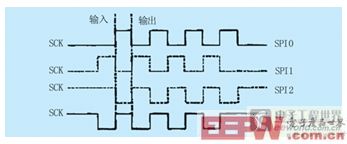

SPI是一个环形总线结构,由SS(CS)、SCK、SDI、SDO组成,在主设备和从设备之间双向传输,实现发送和接收数据,最高速率可达5Mbps。由SS(CS)信号来选定与主设备通信的从设备,所以在某时间点内主设备与从设备之间可实现点对点通信,其好处是不需要进行寻址操作。SPI共有4种工作模式,SP0、SP1、SP2、SP3,其中比较常用的是SP0、SP3。SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设时钟相位和极性应该一致。图2是SPI 总线4种工作模式时的SCK示意。

图2 SPI总线4种工作模式示意

SPI是一个环形总线结构,其主要工作时序是在SCK的控制下,两个双向移位寄存器进行数据交换。

假设下面的8位寄存器装的是待发送的数据10101010,上升沿发送、下降沿接收、高位先发送。

那么第一个上升沿来的时候 数据将会是sdo=1;寄存器=0101010x。下降沿到来的时候,sdi上的电平将锁存到寄存器中去,那么这时寄存器=0101010sdi,这样在8个时钟脉冲以后,两个寄存器的内容互相交换一次。这样就完成里一个spi时序。

例子:

假设主机和从机初始化就绪:并且主机的sbuff=0xaa,从机的sbuff=0x55,下面将分步对spi的8个时钟周期的数据情况演示一遍:假设上升沿发送数据

脉冲 主机sbuff 从机sbuff sdi sdo

0 10101010 01010101 0 0

1上 0101010x 1010101x 0 1

1下 01010100 10101011 0 1

2上 1010100x 0101011x 1 0

2下 10101001 01010110 1 0

3上 0101001x 1010110x 0 1

3下 01010010 10101101 0 1

4上 1010010x 0101101x 1 0

4下 10100101 01011010 1 0

5上 0100101x 1011010x 0 1

5下 01001010 10110101 0 1

6上 1001010x 0110101x 1 0

6下 10010101 01101010 1 0

7上 0010101x 1101010x 0 1

7下 00101010 11010101 0 1

8上 0101010x 1010101x 1 0

8下 01010101 10101010 1 0

这样就完成了两个寄存器8位的交换,上面的上表示上升沿、下表示下降沿,sdi、sdo相对于主机而言的。其中ss引脚作为主机的时候,从机可以把它拉低选为从机,作为从机的是时候,可以作为片选脚用。根据以上分析,一个完整的传送周期是16位,即两个字节,因为,首先主机要发送命令过去,然后从机根据主机的名准备数据,主机在下一个8位时钟周期才把数据读回来 [p]

2、SPI总线测试的需求

工程师对SPI总线测试和分析的需求主要涵盖以下三个方面:

2.1 了解总线正在发生什么

软件工程师设计了SPI主设备发出的消息内容,但硬件工程师需要确定消息是不是被准确无误的传送到物理线路上,需要了解总线上真正在发生什么。传统的使用示波器的方式是先用探头把信号捕获下来,然后根据电平特点转换成“1”或“0”,然后再去对比SPI协议,将其还原成有意义的消息帧。这种方式费时费力,对工程师的业务能力要求很高,而且仪器使用效率很低。工程师需要仪器能提供一种自动化的方式,直接将采集到的波形翻译成容易识别的内容,再根据不用类别工程师的需求,以不同的方式动态显示在仪器屏幕上。比如硬件工程师可能希望以二进制的方式查看SPI消息内容 ,底层驱动工程师希望以16进制方式分析波形,而应用软件工程师则希望以ASCII文本的方式去了解总线上实际运行的数据内容。

2.2 调试总线上有故障的节点

SPI设备可以实现一对多的连接,即一个主设备连接多个从设备,通过片选信号(SS/CS)来选择需要操作的从设备。当主设备切换传输对象的时候,我们需要关注总线所发送的信息是否与所选择的从设备一致。有可能出现所发送的信息与当前所选择的从设备并不一致的状况。

2.3 分析EEPROM或者Falsh内存单元的有效性

EERPOM/Falsh是在各类系统单板上广泛使用的存储器件,主要作用是保存系统上电时需要导入的信息,比如主内存地址、容量、模式,各种设备初始化状态、部分系统信息等,EEPROM/Falsh器件大多通过SPI总线传递数据。当读写EEPROM/Falsh配置信息出错的情况下,我们就不仅仅需要知道是哪片EEPROM出问题,更有意义的是要深入到器件内部,定位具体是哪个地址单元出了问题,是读数据过程中有问题还是写数据过程中有问题。

3、力科示波器充分满足工程师测试SPI总线的需求

广大工程师用户日益需要能处理各种通用测量任务、同时又能满足分析 SPI总线等低速串行总线的专用需求、且符合有限预算的解决方案,力科基于Windows操作系统的全系列示波器产品满足了这些需求,这些系列包括WaveSurfer Xs、WaveRunner Xi、WavePro 7Zi和WaveMaster 8Zi,这些产品一个很重要的的应用方面就是调试串行总线。示波器不仅要能测量信号电平、频率等常规项目,还要能提供专门的软件包以更深入分析和调试SPI总线。

力科 SPI测试软件包的总线协议触发功能和总线协议解码功能,能够帮助工程完成设备调试:

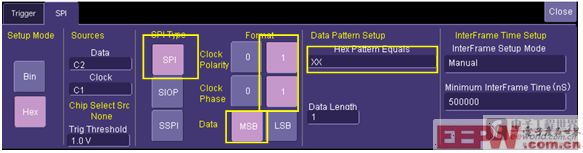

3、1 总线协议触发

在力科示波器界面下进入菜单项“Trigger”->”Serial Data”->”SPI”,弹出的界面中允许用户按照特定的模式去触发SPI消息帧,如下图3所示。你可以根据自己的需求选择不同的数据对总线进行触发。可以选择对SPI总线标准下的某一子集(SPI、SIOP、SSPI)做触发。可以设置时钟的相位和极性,及数据的高位或者低位触发。可以输入需要触发的数据是多少,且数据的位数是可以调整的。也可以选择以2进制还是16进制做为触发的数据格式。

通过总线触发,我们可以对总线所传输的信息和可能出现的错误做分析和调试

图3 力科示波器 SPI软件包设置触发界面

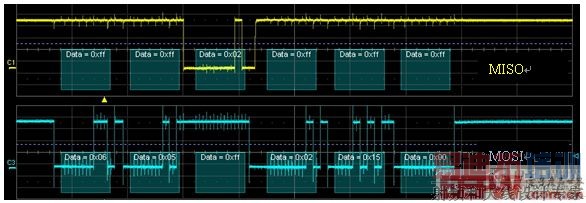

3、2 总线协议解码

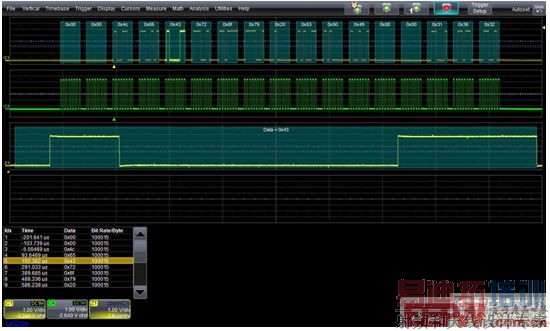

在力科示波器界面下进入菜单项“Analysis”->”Serial Decode”->”SPI”,用户对总线正在传输的数据内容进行实时解码,解码后的内容能选择以“二进制”、“十六进制”和“ASCII”三种方式直接显示在波形上方。例如图4中的信息,MOSI上的第二个0x05,表示RDSR,查看读状态寄存器,MISO上随即返回0x02,表示该设备是可写的,且处于空闲状态。

通过对捕获到的总线协议做解码,我们可以直观的看到总线上传输的数据是否是工程师实际上发送和接收所要求的数据,从而帮助调试。

图4 SPI总线解码

除了可以直接在波形上显示解码结果以外,力科还提供了列表显示解码结果。例如图5中的信息,列表显示了解码后该字段的相关信息,可以通过点击列表的某一行来放大该段数据以观察波形细节。

图5 SPI列表显示及放大

上一篇:测试、测量和仪表的“绿色”之路

下一篇:直方

在抖动分析中的应用