- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

深入浅出谈高速串行信号测试(一)

记得大概在6 年前,随便翻阅一本计算机相关杂志,看到一则硬盘的广告,什么品牌记不得了,印象最深的就是它所宣传的新技术- 串行总线。当时我还没有接触高速数字电路方面的知识,脑子里还是传统的教科书式的关于数字电路的概念:串行,或是异步串行总线,无外乎RS232 、RS485 等。居然串行构架的传输效率高过于并行的系统,简直无法想象。回头看看这几年市场热点和技术革新,在对照自己第一次接触“串行”时的愕然,不禁莞尔。

这篇小文章就是自己对关于高速串行数字电路设计、测试的知识体系的一个梳理。特别是在加入Tektronix 之后,负责HSSD (High Speed Serial data )测试产品的支持,从日常接触的客户中,了解到很多具体的应用和实例,在一定程度上讲,Tektronix 就像小蜜蜂一样,在不同的客户中间,传播着HSSD 设计、测试的理念和经验。这篇小东西包含了涉及HSSD 各个方面的内容,有谈到基本的原理、测试的方法、时下比较流行的技术,以及常见的故障信号以及解决方案。希望这篇小东西能在日常繁琐的工作之余,作为一盘“小甜点”,给大家带来内心那一份久违的、轻松愉悦的微笑。

一、高速串行总线基本知识

并行总线之所以在高速传输上被串行总线取代的原因就在于:第一,系统时钟的瓶颈;第二,总线间的串扰。要达到上Gbps的传输速率,对于并行总线而言,势必时钟频率要达到GHz,就算是使用DDR方式,其系统时钟频率之高,在板级分布之困难,使得我们望而却步。而动辄几十条走线等长的排布,可控的串扰,几乎也是不可能完成的任务,而不断增加的时钟频率,又对等长走线要求越来越严格,并行总线的瓶颈似乎变得非常的突出。

串行总线没有时钟。或是说在串行总线收发两端,不需要同步时钟。这是串行总线最突出的一个特点。这是这个特点,一举将并行构架的瓶颈打破,数据速率可谓突飞猛进!最新在PC行业的动向是8Gbps的PCIE Gen3。而在通信行业,超过10Gbps的串行总线早已在使用了。

对于高速串行系统的验证与测试和传统的信号测试有自己特殊的之处,传统信号测试关心信号的模拟特征,包括时序和幅度方面特性的考察。对于并行总线而言,时序的方面的测量最主要以建立/保持时间为主,为了满足接收端能否正确的锁存数据,数据和时钟的时序必须满足建立/保持时间的要求,否则会产生误码。对于高速串行系统而言,测试的目的也是为了验证系统是否满足设计要求的误码水平。并行和串行的差别就在于发送端和接收端对数据锁存的处理和时钟的传输上的差异。串行系统在发送断通过串行发送器将数据按照Tx clk的节拍发送到总线上,在接收端必须能够从数据中恢复出时钟,并且用该时钟锁存数据,进行解码。在串行系统中,我们不再关心时钟和数据信号之间的时序,而是关心在发送端是否能否严格按照时钟节拍发送数据;在接收端能否恢复出时钟;在互连层面关心传输线对信号完整性,特别是抖动的影响。

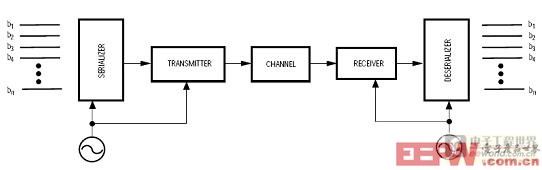

图表 1典型的串行系统

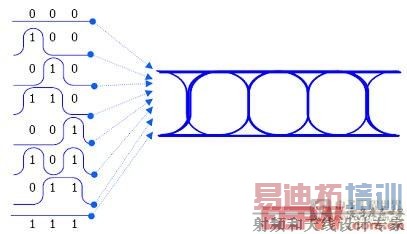

那么如何去定量串行系统的性能呢?在高速串行系统中,主要通过眼图测试。眼图是把连续的比特流按照某一特定的时钟,分割为单独的比特,而后叠加而形成的图形,类似一个张开的眼睛,故得名眼图(Eye-diagram)。

图表 2眼图的形成

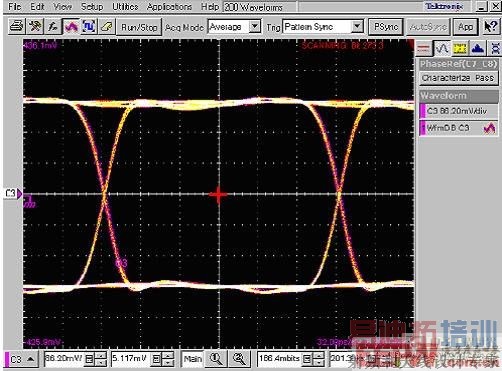

眼图是高速串行信号的宏观的信号质量的体现,在眼图中能直接反映出信号串行信号的幅度(如眼高、过冲、噪声等)和时序(如上升/下降时间、UI长度、眼宽、抖动等)特性。在接收端,理想的时钟判决应该发生在整个眼图的中间,这样才能保证系统有最好的误码特性。

图表 3理想的采样时刻-中间的红色十字

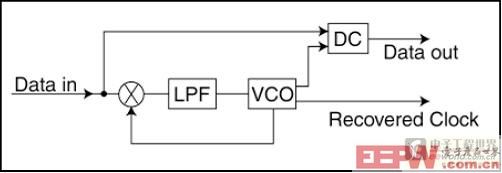

接收端是如何恢复出嵌入在串行数据中的时钟呢?是通过接收端的时钟数据恢复(CDR)来完成的。CDR的实现可以有很多中方式,通常使用锁相环(PLL)或者鉴相器(PI)来完成。PLL类型的CDR通过数据中0-1的跳变来锁定时钟相位和频率,在一定的范围内能够跟踪数据信号的抖动,以保持时钟和数据相位的一致,而后通过判决电路(DC)得到数据。PLL类型的CDR要求数据中有足够多的0-1跳变,而且数据必须是直流平衡的,因此在数据进入到串行发送器之前,会通过8B/10B编码,使得数据有足够多的跳变,并且保证一段数据流中0和1的个数相同。

图表 4 PLL类型的CDR电路

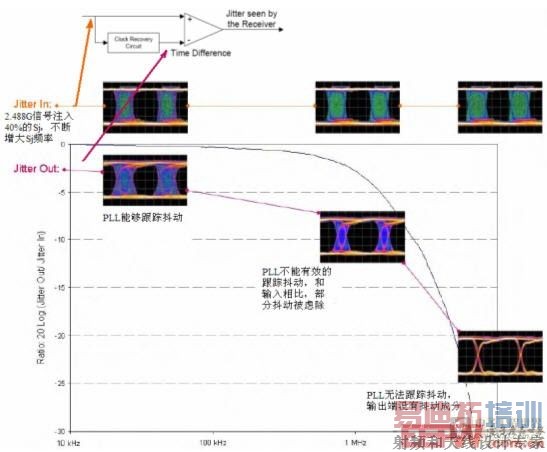

CDR的目的很明确,跟踪数据抖动的变化(产生和数据同步的抖动),保证在DC中不会出现误码。CDR对数据的跟踪也不是万能的,如果数据中的抖动频率超过了PLL的环路带宽,那么PLL是无法跟踪的,数据抖动就会传递到DC中,可能会影响到数据的提取而产生误码。所以CDR的时钟恢复是有范围的,这个范围是有PLL的环路带宽决定的。在环路带宽能的抖动成分能被跟踪,而超出带宽的抖动是真正影响到误码率性能的抖动,我们所要考察的串行系统的抖动,就是那些不能被PLL跟踪的抖动!所以,在眼图测试中,必须要给定CDR的类型,否则盲目的测试眼图和抖动是没有任何意义的。

图表 5抖动测试目的是发现在接收端无法被跟踪的抖动

明确的眼图测试的目的和注意事项后,我们就可以根据被测系统规划合适的测试方案:

- 通过系统的串行速率选择合适带宽的示波器

- 根据串行系统的误码标准,制定眼图模板

- 设计测试使用的CDR模型,正确模拟接收端的抖动情况

- 选择合适的测试项目,明确测试目的是以验证为主还是调试为主

在测试工具的选择上,工程师并不是只有实时示波器一种选择。能够进行高速串行系统功能验证和调试的工具大致有:实时示波器(Real Time Oscilloscope)、采样示波器(Sampling Oscilloscope)、时间间隔分析仪(Time Interval Analyzer)、误码仪(Bit Error Rate Tester)。按照测试精度、调试能力、效率以及成本作为考察项目,将上述几种测试设备做简单的对比:

| 测试精度 | 调试能力 | 效率 | 成本 | |

|---|---|---|---|---|

| 实时示波器 | 中 | 强 | 高 | 低 |

| 采样示波器 | 高 | 中 | 高 | 低 |

| 时间间隔分析仪 | 高 | 无 | 中 | 高 |

| 误码仪 | 高 | 无 | 低 | 高 |

图表 6各种测试仪器对比

在测试精度方面,采样示波器较实时示波器占有一定优势,时基精度可达200fs,垂直14bitADC,动态范围大,自身噪底低(具体指标请参见文档2)。因此采样示波器除了分析抖动外,同时还可以分析噪声对串行系统误码的影响。但是采样示波器采必须需要外触发,只能观察周期性、重复的波形,不具备实时示波器灵活的触发功能,因此在调试能力方面,实时示波器是其中最强大的。例如Tektronix DSA系列示波器中的串行触发,可以触发到数据流中特定的比特码型;码型锁定功能可以很容易的浏览码型中所有比特;硬件CDR能够快速的同步数据,进行眼图、抖动分析。而误码仪是专用的误码测试设备,其测试精度是最高的。误码仪是一个闭环的系统,通过对比发送和接收到的数据来计算误码。但是误码仪测试的效率很低,如果要测试置信概率为95%的误码率小于1E-12的话,要至少保证在连续的3E+12个比特中没有误码。如果该串行速据的速度为1Gbps,那么3E+12个比特意味着要测试3000秒才能得到结果,而且这是最乐观的估算。时间间隔分析仪是专用的测试时间间隔的仪器,时间测试精度高,但是设备本身带宽有效,100MHz带宽的时间价格分析仪非常的昂贵。因此,综合比较下来,实时示波器的综合能力在所有抖动分析测试工具里面是最强的。