- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用时钟裕度技术早期故障预测

计算机领域的超频技术已存在多年,其目的就是有意识地让系统超越工作极限,实现最大性能,但这通常会减少设备的使用寿命且难以保证系统的稳定性。许多系统设计人员都认为超频技术除了影响系统稳定性之外一文不值,但实际它也有一些潜在的好处:可以为我们确定实际系统总时序预算(TTB)裕度以及估算产品现场使用寿命提供有益信息。超频技术正在发展为一种称为“时钟裕度”的新技术,该技术可确保系统稳定运行。此外,本文还将探讨如何利用可编程时钟源来实现时钟裕度技术,确保在临界条件下的真正系统稳定性。

很多读者对上世纪80年代和90年代初期的PC平台可能记忆犹新,这种平台都带有一个所谓加速模式(turbo mode)按键。我喜欢按下加速模式按键,并观察显示数字的变化。可这些数字到底意味着什么呢?按下这个按键,首先是自我感觉良好,认为自己正在体验一种极限计算性能,可谓物超所值,毕竟当年的一部台式机价值2500美元。我也很清楚,要是觉得加速模式下性能不稳定,那么总可以返回正常模式,以确保整个系统的稳定性。坦率地说,实际上我从未在正常模式下工作过,相信其他人也一样。当然,加速模式是一柄双刃剑,人们一直批评它会造成系统崩溃,而且还会担心一旦风扇失灵,就会把CPU烧坏报废掉。

实际上,过去的加速模式就是我们今天所说的超频技术。其实基本概念并没变,都是要接近或超越系统的计算速度极限,将系统推到稳定与不稳定的边缘。想到超频技术时,总是自然而然地想到PC。除了超频技术带来的问题之外,能不能通过超频技术(即以超频为工具)找到系统的弱点呢?能不能通过一种结构化的“试验设计”,让逻辑中最薄弱的一环自动暴露出来呢?能不能通过超频技术来准确判断系统稳定与不稳定的确切临界点呢?我们的分析还会不会提供一些隐性的有价值信息,有助于推测系统老化影响带来的早期故障问题?如果认为超频的好处是让系统达到稳定工作的极限,那么降频又会怎么样呢?通常认为超频主要就是修改设置时间,而降频就是修改保存时间。要讨论超频或降频,就需要给系统“标称”响应定义一个参考基准。系统设计人员应当根据系统组件数据表提供的有关制造规范建立一个标称响应的标准。

总时序预算

首先介绍一些涵盖关于超频概念的新术语。总时序预算(TTB)与超频系统的稳定性条件密切相关。总时序预算是指系统能够实现的性能。根据这个定义,我们可以明确理性条件下系统的边界时序性能限定。总时序预算是指系统的整体边界性能极限条件下的,既包括超频和降频时的体验效果。我们往往要通过实践分析来获得总时序预算参数,数据表中的内容不能提供这种最大和最小容限规范。根据定义,数据表提供的是系统“标称”的时钟速度(位于最大和最小指标之间),是构成整体系统的设备选择的内在特性。在分析系统总时序预算的时候,会发现标称数值与总时序预算数值之间存在一定的性能差或者频率差。系统电压与温度都会影响总时序预算,为了获得一致性的结果,必须考虑这些影响因素。

始终裕度

时钟裕度(clock margining)也是一个有趣的术语。其含义包含的不仅仅是超频的概念。时钟裕度的概念是指我们通过全面的回归测试、根据总时序预算数据来探索并得出系统的稳定性参数。通过时钟裕度,让小部分软件超频运行,能全面了解系统的工作性能极限。可在产品寿命周期中隔一定时期就进行一次时钟裕度检测,了解实际性能与标称性能的差别,从而了解产品性能变化的趋势。这种趋势有助于估计系统什么时候会达到寿命终点。系统制造后不久,会进行一次参照时钟裕度性能差检测,这通常可建立起一个极限性能基准。随着产品的老化,在实际的测试中首次极限性能与标称的差距最大,以后每次检测都会发现差距在缩小。 [p]

系统老化

系统老化这是一个老生常谈的问题了,也是一个有趣的问题。世界上没有完美的产品,硅芯片制造也一样。硅芯片的封装会对产品使用寿命产生很大影响,因为封装技术密封性不好,硅芯片会暴露于外界环境。从硅芯片的角度来说,热载流子注入的自然效应与电子移动的细微效果会对系统产生影响。热量会加速硅芯片的老化。老化作为一种灵敏度参数来说,则体现在总时序预算数据上。通过超频与降频对比,发现超频对系统产生的压力最大,这也是性能差分析的基本方法。

时钟裕度的实施

上面谈论了这么多关于时钟裕度技术的话题,那么怎样才能实施时钟裕度技术呢?首先,我们要知道,最先进的系统通常包括众多时钟源。在多数情况下,时钟间存在相互依赖的关系,但有时也会存在独立的时钟。现在,常见的时钟源通常采用锁相环技术,确保噪声最小化,这使得新一代锁相环技术产生的时钟源具有较小的抖动,同时在相位噪声性能方面优于固定的时钟源。锁相环通常作为带可编程分压器的时钟合成器,可支持多种时钟输出的合成,而且相互依赖的不同时钟之间可建立不同的“分频比”。分频比是PC时钟领域的过时术语,但对任何相互依赖的时钟问题来说仍然适用。

为了成功实现时钟裕度功能,其必须内置频率调节的功能。变频功能在实际上可能比最初设想的要更困难,因为我们必须全面了解锁相环技术的性能,不仅要了解工作期间可以实现的目标频率,还要了解不同反馈编程条件下的相位噪声与抖动性能。基于时域的抖动是我们需要了解的重要内容,这样才能确保不同频率之间的一致性(不能突然断开),否则系统的稳定性分析就会出错。如果发生了不连续的抖动情况,也不会出现太大麻烦,可以通过多个特定的输出频率开槽或所需的分频比来解决。此外,应当确保开槽不要在频率变化期间进行,除非锁相环的设置在CPU对任何形式的开槽和短脉冲不敏感的间隔中进行。

确保总时序预算正确的技巧就是,应当了解哪些频率范围表现较好,这样就能小心地通过逐步逼近的办法接近总时序预算目标,而每一步的变化量可能有差别。如果频率变化较大,那么通常会导致总时序预算差别结果较小。总时序预算边界检测要求最终肯定要突破系统的界限,然后重启并略微后退一些,直至获得满意的一致性阈值为止。有许多没有文件记载的“小窍门”可以完成此项工作。建立系统总时序预算的关键就是一致性与可重复性。

正如前面简单谈到的那样,执行时钟裕度工作所发现的最重要信息就是在产品投入使用后估算出实际的产品使用寿命终结时间。本文分析的目的就是要通过时钟裕度来计算产品的标称性能与总时序预算之间的差异,以备后续之需。在几周、几个月乃至几年的时间里,投入实际使用的产品运行相同的回归进程,重复计算性能差异。我认为,能够体现产品使用寿命结束的情况就是在性能差为零或为负值。这并不是说系统出现故障,而只是说没有性能差了,说明产品已经到了使用寿命的终点。无论采用何种产品支持方式,如果性能差为零,则说明产品的使用寿命已经结束了,这一信息对那些需要全天候持续工作的系统来说是至关重要的。如图1所示,根据历史性能差信息预测出了性能差为零的时间。通过简单的线性分析或非线性曲线分析,可以估计得出产品使用寿命结束的时间。

图 1:系统使用寿命估算分析图。

[p]

在温度与电压等外部因素已知、记录且匹配的情况下进行未来回归检测,确保符合时钟裕度技术的准确性。图1显示了超频工作情况下的时钟裕度性能差为正值的变化图,此原理也适用于降频工作的情况。不过,在降频工作情况下,性能差的变动不会太大且基本保持稳定。这里将降频工作情况下的时钟裕度差值设为正值。

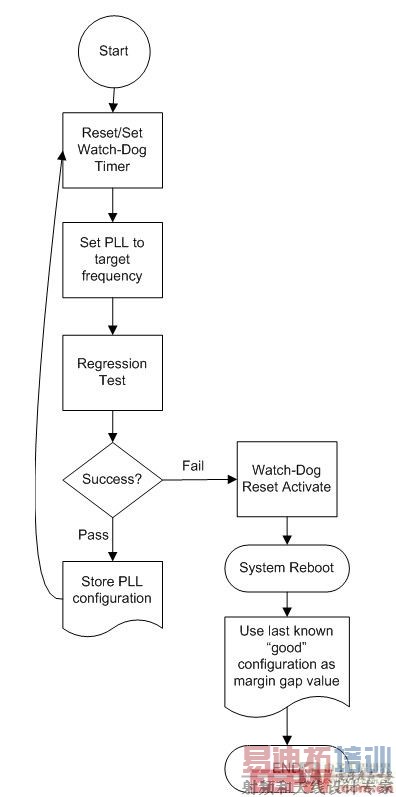

在时钟裕度技术的实施过程中,通过不断调整来修正锁相环时钟源或其他时钟源。图2显示了一个采用时钟裕度技术的简单的锁相环进程的一级方案。管理系统的最佳方法之一,就是采用看门狗计时器,成功完成回归检测后,软件就会重新设置计时器,而系统故障则会导致看门狗计时器超时。反复进行上述工作,重复检测回归计算,存储锁相环频率内容,进程不断重复进行直到出现故障。如前所述,不断趋近总时序预算极限的过程中,可以了解锁相环参数与系统步进变化大小的灵敏度,越接近总时序预算标准极限,步进改变就越小。这样,就要多次循环上述工作,直到取到最后一次成功检测参数为止,超过这个回归检测界限,系统就会出故障。因此最后一个已知的成功回归检测结果就是总时序预算的极限。

图 2:采用时钟裕度技术的简单的锁相环进程。

本文小结

测试时钟裕度性能差的过程,也就是了解总时序预算极限的过程,对了解如何发掘系统的全部潜力很有用。时钟裕度技术有助于找到系统最薄弱的环节,还能不断调节并创建一个匹配的系统,以防止系统超过总时序预算极限发生灾难性后果。总时序预算可以帮助我们明确时钟裕度性能差,估算出产品投入使用后的使用寿命。为了实现上述功能,时钟裕度技术的核心就是可编程的锁相环。通过参考PLL环路编程进程的有关讨论,验证了使用硬件计时器与非易失性存储设备有助于简化管理工作,明确总时序预算极限。